# LOW DIELECTRIC CONSTANT-BASED ORGANIC FIELD-EFFECT TRANSISTORS AND METAL-INSULATOR-SEMICONDUCTOR CAPACITORS

A Dissertation presented to the Faculty of the Graduate School University of Missouri

In Partial Fulfillment

Of the Requirements for the Degree

**Doctor of Philosophy**

# by NDUBUISI BENJAMIN UKAH

Dr. Suchi Guha, Dissertation Supervisor

DECEMBER 2012

The undersigned, appointed by the Dean of Graduate School, have examined the dissertation entitled

# LOW DIEJECTRIC CONSTANT-BASED ORGANIC FIELD-EFFECT TRANSISTORS

| AND METAL-INSULATOR-SEMICONDUCTOR CAPACITORS                         |

|----------------------------------------------------------------------|

| Presented by Ndubuisi Benjamin Ukah                                  |

| A candidate for the degree of Doctor of Philosophy                   |

| And hereby certify that in their opinion it is worthy of acceptance. |

|                                                                      |

|                                                                      |

| Dr. Suchi Guha                                                       |

|                                                                      |

| Dr. Carsten Ullrich                                                  |

|                                                                      |

| Dr. Gavin King                                                       |

|                                                                      |

| Dr. Ping Yu                                                          |

|                                                                      |

| Dr. Naz Islam                                                        |

#### **DEDICATION**

I cannot exhaust my many thanks to my loving wife, pillar of support, and costrategist – Ahunna, who having traveled this extraordinary road before me, stood by me every step of the way. I also express my indebtedness and gratitude to my loving parents, sister, and brothers for their support, encouragement, sacrifice, and prayers throughout my graduate degree journey. I pray for the blessings of Almighty God on them, friends and well-wishers.

Last, I will never forget the support and prayers of my American family - Mr. & Mrs. Tom Carter, who drove me down to Columbia in August of 2009 and ensured that I settled in on day one. My debt to them is without measure.

#### **ACKNOWLEDGEMENTS**

I would like to express my sincere gratitude to my supervisor - Dr. Suchi Guha for taking a chance on me and for her all-round support and guidance throughout the period. I strongly doubt if this day would have been possible without her help and uncommon co-operation.

I am greatly thankful to Dr. Jimmy Granstrom for his invaluable inputs toward the take-off and success of my research work. My special thanks also go to our research collaborators – Dr. Kartik Ghosh, Dr. Ram Gupta, Dr. Gavin King, and his student – Raghu for all their cherished assistances. I remain grateful to Dr. Ping Yu and Dr. Naz Islam for their time and useful inputs.

My immeasurable gratitude goes to Dr. Carsten Ullrich, who for his infectious empathy never left one on ones own and who time and again, never hesitated to go out of his way to offer critical assurances, help, and solutions to ones sometimes not-so-easy problems. I also appreciate the wonderful support of my group members especially Danish, who was ever-ready to assist and share useful information.

### **TABLE OF CONTENTS**

| AC  | KNOWL    | EDGEM   | IENTS                                            | ii  |

|-----|----------|---------|--------------------------------------------------|-----|

| LIS | T OF TA  | BLES    |                                                  | vi  |

| LIS | T OF FIG | SURES.  |                                                  | vii |

| AB  | STRACT   |         |                                                  | xi  |

| СН  | APTER    | •••••   |                                                  |     |

| 1   | INTRO    | DUCTIO  | ON                                               | 1   |

| 2   | WORK     | (ING PR | SINCIPLES OF MIS DIODES                          | 4   |

|     | 2.1      | MIS C   | apacitance                                       | 4   |

|     | 2.2      | Charge  | es and Potentials                                | 8   |

|     | 2.3      | Interfa | ace Trap States                                  | 11  |

|     | 2.4      | OFET I  | Electrical Characteristics                       | 17  |

|     | 2.5      | Organ   | ic Materials                                     | 22  |

|     |          | 2.5.1   | Polymer Dielectrics                              | 22  |

|     |          | 2.5.2   | Organic semiconductors                           | 24  |

| 3   | EXPER    | IMENT   | AL TECHNIQUES                                    | 26  |

|     | 3.1      | Film D  | eposition                                        | 26  |

|     |          | 3.1.1   | Spincoating                                      | 26  |

|     |          | 3.1.2   | Matrix-assisted pulsed-laser evaporation (MAPLE) | 27  |

|     |          | 3.1.3   | Thermal evaporation                              | 30  |

|     | 3.2      | Experi  | mental details                                   | 32  |

|   |      | 3.2.1  | Device Structures and Fabrication                                                                                    | 32 |

|---|------|--------|----------------------------------------------------------------------------------------------------------------------|----|

|   | 3.3  | Device | e characterizations                                                                                                  | 36 |

|   |      | 3.3.1  | Atomic force microscopy                                                                                              | 36 |

|   |      | 3.3.2  | MIS capacitance-voltage measurement                                                                                  | 38 |

|   |      | 3.3.3  | OFET current-voltage measurement                                                                                     | 39 |

| 4 | INSU | LATOR- | ILMS FOR ORGANIC FIELD-EFFECT TRANSISTORS AND METALSEMICONDUCTOR CAPACITORS WITH POLY (METHYL LATE) GATE DIELECTRICS | 40 |

|   | 4.1  | Introd | luction                                                                                                              | 40 |

|   | 4.2  | Result | ts and Discussion                                                                                                    | 42 |

|   |      | 4.2.1  | Dielectric Film: Morphology and Electrical Characteristics                                                           | 42 |

|   |      | 4.2.2  | MIS Diode Characteristics                                                                                            | 44 |

|   |      | 4.2.3  | OFET Characteristics                                                                                                 | 52 |

|   | 4.3  | Concl  | usions                                                                                                               | 57 |

| 5 | SEM  | IICOND | FIELD-EFFECT TRANSISTORS AND METAL-INSULATOR-<br>UCTOR CAPACITORS WITH POLY (METHYL METHACRYLATE) G                  |    |

|   | 5.1  | Introd | luction                                                                                                              | 58 |

|   | 5.2  | Result | ts and Discussion                                                                                                    | 60 |

|   |      | 5.2.1  | Morphology and Structure of the Dielectric Films                                                                     | 60 |

|   |      | 5.2.2  | MIS Diode Characteristics                                                                                            | 61 |

|   |      | 5.2.3  | OFET Characteristics                                                                                                 | 64 |

|   | 5.3  | Concl  | usion                                                                                                                | 69 |

| 6 |      |        | TING VOLTAGE AND STABLE PENTACENE FIELD-EFFECT TRANS -K POLY (4-VINYL PHENOL) POLYMER GATE DIELECTRICS               |    |

|     | 6.1            | Introd | uction                                                    | 71  |  |

|-----|----------------|--------|-----------------------------------------------------------|-----|--|

|     | 6.2            | Experi | mental details                                            | 73  |  |

|     | 6.3            | Result | s and discussion                                          | 75  |  |

|     |                | 6.3.1  | Morphology of the dielectric films                        | 75  |  |

|     |                | 6.3.2  | Surface energy and contact angles of the dielectric films | 76  |  |

|     |                | 6.3.3  | MIS diode characteristics                                 | 76  |  |

|     |                | 6.3.4  | FET characteristics                                       | 80  |  |

|     | 6.4            | OFETs  | and MIS Diodes with DMSO-dissolved PVP layer              | 92  |  |

|     | 6.5            | Hybrid | Bilayer Devices                                           | 94  |  |

|     | 6.6            | Conclu | usion                                                     | 98  |  |

| 7   | CONCI          | UDING  | REMARKS AND FUTURE DIRECTION                              | 101 |  |

| REF | ERENCI         | ES     |                                                           | 106 |  |

| VIT | A              | •••••  |                                                           | 113 |  |

| PUE | JBLICATIONS114 |        |                                                           |     |  |

## **LIST OF TABLES**

| Table |                                                                                                                                                                                                 | Page |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1   | Various solvents used in this work and their properties                                                                                                                                         | 23   |

| 4.1   | Field-effect mobilities in saturation regime, threshold voltages, root mean square values, density of interface state at flat band ( $D_{it}$ ), and solubility parameters for various solvents | 56   |

| 5.1   | Summary of electrical characteristics of PMMA (with PC) and PMMA-BTAc OFETs                                                                                                                     | 65   |

| 6.1   | Summary of performance parameters of OFETs after 10 days of air exposure                                                                                                                        | 86   |

| 6.2   | Summary of performance parameters of (a) PVP/SiO <sub>2</sub> (50 nm), (b) PVP/SiO <sub>2</sub> (100 nm), (c) PVP/SiO <sub>2</sub> (200 nm), and SiO <sub>2</sub> (200 nm) OFETs.               | 99   |

## **LIST OF FIGURES**

| Figure | P                                                                                                                                                                       | age  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

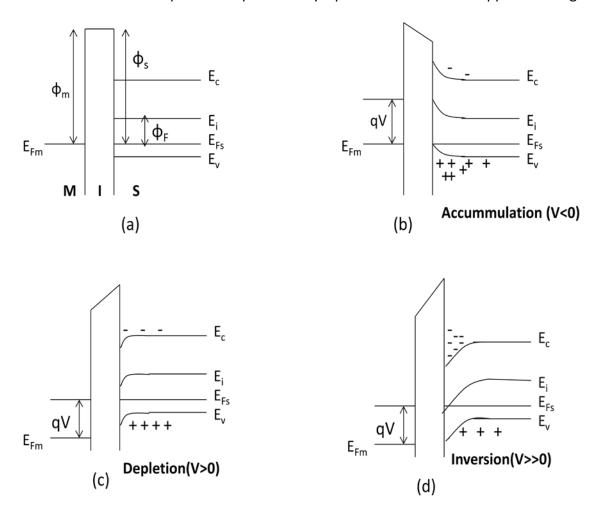

| 2.1    | Energy band diagrams for an ideal p-type MIS device under (a) flat band (b) accumulation (c) depletion and (d) inversion conditions                                     | 5    |

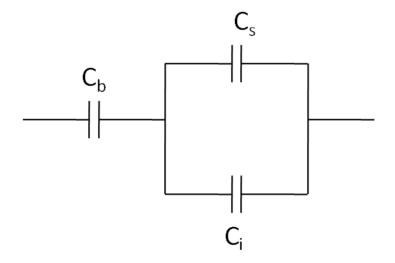

| 2.2    | Equivalent circuit of a MIS structure                                                                                                                                   | 7    |

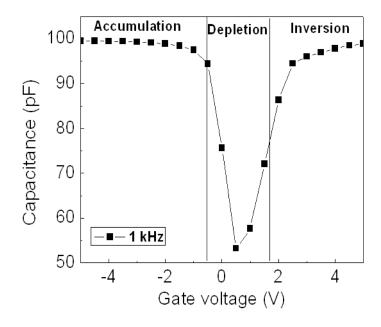

| 2.3    | Capacitance-voltage characteristics for a typical Si-based MIS capacitor indicating the accumulation, depletion, and inversion regions                                  | 7    |

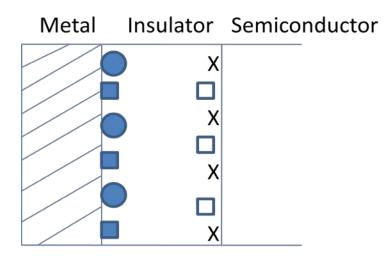

| 2.4    | Different types of charges occurring in a typical Si-based MIS structure                                                                                                | 8    |

| 2.5    | Charge distribution in a MIS structure                                                                                                                                  | 9    |

| 2.6    | Energy band diagram of the MIS structure                                                                                                                                | 9    |

| 2.7    | Plot of $G_p/\omega$ as a function of log (f) for various gate biases in the depletion region                                                                           | . 14 |

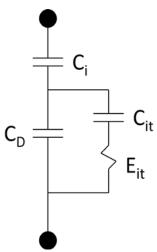

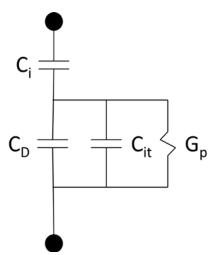

| 2.8    | Schematics of (a) equivalent (b) simplified and (c) measured circuits for MIS structures with interface traps                                                           | . 14 |

| 2.9    | Schematic of equivalent circuit for an STC model                                                                                                                        | . 16 |

| 2.10   | Schematic of equivalent circuit for the continuum of states model                                                                                                       | . 17 |

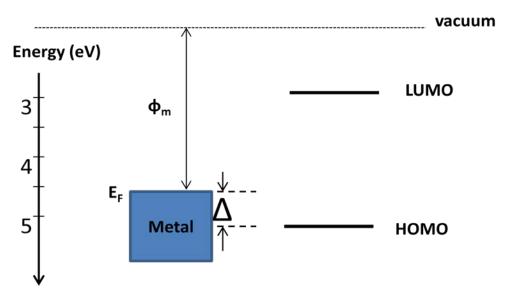

| 2.11   | Energy band diagram alignment at a metal-organic semiconductor interface                                                                                                | . 18 |

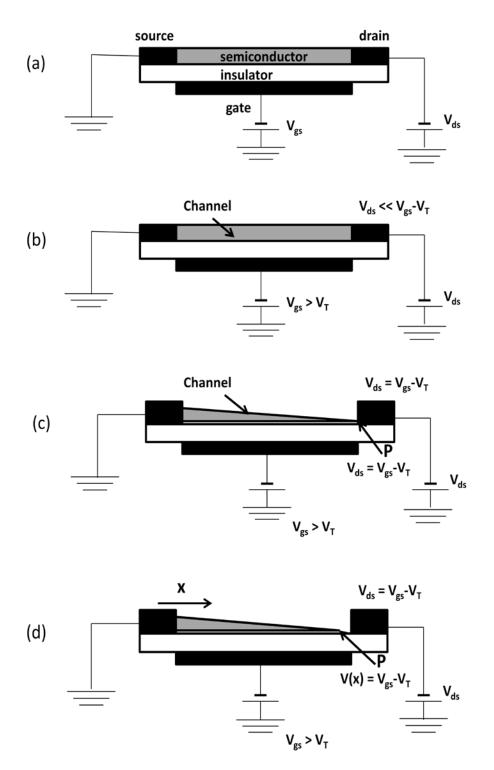

| 2.12   | (a) Schematic of an organic field-effect transistor. Illustrations of (b) linear (c) start of saturation and (d) saturation regimes of organic field-effect transistors | . 19 |

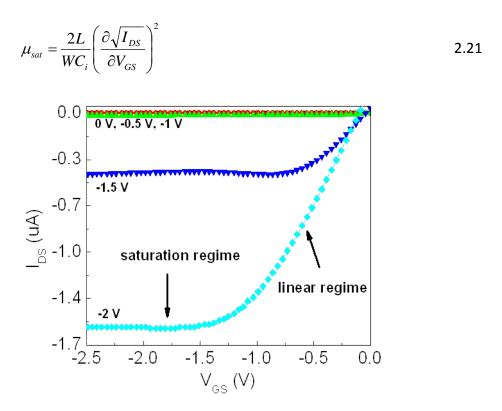

| 2.13 | and saturation regimes                                                                                                                                                                                                 | 21 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.14 | Transfer characteristics for a typical OFET indicating $V_T$ and $SS$                                                                                                                                                  | 22 |

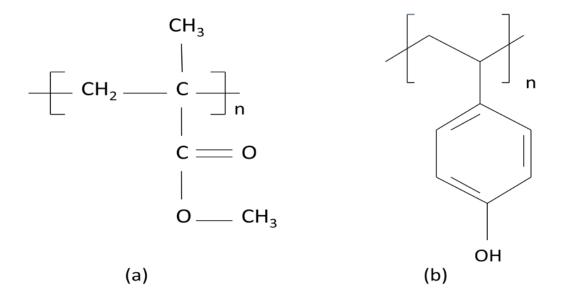

| 2.15 | Molecular structure of (a) PMMA and (b) PVP                                                                                                                                                                            | 23 |

| 2.16 | Molecular structure of pentacene                                                                                                                                                                                       | 24 |

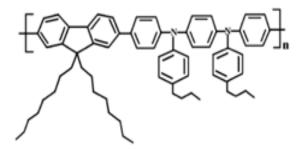

| 2.17 | Molecular structure of PFB                                                                                                                                                                                             | 25 |

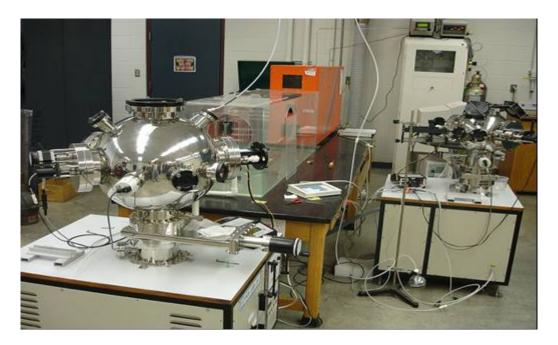

| 3.1  | The MAPLE system at Missouri State University in Springfield, Missouri                                                                                                                                                 | 28 |

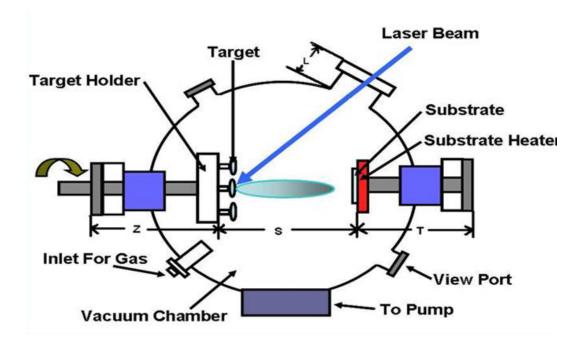

| 3.2  | Schematic diagram of the MAPLE system                                                                                                                                                                                  | 29 |

| 3.3  | Schematic of thermal evaporating system                                                                                                                                                                                | 31 |

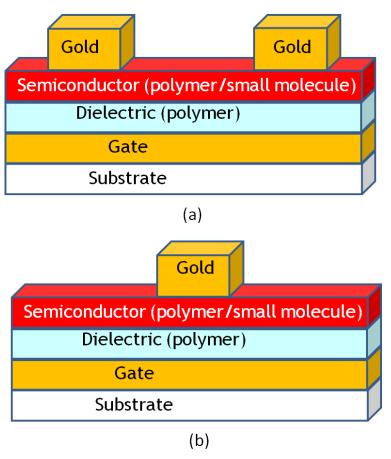

| 3.4  | Schematic representations of our (a) OFET and (b) MIS diode structures                                                                                                                                                 | 32 |

| 3.5  | MBraun glove box system with thermal evaporator in box 1 (left)                                                                                                                                                        | 34 |

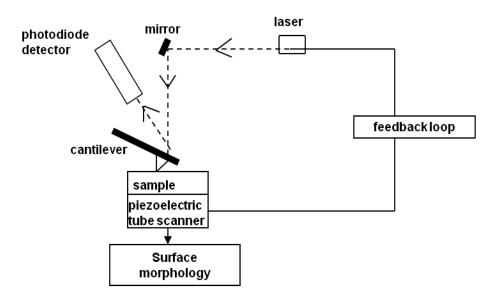

| 3.6  | Schematic representation of the working principle of the atomic force microscope                                                                                                                                       | 37 |

| 3.7  | A sketch of a C-V measurement set-up                                                                                                                                                                                   | 38 |

| 3.8  | A sketch of OFET I-V measurement set-up                                                                                                                                                                                | 39 |

| 4.1  | Atomic force micrographs of PMMA films prepared in different solvents                                                                                                                                                  | 43 |

| 4.2  | Current density–electric density characterization for PMMA dielectric film dissolved in butylacetate, toluene, and anisole                                                                                             | 44 |

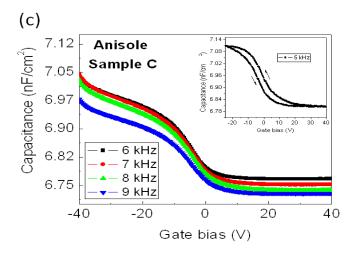

| 4.3  | C-V characteristics between 6–9 kHz for Al/PMMA/PFB/Au structure and C-V characteristics of Al/PMMA/PFB/Au MIS diodes at 5 kHz (insets) for (a) butylacetate (Sample A), (b) toluene (Sample B) and anisole (Sample C) | 45 |

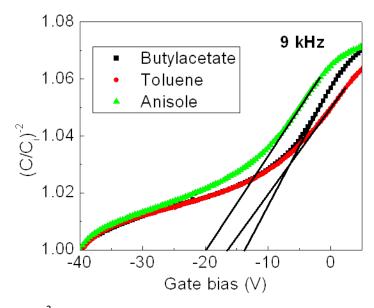

| 4.4  | Plot of $(C/C_i)^{-2}$ vs. gate bias $(V)$ for Samples A, B, and C                                                                                                                                                     | 46 |

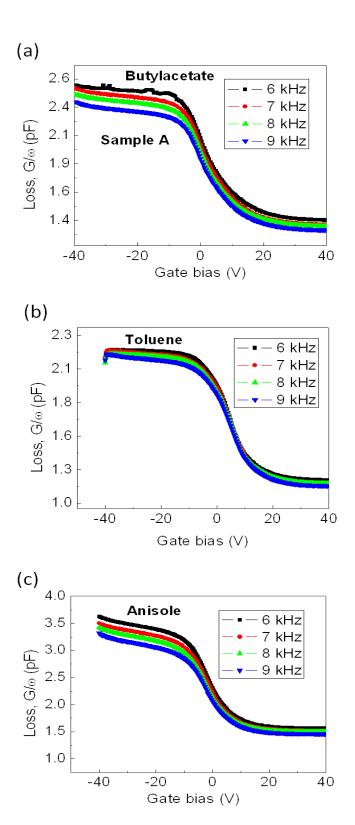

| 4.5  | Frequency dependence of loss (conductance/angular frequency) vs. gate bias for MIS diodes: (a) Sample A, (b) Sample B, and (c) Sample C                                                                                | 49 |

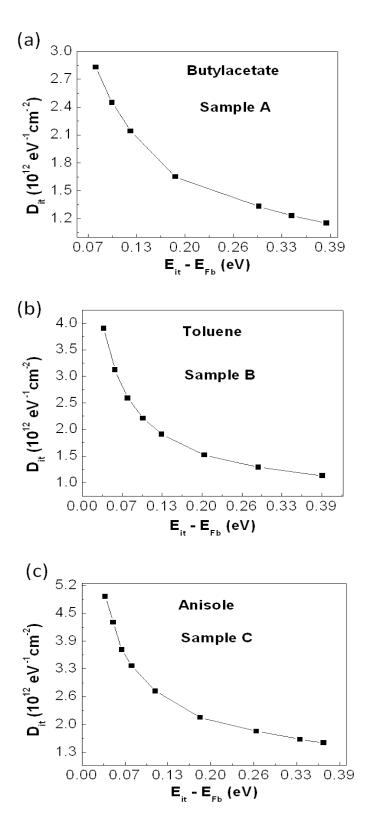

| 4.6  | Plot of D <sub>it</sub> as a function of energy above bulk Fermi level,                                                                                                                                                |    |

|     | E <sub>it</sub> – E <sub>Fb</sub> for Sample A, Sample B, and Sample C                                                                                                                                      | . 51 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

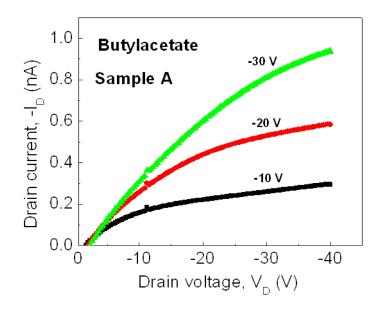

| 4.7 | Representative electrical output characteristics of the FETs from various solvents                                                                                                                          | . 53 |

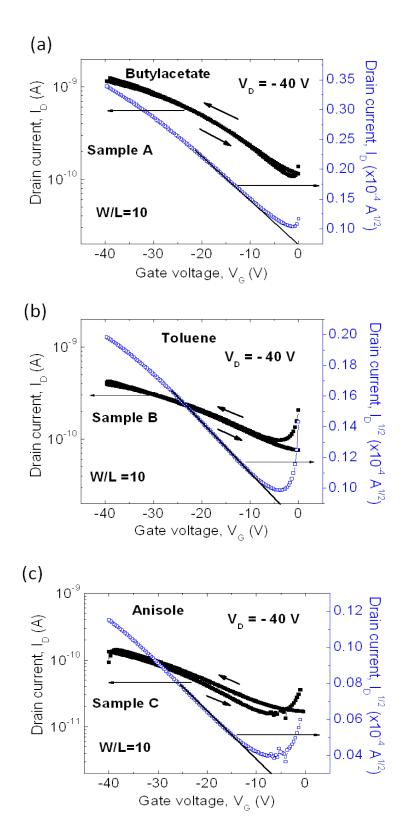

| 4.8 | Electrical transfer characteristics of OFETs from various solvents: (a) butylacetate (Sample A), (b) toluene (Sample B), and (c) Sample C                                                                   | . 55 |

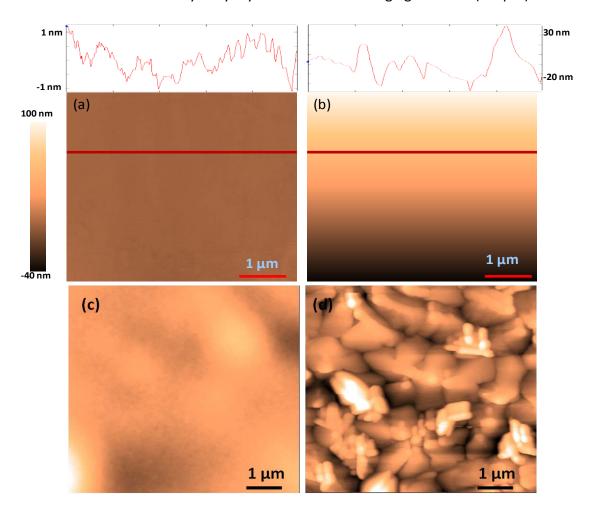

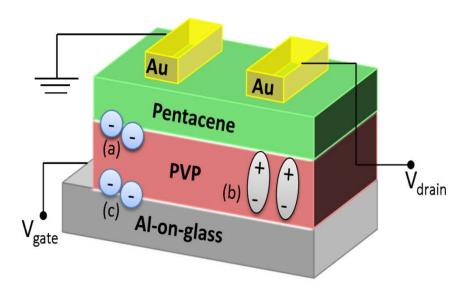

| 5.1 | Atomic force microscopy images of (a) PMMA-PC (b) pentacene on PMMA-PC (c) PMMA-BTAc and (d) pentacene on PMMA-BTAc                                                                                         | . 60 |

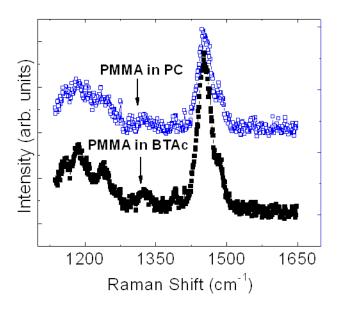

| 5.2 | Raman spectra of PMMA-BTAc and PMMA-PC dielectric films                                                                                                                                                     | . 61 |

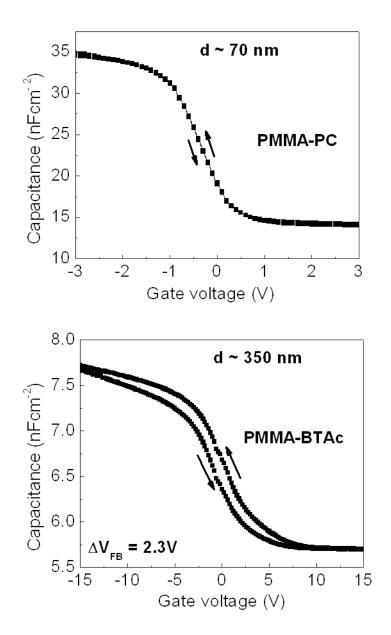

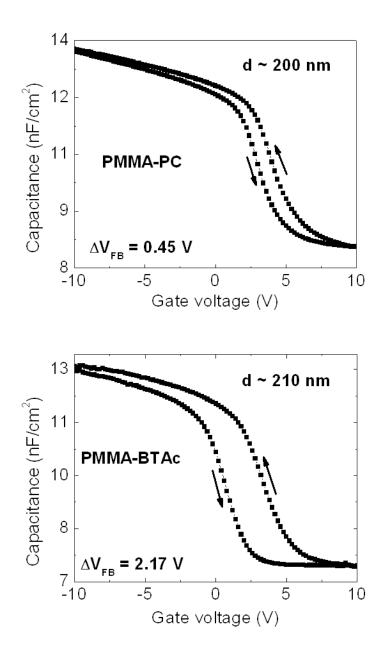

| 5.3 | C-V curves of Al/PMMA-PC/Pentacene/Au and Al/PMMA-PC/Pentacene/Au MIS diodes at a frequency of 5 kHz                                                                                                        | . 62 |

| 5.4 | C-V curves of Al/PMMA-PC/Pentacene/Au and Al/PMMA-PC/Pentacene/Au MIS diodes at a frequency of 5 kHz                                                                                                        | . 63 |

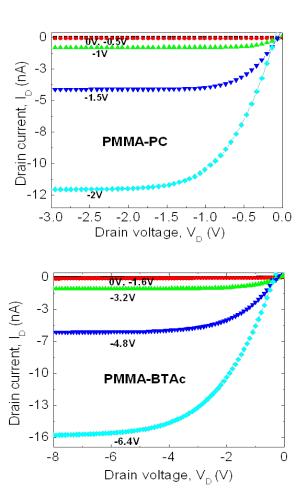

| 5.5 | Output characteristics for out OFETs                                                                                                                                                                        | . 65 |

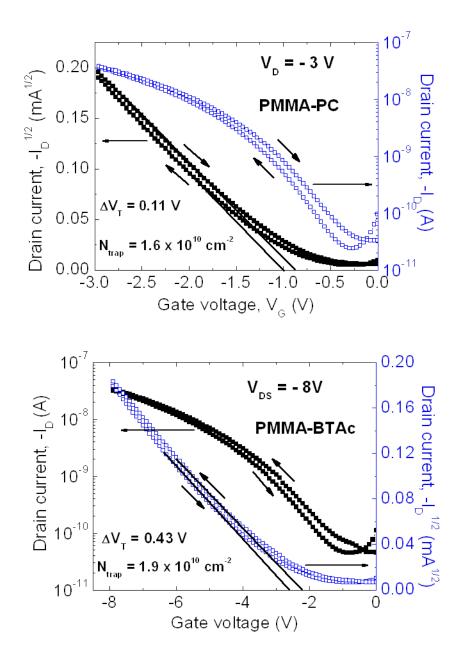

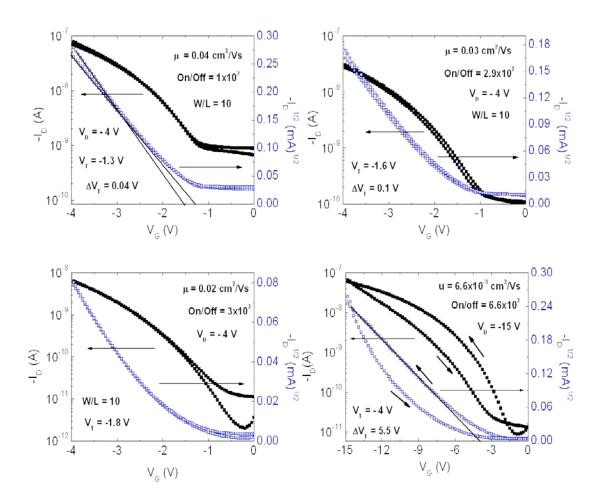

| 5.6 | Transfer characteristics for out OFETs                                                                                                                                                                      | . 66 |

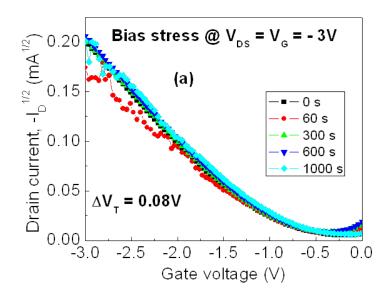

| 5.7 | Operational stability of OFET transfer characteristics (a) after bias stress at $V_G = V_D = -3 V$ at varying stress times (b) Repetitive forward testing at $V_D = -3 V$                                   | . 68 |

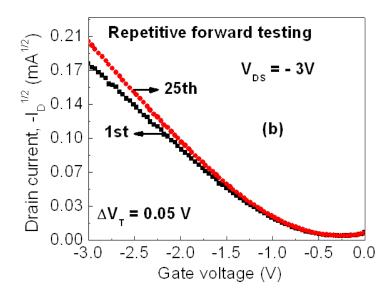

| 6.1 | Schematic cross-sectional view of OFET showing the various sources of instability arising from (a) semiconductor-insulator interface charges (b) slowly-polarizing dipole charges (c) gate-injected charges | . 74 |

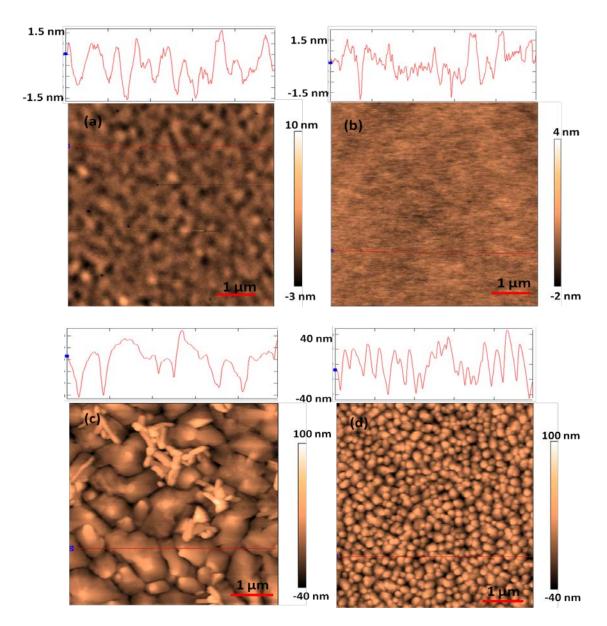

| 6.2 | Atomic force microscopy images of (a) PVP (b) c-PVP (c) pentacene on PVP and (d) pentacene on c-PVP dielectric films                                                                                        | . 75 |

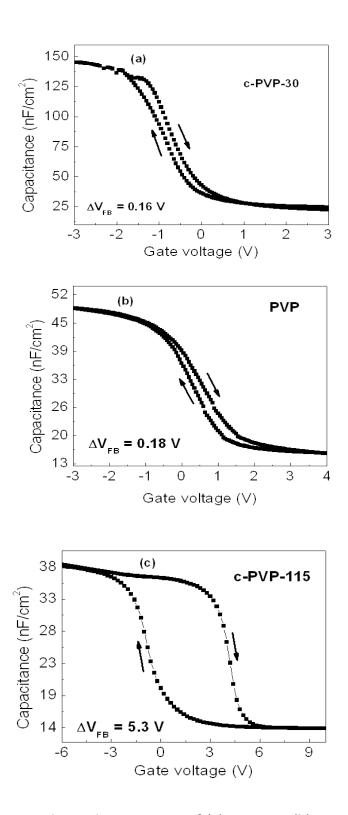

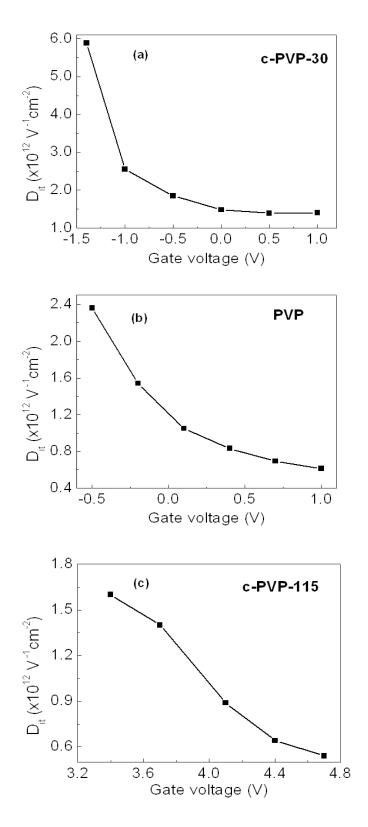

| 6.3 | Capacitance-voltage characteristics of (a) c-PVP-30 (b) PVP and (c) c-PVP-115 MIS diodes at 5 kHz                                                                                                           | . 77 |

| 6.4 | Capacitance-voltage characteristics of (a) c-PVP-30 (b) PVP and (c) c-PVP-115 MIS diodes at 5 kHz                                                                                                           | . 79 |

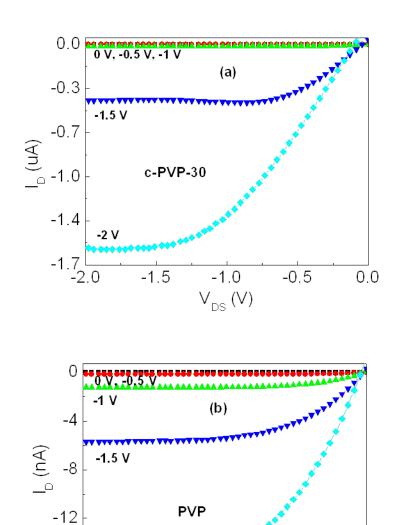

| 6.5 | Output characteristics of (a) c-PVP-30 and (b) PVP OFETs                                                                                                                                                    | . 81 |

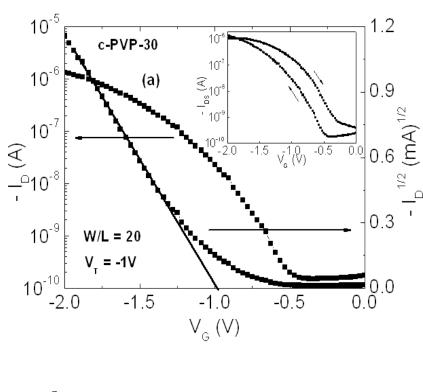

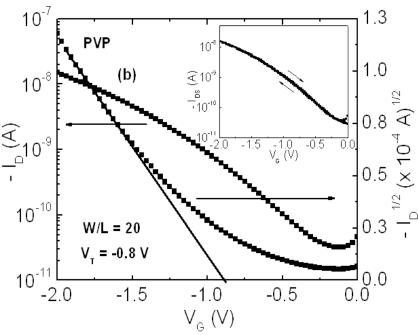

| 6.6 | Transfer characteristics of (a) c-PVP-30 and (b) PVP OFETs. Insets: Forward and backward sweeps of transfer characteristics                                                                                 | . 82 |

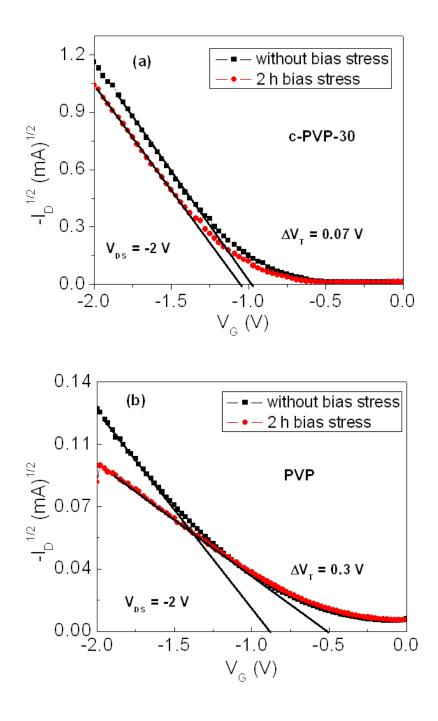

| 6.7  | Bias stressing and measurements were carried out under ambient conditions                                                                                                                 | 84 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

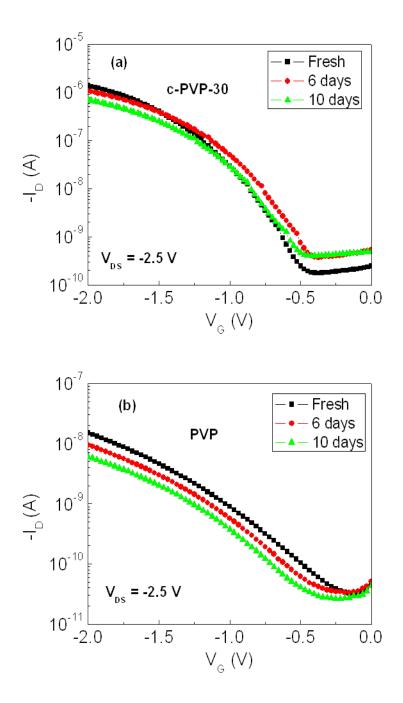

| 6.8  | Transfer characteristics of OFETs over a 10-day period of air exposure (c) and (d)                                                                                                        | 85 |

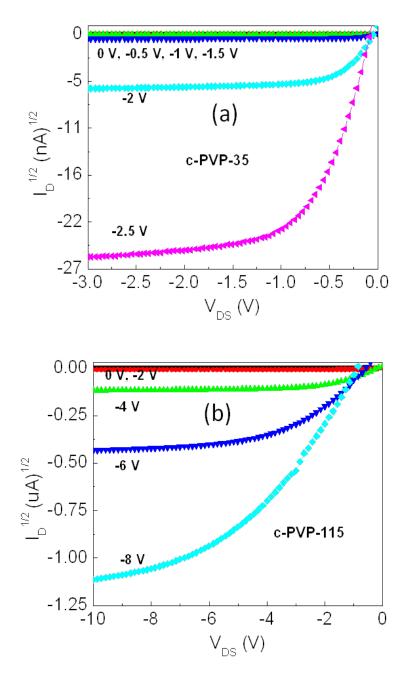

| 6.9  | Output characteristics of (a) c-PVP-35 and (b) c-PVP-115 OFETs                                                                                                                            | 87 |

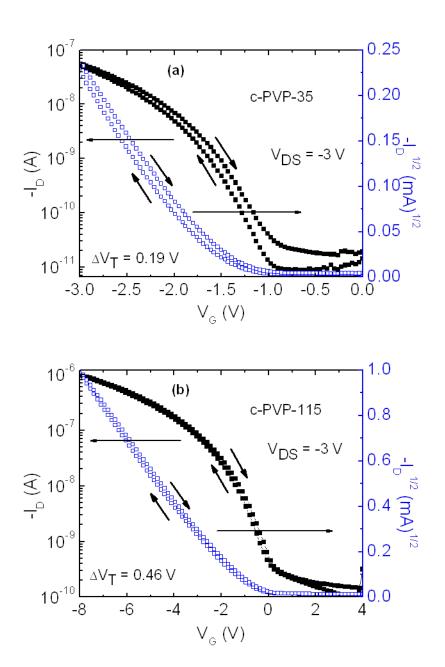

| 6.10 | Transfer characteristics of (a) c-PVP-35 and (b) c-PVP-115 OFETs                                                                                                                          | 88 |

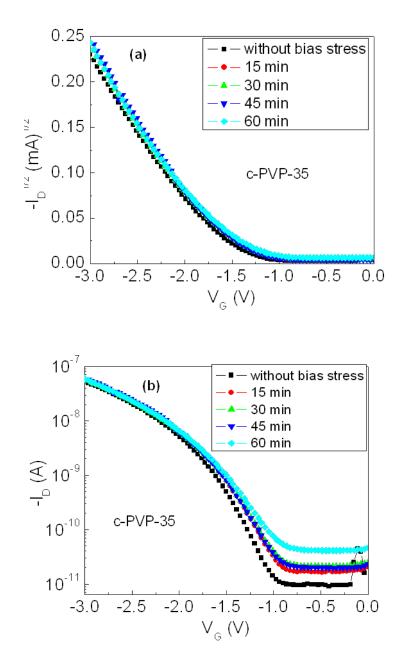

| 6.11 | Operational stability of transfer characteristics of (a) c-PVP-35 OFET and (b) c-PVP-115 OFET after bias stress at $V_G = V_{DS} = -3 \text{ V}$ at varying stress times                  | 90 |

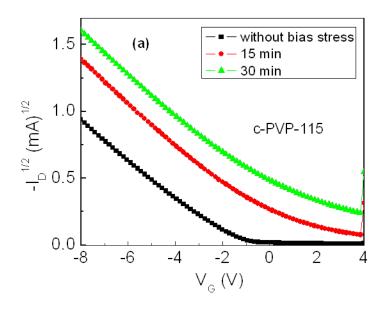

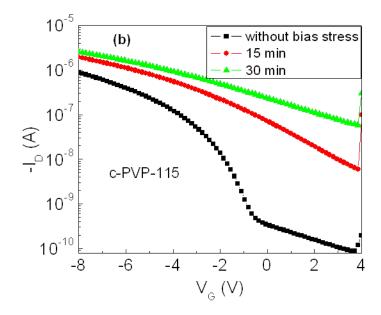

| 6.12 | Operational instability of transfer characteristics of (a) c-PVP-35 OFET and (b) c-PVP-115 OFET after bias stress at $V_G = V_{DS} = -8 \text{ V}$ , respectively at varying stress times | 91 |

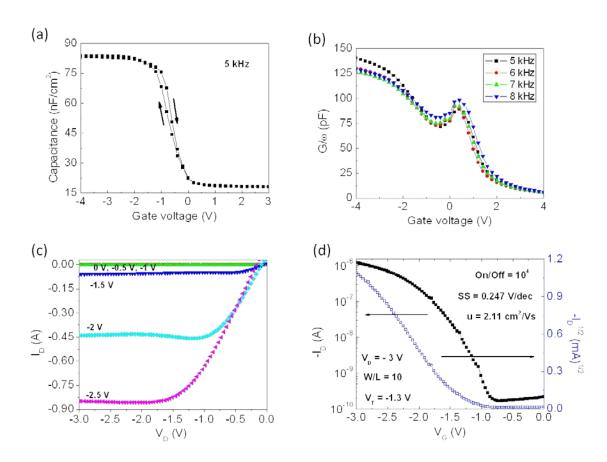

| 6.13 | (a) C-V characteristics of MIS diode at 5 kHz (b) G-V curves of MIS diode (c) Output and (d) Transfer characteristics of OFET                                                             | 93 |

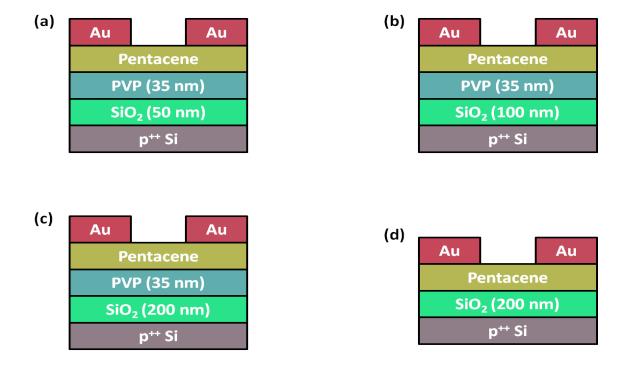

| 6.14 | Schematic cross-sectional view of OFETs                                                                                                                                                   | 94 |

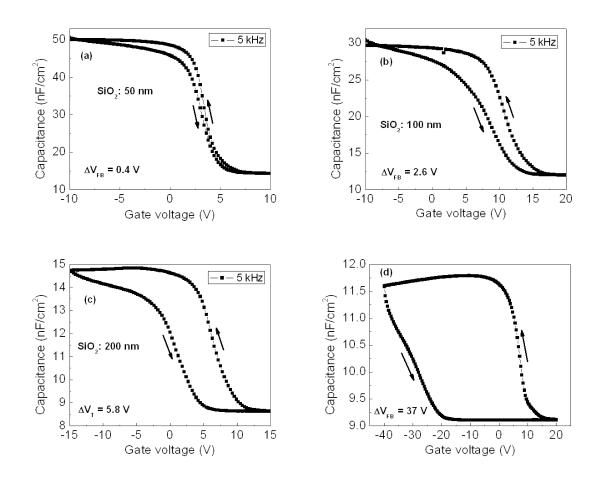

| 6.15 | Capacitance-voltage characteristics of (a) $PVP/SiO_2$ (50 nm) (b) $PVP/SiO_2$ (100 nm) (c) $PVP/SiO_2$ (200 nm) and (d) $SiO_2$ (200 nm) MIS diodes at 5 kHz                             | 95 |

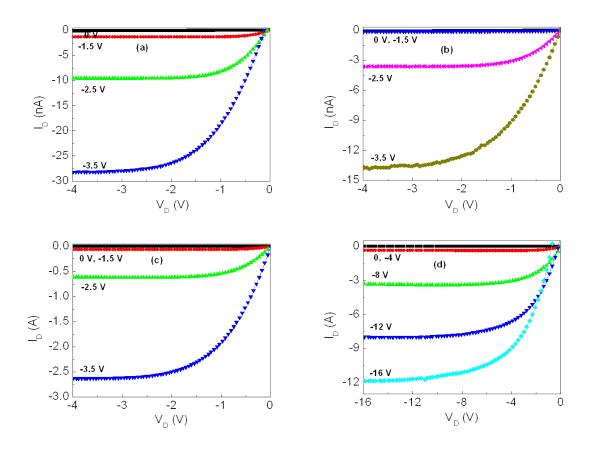

| 6.16 | Output characteristics of (a) PVP/SiO <sub>2</sub> (50 nm) (b) PVP/SiO <sub>2</sub> (100 nm) (c) PVP/SiO <sub>2</sub> (200 nm) and (d) SiO <sub>2</sub> (200 nm) OFETs                    | 97 |

| 6.17 | Transfer characteristics of (a) PVP/SiO <sub>2</sub> (50 nm) (b) PVP/SiO <sub>2</sub> (100 nm) (c) PVP/SiO <sub>2</sub> (200 nm) and (d) SiO <sub>2</sub> (200 nm) OFETs                  | 98 |

#### **ABSTRACT**

This thesis describes a study of PFB and pentacene-based organic field-effect transistors (OFET) and metal-insulator-semiconductor (MIS) capacitors with low dielectric constant (k) poly(methyl methacrylate) (PMMA), poly(4-vinyl phenol) (PVP) and cross-linked PVP (c-PVP) gate dielectrics. A physical method – matrix assisted pulsed laser evaporation (MAPLE) - of fabricating all-polymer field-effect transistors and MIS capacitors that circumvents inherent polymer dissolution and solvent-selectivity problems, is demonstrated. Pentacene-based OFETs incorporating PMMA and PVP gate dielectrics usually have high operating voltages related to the thickness of the dielectric layer. Reduced PMMA layer thickness (≤ 70 nm) was obtained by dissolving the PMMA in propylene carbonate (PC). The resulting pentacene-based transistors exhibited very low operating voltage (below -3 V), minimal hysteresis in their transfer characteristics, and decent electrical performance. Also low voltage (within -2 V) operation using thin (≤ 80 nm) low-k and hydrophilic PVP and c-PVP dielectric layers obtained via dissolution in high dipole moment and high-k solvents - PC and dimethyl sulfoxide (DMSO), is demonstrated to be a robust means of achieving improved electrical characteristics and high operational stability in OFETs incorporating PVP and c-PVP dielectrics.

#### **CHAPTER 1**

#### INTRODUCTION

Until recently, semiconductor optoelectronics research has been restricted to the conventional inorganic semiconducting materials. Owing to the discovery in 1977 of the first highly conductive polymer – polyacetylene, by A. J. Heeger, H. Shirakawa, and Alan G. MacDiamid (Nobel Prize in Chemistry in 2000), intense research efforts have been directed at organic semiconductors and devices resulting in the birth of organic electronics [1]. Organic electronics is basically electronic devices made using organic materials (organic dielectrics, conjugated and small molecule semiconductors). The existence of  $\pi$ -orbitals in organic materials is responsible for carrier transport and semiconducting properties in these materials. Typical organic electronics include organic field-effect transistors (OFETs), organic light-emitting diodes (OLEDs) and organic photovoltaics.

The interest and increased research activities in solution-processable organic devices are due to their promise in large-area electronics fabricated on flexible substrates using low-cost and unconventional means such as spincoating, low/room temperature printing, and roll-to-roll processing [2]. Interestingly, some of the best

OFETs have shown performances that compare favorably well with amorphous silicon thin film transistors [3]. However, considerable challenges still need to be addressed in order to reap the full benefits of organic electronics. Such challenges include the inherent problems of polymer dissolution and solvent-selectivity particularly encountered in the fabrication of all-polymer devices as well as the difficultly in fabricating stable and low-operating voltage OFETs owing to the low dielectric constants of conventional polymer dielectric materials. Contained in this work are facile strategies for overcoming these above-mentioned organic electronics problems.

This report begins with a discussion of the working principles of metal-insulator-semiconductor (MIS) structures (field-effect transistors and capacitors) in chapter 2. Chapter 2 also contains brief descriptions of the organic materials employed in this work. Chapter 3 contains an overview of thin film deposition techniques for organic devices, organic devices fabrication procedure, device structures as well as some concise descriptions of employed device characterization techniques. Chapter 4 begins the results chapters. It discusses the morphology and electrical characteristics of poly (methyl methacrylate) (PMMA) films and electrical characterization results of our all-polymer OFETs and MIS capacitors with matrix-assisted pulsed-laser evaporated polymer semiconducting layers. Chapter 5 contains discussions about the morphology of pentacene films and electrical characterizations of pentacene OFETs and diodes incorporating PMMA dielectric layers. It also demonstrates the feasibility of low-operating voltage pentacene OFETs based on single-layer PMMA polymer dielectric. Chapter 6 also discusses electrical characterizations and operational as well as

environmental stability of high-mobility and low-operating voltage pentacene OFETs based on single-layers of pristine poly (4-vinyl phenol) (PVP) and cross-linked PVP (c-PVP). Here, the use of thin PVP and c-PVP layers with consequent low-voltage operation is demonstrated to be a robust means of achieving stability in pentacene-based OFETs incorporating PVP and c-PVP dielectrics. The report ends with some concluding remarks and suggestions for future work in Chapter 7.

#### **CHAPTER 2**

#### **WORKING PRINCIPLES OF MIS DIODES**

#### 2.1 MIS Capacitance

An understanding of the working of the two-terminal MIS capacitor is critical for a proper understanding of the operations of the three-terminal MIS field-effect transistor (MISFET). Here, we will begin by defining some of the relevant terms.  $\varphi_m$  is the modified work function for the metal-insulator interface and it is the energy measured from the metal Fermi level to the conduction band of the insulator.  $\varphi_s$  is the modified work function at the semiconductor-insulator interface. In an idealized case,  $\varphi_m$  and  $\varphi_s$  are assumed to be equal, which means that there is no difference in the two work functions.  $\varphi_F$  is a measure of the position of the Fermi level below the intrinsic level of the semiconductor,  $E_i$ .

When the voltage across the ideal MIS structure is zero, flat-band conditions are at hand as shown in Fig. 2.1a. Assuming a p-type semiconductor, for a negative potential on the metal as shown in Fig. 2.1b, an effective negative charge is deposited on the metal and in response, an equal positive charge accumulates at the surface of the semiconductor giving rise to an accumulation of holes at the semiconductor-insulator

interface. The applied negative voltage results in the raising of the electron energies in the metal relative to the semiconductor; as a result, the Fermi level of the metal,  $E_{Fm}$  now lies above its equilibrium position by qV where V is the applied voltage.

Figure 2.1: Energy band diagrams for an ideal p-type MIS device under (a) flat band, (b) accumulation, (c) depletion and (d) inversion conditions.

The energy bands of the semiconductor are seen to bend near the interface in order to accommodate the accumulation of holes, causing  $E_i$  to move up in energy near the surface due to a non-variation of the Fermi level in the semiconductor.

An application of a positive voltage causes the deposition of positive charges on the metal which results in corresponding negative charges at the surface of the semiconductor. The negative charges are due to a depletion of holes from a region near the surface which leave behind uncompensated ionized acceptors. As can be seen from Fig. 2.1c, the bands bend down near the semiconductor surface due to the decrease in the hole concentration and consequent shift of E<sub>i</sub> closer to E<sub>F</sub>. An increase in the positive voltage results in further downward bending of the bands at the semiconductor surface and at large enough positive voltage, E<sub>i</sub> bends below E<sub>F</sub>. At this point, the region near the semiconductor surface has conduction properties much like that of an n-type material, which is formed not by doping but by inversion of the originally p-type semiconductor caused by the applied voltage. This inverted layer is highly critical to inorganic MIS capacitor and transistor operations.

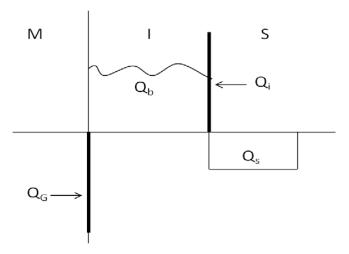

Three distinct capacitance components are distinguishable in a MIS structure (Fig. 2.3). Since charge storage results in capacitance, a charge exchange that take place between the semiconductor-insulator interface states and the energy bands in the semiconductor contributes a capacitance,  $C_i$  which is in parallel with the depletion capacitance of the semiconductor,  $C_s$ . This combination is in series with the insulator layer/bulk capacitance,  $C_b$  resulting in a total capacitance, C given by,

$$C = \frac{dQ_G}{dV_G} = \frac{C_b(C_i + C_s)}{C_b + (C_i + C_s)}$$

2.1

From Equation 2.1, it is obvious that C is voltage-dependent which could be helpful in acquiring information about charges and electron states in the insulator and at the

semiconductor-insulator interface. The MIS structure could be represented by an equivalent circuit as shown in Fig. 2.2.

Fig. 2.2: Equivalent circuit of a MIS structure.

Fig. 2.3: Capacitance-voltage characteristics for a typical Si-based MIS capacitor indicating the accumulation, depletion, and inversion regions.

#### 2.2 Charges and Potentials

The MIS structure is essentially a capacitor in which one of the plates is a semiconductor. There are four types of charge sources in a MIS structure: interface states, fixed interface charges, mobile ions, and impurity centers (Fig. 2.4) [4].

- X Interface trap charge

- Fixed oxide charge

- Oxide trapped charge

- Mobile ion

Fig. 2.4: Different types of charges occurring in a typical Si-based MIS structure.

The interface states are electron states at the interface between the insulator and semiconductor. Charge carriers can be captured and emitted at these states and they can also communicate with the energy bands of the semiconductor. The fixed interface charges cannot be filled or emptied from the semiconductor and have energy levels that

are often positioned outside the semiconductor band gap. The mobile ions move by diffusion or electric field drift in the insulator. The ionized impurity centers constitute deep-lying energy levels in the band gap of the insulator. As seen in Fig. 2.5, [4] there is a plane charge,  $Q_G$  at the metal-insulator interface. Fixed interface charges,

Fig. 2.5: Charge distribution in a MIS structure.

Fig. 2.6: Energy band diagram of the MIS structure.

mobile ions and ionized impurity centers form a volume charge,  $Q_b$ . At the insulator-semiconductor interface, a surface charge,  $Q_i$  is manifested by the interface states and in the space-charge region of the semiconductor, there exists a total charge,  $Q_s$ . Considering a p-type semiconductor, the band diagram of a MIS structure is as shown in Fig. 2.6 [4]. When the metal and the semiconductor are connected to external conductors involving a voltage source, a charge  $Q_G$  appears in the metal and it is related to the above-mentioned charges by,

$$Q_G + Q_b + Q_i + Q_S = 0$$

2.2

These charges will give rise to a voltage drop  $V_1$  across the insulator with a distribution of charges depicted in Fig. 2.6.

$$V_1 = -\frac{Q_b}{C_i} \qquad , 2.3$$

where  $C_i$  is the insulator capacitance per unit area. A second potential,  $V_2$  from the interface charge,  $Q_i$  and the charge in the semiconductor,  $Q_s$  is given by,

$$V_2 = -\frac{Q_s + Q_i}{C_i}$$

2.4

The total insulator potential,  $V_i$  is given by,

$$V_i = V_1 + V_2 = -\frac{Q_s + Q_i + Q_b}{C_i}$$

2.5

For different values of  $\phi_m$  and  $\phi_s$ , a potential  $\phi_{ms}$  ( $\phi_m$  -  $\phi_s$ ) exists even before the metal and semiconductor are brought into contact. Finally, the total potential drop,  $V_G$  across the MIS structure is given by,

$$V_G = \phi_{ms} + V_i + \psi_s \tag{2.6}$$

where  $\psi_s$  is the surface potential occurring in the semiconductor due to the depletion region. Using the expression for  $V_i$  in equation 2.5,  $V_G$  becomes,

$$V_{G} = \phi_{ms} - \frac{Q_{s} + Q_{i} + Q_{b}}{C_{i}} + \psi_{s}$$

2.7

A reference point for practical application is the gate voltage which needs to be applied on the gate in order to eliminate the depletion region or "flatten" the energy bands of the semiconductor. This voltage is referred to as the flat band voltage,  $V_{FB}$ .

$$V_{FB} = V_G(\psi_s = 0; Q_s = 0)$$

2.8

Substituting equation 2.7 into 2.8, V<sub>FB</sub> becomes,

$$V_{FB} = \phi_{ms} - \frac{Q_i + Q_b}{C_i}$$

2.9

It is observable that  $V_{FB}$  is a measure of the charge present at the interface and in the dielectric. For real MIS structures,  $V_{FB}$  is not zero. As a result, the capacitance-voltage (C-V) curves are usually parallel-shifted along the voltage axis by a magnitude,  $\Delta V_{FB}$ , corresponding to the additional voltage from the interface charges. For an ideal MIS structure,  $V_{FB}$  is zero.

#### 2.3 Interface Trap States

The presence of trapped charges in the bulk of the insulator or at the semiconductor-insulator interface results in a stretching of the C-V curve along the voltage axis and a parallel shift to either the right or left of the ideal curve. The shift in

flat band voltage,  $\Delta V_{FB}$  could be used to estimate the total trapped charge in the insulator,  $Q_{tot}$  [5].

$$Q_{tot} = C_{insulator} \Delta V_{FB}$$

2.10

Negative charge trapping in film results in positive  $\Delta V_{FB}$ , while positive charge trapping yields negative  $\Delta V_{FB}$ . The interface states are able to keep pace with low frequency variations of the gate bias (~ 1 – 1000Hz), but do not at very high frequencies (~ 1 MHz). As such, the interface traps contribute to the low frequency capacitance ( $C_{lf}$ ), but not to the high frequency capacitance ( $C_{hf}$ ). It is possible to calculate the density of interface ( $D_{it}$ ) from the difference in capacitance between  $C_{lf}$  and  $C_{hf}$  at a particular gate bias [6] using the relation,

$$D_{it} = \frac{1}{q} \left( \frac{C_i C_{lf}}{C_i - C_{lf}} - \frac{C_i C_{hf}}{C_i - C_{hf}} \right)$$

2.11

where q is the electronic charge.  $D_{it}$  (cm<sup>-2</sup>eV<sup>-1</sup>) can be measured for different gate biases in the depletion region. The draw-back in using the above capacitance method in estimating  $D_{it}$  lies in the difficulty in extracting the interface trap capacitance from the measured capacitance that comprises the insulator capacitance, the depletion-layer capacitance and the interface trap capacitance. It turns out that higher inaccuracies exist in the extraction of interface states information from the measured capacitance since the difference between two capacitances must be used. But, this is not the case in capacitance and conductance as functions of voltage and frequency measurements since both measurements contain similar information about the interface. As such, the conductance method is the preferred method of calculating  $D_{it}$  since the above difficulty

does not apply as the measured conductance is directly related to interface traps [7]. The conductance method proposed by Nichollian et al. [7] was employed in the calculation of interface state density ( $D_{it}$ ) in this work.

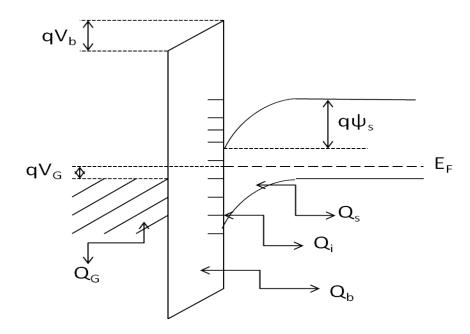

Here, the interface traps change occupancy over a few KT/q wide centered about the Fermi level by interacting with the semiconductor bands via the emission and capture of carriers. A small ac signal applied to the gate of an MIS diode results in an alternate movement of the band edges toward or away from the Fermi level. Using the conductance technique, interface trap states are detected through the loss resulting from changes in their occupancy due to small variations in dc gate bias. Usually, a conductance peak is observed as a result of the ac (energy) loss due to capture and emission of carriers by these interface states.

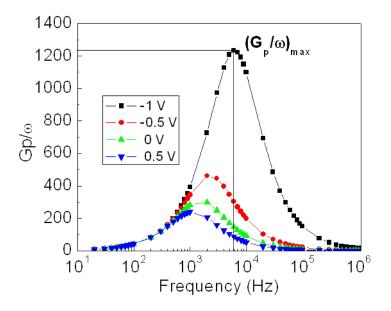

An equivalent conductance,  $G_p$  can be used to represent the energy loss due to capture and emission of carriers in a MIS structure. At fixed bias, an increase in energy loss is usually observed with a gradual increase in frequency in the low frequency range, which is attributed to a response of interface states to the low frequency with time lag. However, the energy loss decreases with further increase in frequency since fewer traps are now able to respond. A maximum energy loss is observed when most of the interface traps respond; as such, a measure of  $G_p$  over a range of frequencies and gate biases in the depletion region results in a measure of  $D_{tt}$  (Fig. 2.7).

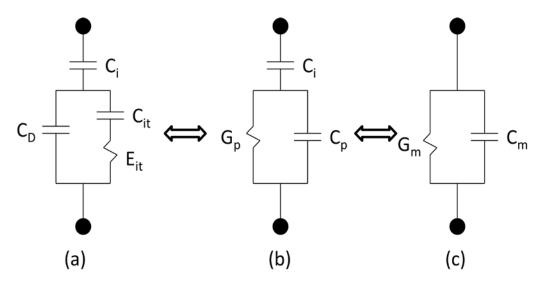

Shown in Fig. 2.8 are schematics of the equivalent, simplified and measured circuits of a MIS structure with interface traps. In Fig. 2.8a,  $E_{it}$  is the energy loss due to interface traps,  $C_{it}$  is the capacitance due to the trapped charges,  $C_D$  is the depletion

capacitance which is in parallel with the series connection of  $C_{it}$  and  $E_{it}$ , while the insulator capacitance,  $C_i$  is in series with  $C_{D_i}$ ,  $C_{it}$ , and  $E_{it}$ . Fig. 2.8b, which was derived from

Fig. 2.7: Plot of  $G_p/\omega$  as a function of log (f) for various gate biases in the depletion region.

Fig. 2.8: Schematics of (a) equivalent (b) simplified and (c) measured circuits for MIS structures with interface traps.

2.8a is a parallel combination of the equivalent conductance,  $G_p$  and the equivalent capacitance,  $C_p$ . Fig. 2.8c contains the measured parallel conductance,  $G_m$  and capacitance,  $C_m$  obtainable via direct measurements on a MIS structure using an LCR meter.  $G_p$  is obtainable from the measured data using the relation,

$$\frac{G_p}{\omega} = \frac{\omega G_m C_i^2}{G_m^2 + \omega^2 (C_i - C_m)^2}$$

2.12

where  $\omega=2\pi f$  is the radian frequency.  $G_p$  is estimated in the depletion region as a function of both gate bias and frequency.

Depending on the assumed energy distribution of the interface traps, either the single time constant (STC) or continuum of states model of the conductance method could be used to estimate  $D_{it}$ . For the STC model, the traps are assumed to behave as a single trap with a single energy level. Here, the admittance of the traps,  $Y_{it}$  is given by

$$Y_{it} = \frac{\omega^2 \tau C_{it}}{1 + \omega^2 \tau^2} + j \frac{\omega C_{it}}{1 + \omega^2 C^2}$$

2.13

where j is complex. In general,

$$Y_{it} = G_p + j\omega C_p$$

2.14

According to this model,  $G_p$  of a single level interface state is given by,

$$\frac{G_p}{\omega} = \frac{qD_{it}\omega\tau}{1+\omega^2\tau^2}$$

2.15

where  $qD_{it} = C_{it}$  is the interface states capacitance,  $\tau$  is the time constant of the interface state and  $G_p/\omega$  has a maximum at  $\omega \tau$ =1. For the continuum of states model which was used in the calculation of  $D_{it}$  in this work, the interface traps are assumed to have

energy levels that are so closely spaced across the band gap and as such, could be treated as a continuum of states. The admittance of the continuum of states model is

Fig. 2.9: Schematic of equivalent circuit for an STC model.

given by,

$$Y_{it} = \frac{C_{it}}{2\tau} \ln(1 + \omega^2 \tau^2) + j \frac{C_{it}}{\tau} \tan^{-1}(\omega \tau)$$

2.16

According to this model,  $G_p$  of a single level interface state is given by,

$$\frac{G_p}{\omega} = \frac{qD_{it}\ln(1+\omega^2\tau^2)}{2\omega\tau}$$

2.17

$G_p/\omega$  has a maximum at  $\omega\tau$ =1.98. From here,  $D_{it}$  can be calculated from the highest peak of  $G_p/\omega$  versus log (f) plot as shown in Fig. 2.7 (obtained from Eq. 2.9), using the relation,

$$D_{it} = \frac{2.5}{qA} \left(\frac{G_p}{\omega}\right)_{\text{max}} (cm^{-2}eV^{-1})$$

2.18

where A is the area of the MIS capacitor.

Fig. 2.10: Schematic of equivalent circuit for the continuum of states model.

#### 2.4 OFET Electrical Characteristics

The OFET, unlike a regular inorganic FET works in the accumulation mode. Looking at a hole-transporting (p-type) OFET which was used in this work, application of a negative gate voltage induces positive charges at the grounded source electrode, which are consequently injected into the organic semiconductor. For an effective hole injection, these electrodes (source and drain) materials must have Fermi levels that match or are close enough to the highest occupied molecular orbital (HOMO) of the organic semiconductor. This means that the hole injection barrier ( $\Delta$ ) between the Fermi level of the metal and HOMO level of the organic semiconductor must be as low as possible (Fig. 2.11). These accumulated positive charges form a conducting channel at the organic semiconductor-insulator interface and can be made to move along the channel and collect at the drain by an application of a negative voltage at the drain electrode. No current can flow from source to drain if the gate-source voltage ( $V_{GS}$ ) is lower than the threshold voltage ( $V_{T}$ ) ( $V_{GS} < V_{T}$ ), since there is no mobile charge at the

Fig. 2.11: Energy band diagram alignment at a metal-organic semiconductor interface. surface of the semiconductor. In the linear regime of the transistor (Fig. 2.12b) in which the current flowing through the channel is directly proportional to the drain-source voltage ( $V_{DS}$ ), for low  $V_{DS}$  ( $V_{DS}$  <<  $V_{GS}$ ), the drain-source current ( $I_{DS}$ ) is related to  $V_{DS}$  by

$$I_{DS(lin)} = \frac{WC_i}{L} \mu \left[ V_{GS} - V_T - \frac{V_{DS}}{2} \right] V_{DS}$$

2.19

where  $V_T$  is the threshold voltage,  $C_i$  is the dielectric capacitance per unit area and  $\mu$  is the field-effect mobility. The threshold voltage refers to the value of  $V_{GS}$  required to induce the inversion layer in an inorganic transistor or accumulation layer in an organic transistor (onset of transistor conduction).

For high  $V_{GS}$  ( $V_{GS} > V_T$ ), conduction is established if there is a potential ( $V_{DS}$ ) between the drain and the source. As  $V_{DS}$  increases from source to drain, a

point P,  $(V_{DS} = V_{GS} - V_{T})$  is reached at which the channel is "pinched-off" as

Fig. 2.12: (a) Schematic of an organic field-effect transistor. Illustrations of (b) linear (c) start of saturation and (d) saturation regimes of organic field-effect transistors.

shown in Fig. 2.12c. Due to the difference between the local potential V(x) and  $V_{GS}$  which is now below  $V_T$ , a depletion region develops next to the drain. Carriers pulled into the drain by the strong electric field that exists within the narrow depletion region between the drain and the pinch-off point, give rise to a space-charge-limited saturation current,  $I_{DS(sat)}$ . Further increase in  $V_{DS}$  will not result in an increase in current beyond the value it reached before the onset of the "pinch-off"; rather, it gives rise to an expansion of the depletion region and a reduction of the channel (Fig. 2.12d). This is the referred to as the saturation regime of the transistor. It is observable that the saturation current must be proportional to  $(V_{GS} - V_T)^2$  considering that the "pinch-off" potential  $(V_{DS} = V_{GS} - V_T)$  is the potential difference that drives the current through the conducting part of the channel, and the conductance of the channel itself is directly proportional to the density of mobile charge at the source-end of the channel. Therefore,

$$I_{DS(sat)} = \frac{WC_i}{2L} \mu (V_{GS} - V_T)^2$$

2.20

The OFET transfer characteristic plots the output drain current as a function of the input gate bias for a fixed drain bias. For the transfer characteristics in the saturation region, the square root of  $I_{DS}$  is plotted as a function of  $V_{GS}$ , with the threshold voltage as the intercept. Similarly, the slope of the transfer characteristics can be used to determine value of the saturation field-effect mobility,  $\mu_{(sat)}$  in the saturation regime using the relation,

Figure 2.13: Output characteristics for a typical OFET indicating the linear and saturation regimes.

The on/off current ratio and subthreshold slope (SS) are extractable from a plot of  $I_{D(sat)}$  on a logarithmic scale as a function of  $V_{GS}$  as shown in Fig. 2.14. Eq. 2.20 suggests that the current abruptly becomes zero as soon at the as  $V_{GS}$  equals  $V_T$ . In practice, this is not the case as there is still some drain conduction below threshold (Fig. 2.14) referred to as subthreshold conduction. This subthreshold current may be due to weak accumulation in the channel between flat band and threshold which may result in a diffusion current between source and drain. Usually, a plot of log ( $I_{DS}$ ) as a function of  $V_{GS}$  exhibits a linear behavior in the subthreshold regime (marked SS in Fig. 2.14) and the reciprocal of the slope of this line is known as the subthreshold slope (SS). For state-of-the art MOSFETs, SS has a typical value of  $\sim$  70 mV/decade at room temperature [6]. A smaller

value of SS implies that a small change in input bias considerably modulates the output current.

$$SS = \frac{dV_{GS}}{d(\log I_{DS})} = 2.3 \frac{KT}{q} \left[ 1 + \frac{C_D + C_{it}}{C_i} \right]$$

2.22

Figure 2.14: Transfer characteristics for a typical OFET indicating V<sub>T</sub> and SS.

#### 2.5 Organic Materials

#### 2.5.1 Polymer Dielectrics

Poly(methyl methacrylate) (PMMA) is an example of a polymer dielectric and was used in this study. Because it is a polymer dielectric, it is solution-processable. PMMA is a hard, rigid, hydrophobic, less-polar, and brittle polymer dielectric. It is one of the most common polymer dielectric materials. PMMA is a linear amorphous polymeric thermoplastic with high transparency and surface gloss [8]. It is highly resistive to oxidation and photodegradation [9], and stable to sunlight [10]. PMMA is also easily

Table 2.1: Various solvents used in this work and their properties.

| Solvent             | Dipole moment | Dielectric constant | Solubility parameter |

|---------------------|---------------|---------------------|----------------------|

|                     |               |                     | (MPa) <sup>1/2</sup> |

| Butyl acetate       | 1.84          | 5.01                | 17.4                 |

| Toluene             | 0.375         | 2.38                | 18.2                 |

| Anisole             | 0.994         | 4.33                | 19.5                 |

| Propylene carbonate | 4.90          | 64.90               | 27.2                 |

| Dimethyl suloxide   | 3.96          | 47.20               | 26.6                 |

preparable and available. Its monomer, methyl methacrylate (MMA) is synthesized by heating acetone cyanohydrins with sulfuric acid to form methacrylamide sulfate, which is then reacted with water and methanol to yield methyl methacrylate [9]. PMMA has a

Fig. 2.15: Molecular structures of (a) PMMA and (b) PVP.

dielectric constant that ranges from about 3.5 (at 5 kHz) to 2.6 (at 1 MHz). In this work, PMMA (Mw = 996,000 g/mol.) obtained from Sigma-Aldrich was used as the gate dielectric layer in our OFETs and diodes. Another polymer dielectric that was used in this work is poly (4-vinyl-phenol) (PVP). Unlike PMMA, PVP is a hydrophilic polymer dielectric with a dielectric constant that ranges between 4.0 and 5.2. Table 2.1 contains the various solvents used in this work and their respective properties.

#### 2.5.2 Organic semiconductors

Pentacene is an aromatic hydrocarbon and one of the most promising and extensively studied organic small molecule semiconductors with quite high carrier mobility. Small molecule semiconductors are usually evaporated. Pentacene is a planar molecule with five linearly-fused benzene rings with herringbone packing of two molecules per unit cell resulting in a triclinic crystal structure. It could be thermally evaporated under both high and low vacuum pressures. During evaporation, pentacene film formation begins with an adsorption and subsequent diffusion of the sublimated pentacene molecules on a substrate, which proceeds to a two-dimensional (2D) island at some critical film quantity. The growth finally changes to three-dimensional (3D) growth with the deposition of about one or some monolayer of films. In this work, pentacene (obtained from Tokyo Chemical Industrial Co. Ltd) was used as the

Fig. 2.16: Molecular structure of pentacene.

semiconductor in some of our OFETs and MIS diodes.

9,9-dioctylfluorene-co-bis-N-N-(4-butylphenyl)-bis-N,N-phenyl 1,4-phenylenediamine (PFB) is a polymer semiconductor and was used in this work. It belongs to the family of polyfluorenes (PFs). PFB, just like all polymer semiconductors is solution-processable. PFs are polymers that emit light via electroluminescence; as such, are promising materials for optoelectronic device applications, especially light-emitting diodes (LEDs) considering their electroactive, photoactive, and excellent electro-optical characteristics. PFs have the fluorene unit as their building blocks. Polyfluorenes have high thermal stability and can emit light across the entire visible spectrum [11]. In this study, PFB (obtained from American Dye Source) was used as the semiconductor in some of our OFETs and diodes. Our choice of PFB here was mainly due to the very close matching of its HOMO level with the Fermi level of the gold source and drain contacts.

Fig. 2.17: Molecular structure of PFB.

#### **CHAPTER 3**

## **EXPERIMENTAL TECHNIQUES**

### 3.1 Film Deposition

## 3.1.1 Spincoating

Spincoating is a technique that is typically employed in the deposition of polymeric thin films onto substrates (flexible and non-flexible). The procedure could be summarized thus: (a) an amount of a solution (material to be deposited) is dispensed on the substrate either before substrate rotation or while the substrate is slowly rotating (b) the substrate is rotated at a pre-set speed which is usually a few thousand rotations per minute (rpm), and (c) the solution spreads outwards with a resultant thin film formation. The process completes with baking/curing in an oven – a process aimed at evaporating the solvent out of the film. The spincoating process could be modeled thus [12]:

$$d = \left(\frac{\eta}{4\pi\ell\,\omega^2}\right)^{1/2} \left(\frac{1}{t}\right)^{1/2}$$

3.1

where d is the thickness of the spincoated film,  $\eta$  is the coefficient of viscosity of the solution,  $\ell$  is the density of the solution,  $\omega$  is the angular frequency of the spin, and t is spin time.

#### 3.1.2 Matrix-assisted pulsed-laser evaporation (MAPLE)

MAPLE is a derivative of pulsed laser deposition (PLD), which is a deposition technique whereby a pulsed laser beam focused down by a lens hits a target of the desired material and creates a plume of the material perpendicular to the target surface. Typical lasers employed include ArF, KrF excimer lasers, and Nd:YAG laser. The main difference between MAPLE and PLD is in the original forms of the targets. While the PLD target is always solid, the MAPLE target is originally a liquid solution but turned into a solid via freezing. The MAPLE set-up used in our work has a KrF excimer laser source (Lambda Physik COMPex) and a vacuum system that can attain pressures up to 10<sup>-5</sup> mbar with the aid of roughing and turbo pumps. The vacuum deposition system (Fig. 3.1) comprises a deposition chamber, target carousel with target holders, a variable temperature substrate holder, and many standard ports such as pumping ports, gas inlet, pressure gauge, and view ports. Different parts are indicated in Fig. 3.2: the laser port, L; the target port flange-to-beam focal plane distance, Z; the target to substrate distance, S, and the substrate-to-flange distance, T. The target-to-substrate distance is usually about 5-15 cm. MAPLE involves a complex physical process of the interaction of high-power pulsed irradiation on a frozen target with the laser beam, the formation of plasma plume, and the transfer of the ablated material through the plasma plume onto

the substrate surface. Hence, MAPLE deposition of polymer thin films could be broken down into four different steps:

- (a) Interaction of the laser radiation with the target

- (b) Ablation materials dynamics

- (c) Deposition of the ablated materials onto the substrate

- (d) Thin film growth and nucleation on the substrate surface

Fig. 3.1: The MAPLE system at Missouri State University in Springfield, Missouri.

The first step involves a focusing of the laser beam onto the surface of the target, and subsequent stoichiometric dissociation and ablation of the target material from the target surface. Various complex physical phenomena such as collisions, heating, electronic excitation etc, accompany the ablation process.

The second step involves a movement of the dissociated materials from the target towards the substrate as governed by the laws of gas-dynamics. Here, the

majority of the laser intensity is initially absorbed by the solvent molecules (toluene) which cause them to vaporize. Then the kinetic energy of the solvent molecules is transferred to the solute through collective collisions, causing the polymer to evaporate and deposit on the substrate. All polymer films were deposited at room temperature. The films were deposited for ~ 30 min with the growth rate of ~ 0.6 nm/min. During the deposition, the target was kept frozen by passing liquid nitrogen externally through a tube which goes into the target holder. The uniformity of the deposited film on the substrate is affected by the spot size of the laser and the plasma temperature. Also the angular spread of the ablated materials depends on the target-to-substrate distance.

Figure 3.2: Schematic diagram of the MAPLE system.

In the third step, the emitted high-energy species impinge on the substrate surface. This step is critical in determining the quality of the film. Here, some of the surface atoms are sputtered by the energetic species, and this leads to the formation of

a collision region between the incident flow and sputtered atoms; films grow only on the formation of a thermalized region.

The growth and nucleation step is a critical step which depends on such factors as the energy of the laser, density, and ionization degree, as well as physical and chemical properties of the substrate. The growth of the film is dependent on the surface mobility of the adatom, which diffuses through several atomic distances before settling at a stable position within the film. The nucleation process depends on the interfacial energies between the substrate, condensing material, and vapor.

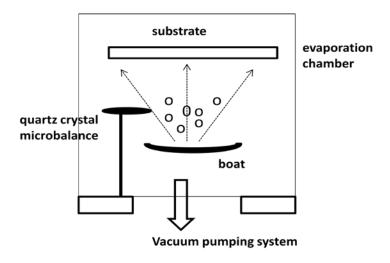

#### 3.1.3 Thermal evaporation

At high enough temperatures, a solid can vaporize whereby the molecules of the solid are detached from the solid. This process is harnessed for deposition of thin films on substrates. The process could be summarized thus: (a) heating of solid causes an escape of molecules from the solid (b) the removed molecules travel over some distance in the vacuum from the source to the substrate (c) the molecules deposit on the susbtrate resulting in thin film growth. According to kinetic theory [13], the mean free path of gas atoms ( $\lambda$ ) is given by

$$\lambda = \frac{k_B T}{P \pi d^2 \sqrt{2}} \quad , \tag{3.2}$$

where d is the diameter of the molecules, T is temperature, P is pressure, and  $k_B$  is Boltzmann's constant. From the above relation, it becomes necessary to evaporate at low pressures in order to ensure that the depositing species travel from source to substrate with minimal impurity collisions. It is desirable to ensure that  $\lambda$  exceeds the

source-to-substrate distance. Also from the Langmuir relation [13], the rate of evaporation,  $\Gamma$  from a surface is given by

$$\Gamma = P \left( \frac{M}{2\pi RT} \right)^{1/2} , \qquad 3.3$$

where P is the vapor pressure of the material at temperature T, R is the gas constant,

Fig. 3.3: Schematic of thermal evaporating system.

and *M* is the molecular weight. There are usually collisions between the traveling molecules and impurity gases in the evaporation chamber. Critical considerations for thin film growth using thermal evaporation include the deposition rate as well as the substrate temperature during deposition. A typical thermal evaporation system comprises evaporation chamber, a vacuum pumping system, a crucible boat (that holds the Joule heated source material), and a quartz crystal balance (for measurement of film thickness).

### 3.2 Experimental details

#### 3.2.1 Device structures and fabrication

The device fabrication process begins with the ultrasonic cleaning of our  $1" \times 1"$  cut glass substrates with distilled water, acetone and alcohol, respectively. This is immediately followed by air drying of the glass substrates. Shown in Fig. 3.4 (a) and (b) are the configurations for our OFETs and MIS diodes, respectively. The structures are of bottom-gate configuration. And as the name implies, the aluminum gate electrode was first

Fig. 3.4: Schematic representations of our (a) OFET and (b) MIS diode structures.

deposited on the glass substrate, which is followed by the deposition of the dielectric and semiconductor layers, respectively. The structures were then completed with the

deposition of the source and drain contacts (for the OFET) and top metal contact (for the MIS diode) onto the semiconductor layer. For the OFETs, the source and drain contacts must be in direct contact with the semiconductor so as to achieve good carrier injection, while the gate is separated from the semiconductor by the dielectric layer.

In this work, aluminum gate was deposited on cleaned and dried glass substrates by evaporation at room temperature using an MBraun thermal evaporation system located in a glove box. The pressure inside the evaporation chamber was initially pumped down to about  $10^{-2}$  mbar using a roughing pump, and afterwards to pressures of  $10^{-5}$  to  $10^{-6}$  mbar with the aid of the turbo pump. This automated thermal evaporation system is controlled by an SQC-222 co deposition controller. The evaporation source materials were Al pellets (99.9 % purity) held in a tungsten boat, while the glass substrates were screwed down on a custom-built metallic plate fitted in the substrate holder. The Al gate layer with a thickness of about 60 nm was evaporated at a rate of ~ 3 Å/s. The film thickness and deposition rate were monitored via the SQC-222 co deposition controller which is connected to a quartz crystal microbalance.

The aluminum gate deposition process was followed by spincoating of polymer dielectrics. PMMA and PVP dielectrics were used. The thickness of a spincoated film is mostly dependent on the concentration of the solution and spin speed. Here, we used an 8" desk-top precision spincoating system (Model P-6708D), located in a glove box (right box of Fig. 3.4). The solution was dropped on the Al-coated substrate before spinning at an initial low spin speed of about 500 r.p.m. The spin speed was increased afterwards to about 2000 – 5000 r.p.m in order to achieve the desired film thicknesses.

For the MAPLE project, 8 wt% of PMMA (996,000 g/mol) purchased from Sigma-Aldrich and dissolved in three different solvents: butylacetate, toluene, and anisole, were spincoated onto cleaned Al-coated glass substrates at 2000 r.p.m for 60 s, resulting in film thicknesses of between 500 and 550 nm as measured using a reflectometer. Thereafter, the samples were baked at 100 °C for 1 h in order to achieve solvents evaporation.

Fig. 3.5: MBraun glove box system with thermal evaporator in box 1 (left).

For the PMMA-pentacene project, again, 8 wt% of PMMA (996,000 g/mol) purchased from Sigma-Aldrich and dissolved in two different solvents: propylene carbonate (PC) and butylacetate (BTAc), were spincoated onto cleaned Al-coated glass substrates at 5000 r.p.m for 60 s, resulting in film thicknesses of ~ 70 nm and ~ 350 nm for PMMA-PC and PMMA-BTAc films, respectively. The films were then baked at 100 °C for 1 h in order to achieve solvents evaporation. For the PVP-pentacene project, 8 wt%

of pristine PVP (25,000 g/mol) and PVP cross-linked with poly (melamine-coformaldehyde) methylated, purchased from Sigma-Aldrich and dissolved in propylene carbonate were spincoated onto cleaned Al-coated glass substrates at 5000 r.p.m for 60 s. The resulting film thicknesses were  $^{\sim}$  80 nm and  $^{\sim}$  30 nm, respectively. The films were then baked at 100 °C for 1 h in order to achieve solvents evaporation.

Next was the deposition of the semiconducting layers. For the MAPLE project, the polymer semiconductor – PFB was deposited on the PMMA dielectric layers using earlier discussed MAPLE technique. While for the PMMA and PVP-pentacene projects, an organic small molecule semiconductor – pentacene was thermally evaporated on the polymer dielectric layers at room temperature using an MBraun thermal evaporation system located in a glove box. The evaporation source material was pentacene purchased from Tokyo Chemical Industrial Co. Ltd., which was held in a quartz crucible, while the PMMA and PVP-covered substrates were screwed down on a custom-built metallic plate fitted in the substrate holder. The pentacene film layer with a thickness of about 60 nm was evaporated at a rate of ~ 0.3 Å/s. The film thickness and deposition rate were monitored via the SQC-222 co deposition controller which is connected to a quartz crystal microbalance.

Our device structures were completed with the room temperature evaporation of the source and drain gold contacts for the OFETs and top gold contact for the MIS capacitors onto the semiconductor layers. This was done using the MBraun thermal evaporation system located in a glove box. The evaporation source materials were gold wires purchased from Kurt J. Lesker (99.9 % pure), which were held in a tungsten boat,

while the semiconductor-covered substrates were screwed down on a custom-built metallic plate fitted in the substrate holder. The gold contacts with thicknesses of about 40 nm were evaporated at a rate of  $\sim$  3 Å/s. The film thicknesses and deposition rate were monitored via the SQC-222 co deposition controller which is connected to a quartz crystal microbalance. The gold source and drain electrodes, which define a channel length (L) of 0.05–0.10 mm and channel width (L) 0.50–1.00 mm for the FETs, and top gold contacts for MIS diodes, were deposited though metallic shadow masks. The device area for MIS structures, determined by a scanning electron microscope, varied between 2–8 × 10<sup>-3</sup> cm<sup>2</sup>.

Finally, for the MAPLE project, each of our devices contains both FET and MIS diode with Al/PMMA/PFB/Au structure and is named according to the solvent used to dissolve PMMA: butylacetate (Sample A), toluene (Sample B), and anisole (Sample C). For the PMMA-pentacene project, each of our devices contains both FET and MIS diode with Al/PMMA/Pentacene/Au structure and is named according to the solvent used to dissolve PMMA: devices fabricated with PMMA using butyl acetate (BTAc) as the solvent are denoted as PMMA-BTAc while OFETs/MIS structures cast from PC are simply denoted as PMMA-PC. Also for the PVP-pentacene project, each of our devices contains both FET and MIS diode.

#### 3.3 Device characterizations

#### 3.3.1 Atomic force microscopy

Atomic force microscopy (AFM) is a highly sensitive method which mechanically gives information about surface morphology with atomic scale resolution. The basic idea

is to let a sharp tip scan the surface of the sample. A small force applied to the tip moves the tip across the surface resulting in a variation in force between the tip and the surface atoms. The tip is mounted on a cantilever and the force causes it to deflect. The deflection is usually measured by a laser beam which is reflected in different angles depending on the degree of deflection. The actual force can then be calculated using Hooke's law, F = -kz; where F is the force, k is the cantilever spring constant and z is the displacement of the cantilever [14]. A piezoelectric system is used to move the tip

Fig. 3.6: Schematic representation of the working principle of the atomic force microscope.

across the surface with high precision. The AFM has three different modes of operation: contact mode, non-contact mode and tapping mode [14]. Cypher scanning probe AFM used in the tapping mode was employed in this work. As the name implies, the tip taps the surface. The tip is set in motion, oscillates at or close to the resonance frequency and moves with an amplitude typically > 20 nm. Starting away from the surface, the tip

is slowly brought in contact with the surface, tapping the surface atoms. An energy loss to the surface atoms and a decrease in amplitude occur due to the tapping. A feedback loop keeps the amplitude and force, constant by adjusting the separation during movement.

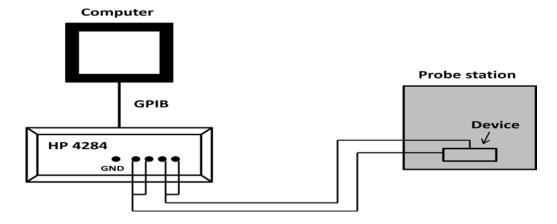

### 3.3.2 MIS capacitance-voltage measurement

The charges inside the dielectric and at the interfaces of a MIS structure can be measured by measuring the capacitance as a function of voltage (C-V). During the measurement, an ac signal with small amplitude of usually between  $10-15\,$  mV is superimposed on a dc voltage that is swept from the negative to the positive. While the ac signal is required to measure the capacitance, the dc voltage determines the bias condition. An inductance-capacitance-resistance (LCR) HP 4284A meter was utilized for the C-V measurements. It provides a dc voltage of  $\pm 40\,$ V and an ac frequency of 20 Hz to 1 MHz. Most of our measurements were performed at low frequencies (1 kHz  $-10\,$ kHz) with a 100 mV ac signal at a scan rate of 0.05 V/s. A sketch of a C-V measurement set-up is shown in Fig. 3.8.

Fig. 3.7: A sketch of a C-V measurement set-up.

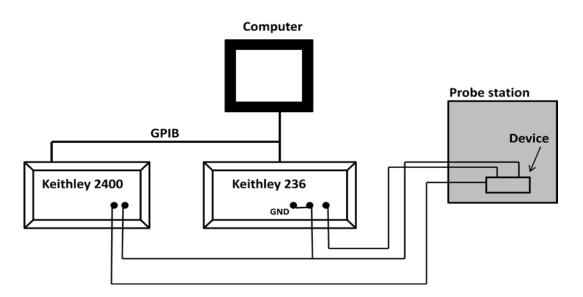

#### 3.3.3 OFET current-voltage measurement

The current-voltage (I-V) characteristics of our OFETs were carried out under ambient conditions using the Keithley 2400 and 236 source/measure units. This is usually a three-probe measurement. For a measurement of the OFET output characteristics, a set dc voltage was applied to the gate via the 2400 source meter, while the 236 source/measure unit was used to simultaneously sweep the drain-source voltage (V<sub>DS</sub>) and measure the drain current (I<sub>D</sub>). The measurement was repeated with several gate voltages. For measurement of the transfer characteristics, a sweeping dc voltage was applied to the gate via the 2400 source meter, while the 236 source/measure unit was used to supply set V<sub>DS</sub> and measure I<sub>D</sub> as well. A two-probe measurement set-up making use of only the 236 source/measure unit was used for measuring the gate leakage current of the dielectric layer. A sketch of I-V measurement set-up for an OFET is shown in Fig. 3.9.

Fig. 3.8: A sketch of OFET I-V measurement set-up.

#### **CHAPTER 4**

# MAPLE PFB FILMS FOR ORGANIC FIELD-EFFECT-TRANSISTORS AND METAL-INSULATOR-SEMICONDUCTOR CAPACITORS WITH POLY (METHYL METHACRYLATE) GATE DIELECTRIC

#### 4.1 Introduction

Lately, considerable research efforts have been directed at organic semiconductors and dielectrics and their applications in organic field-effect transistors and diodes owing largely to their low cost solution processable fabrication. Organic devices can be fabricated by spincoating and other cost effective procedures such as inkjet printing. Active matrix displays based on organic thin film transistors and integrated circuits realized via inkjet printing have been reported [15-19]. There exist ample reports where polymer dielectrics with varying dielectric constant have been used with small molecule semiconductors such as pentacene and rubrene [20,21] and high/low-k inorganic insulators such as SiO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> have also been used with solution processable conjugated polymers [21,22]. Among polymer semiconductors, poly (3-hexylthiophene) (P3HT), when used with SiO<sub>2</sub> as the dielectric has been shown to yield carrier mobility as high as 0.2 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> [23]. Nevertheless polymeric dielectric materials are preferred to their inorganic counterparts due to their numerous advantages: easily

processable, low cost, flexible, and hydrophobic. Unfortunately, the fabrication of polymer thin film transistors and diodes in which both the semiconductor and the dielectric layer are solution processable polymers has been limited. This limitation is due to the inherent fabrication problem whereby an underlying dielectric layer can be damaged by spincoating the overlying semiconducting layer, in the case of bottom-gate architecture or where an underlying semiconducting layer can be damaged by spincoating the overlying dielectric layer, in the case of top-gate device architecture.

Sun et al. [24] have reported baking their PMMA dielectric film at a high temperature of 220 °C for 30 min in nitrogen gas environment in order to make the film resistant to swelling and dissolution by trichlorobenzene (TCB) used to dissolve the overlying semiconducting layer. They observed that for PMMA films baked at lower temperatures, spincoating with TCB resulted in changes in film color and increase in surface roughness. Also the difficulty in finding an orthogonal and stable solvent that does not dissolve the underlying semiconducting film when spincoated has been identified as one of the obstacles in applying crosslinkable polymer thin gate dielectrics in top-gate transistor architectures [25]. The use of solution processable semiconductor with divinyl-tetramethylsiloxane-bis(bisbenzocyclobutene) derivative (BCB), as a solution processable dielectric has been reported [26,27], but it turns out that BCB requires a very high curing temperature (250 °C), which is difficult to handle at times.

This work introduces matrix-assisted pulsed-laser evaporation (MAPLE), a derivative of pulsed laser deposition (PLD), as an alternative fabrication technique that circumvents the inherent solvent selectivity problem encountered in the fabrication of

organic field-effect transistors (OFET) and metal-insulator-semiconductor (MIS) diodes via spincoating. Besides offering the advantage of good layer-by-layer film control, remarkable features of this technique are its solvent non-selectivity and its ability to not cause the swelling and dissolution of polymer dielectrics and semiconductors, common inherent problems associated with spincoating. Here, an organic semiconducting material, 9,9-dioctylfluorene-co-bis-N-N-(4-butylphenyl)-bis-N,N-phenyl 1,4-phenylenediamine (PFB) was dissolved in a toluene solvent and frozen at liquid nitrogen temperatures. Then the frozen target is irradiated by a pulsed laser beam (e.g. KrF excimer laser), whose energy is absorbed by the toluene and is pumped away, thereby leaving the PFB molecules to be gently evaporated and deposited without causing any swelling or dissolution of the PMMA film on the substrate. Our prior studies of MAPLE deposited polyfluorene films show that the optical and structural properties of the films remain unchanged comparable to spincoated films [28].

## 4.2 Results and Discussion

### 4.2.1 Dielectric Film: Morphology and Electrical Characteristics

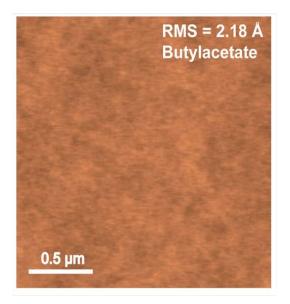

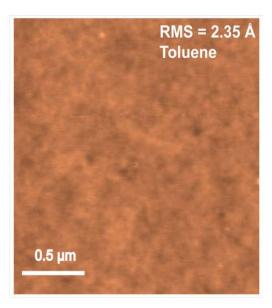

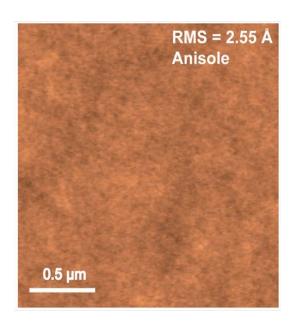

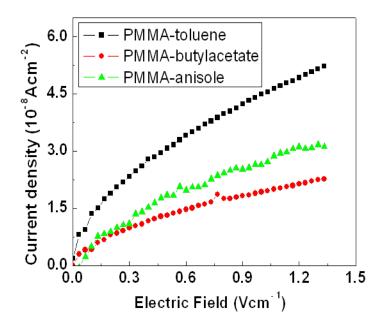

The surface morphology of the films resulting from dissolving PMMA in butylacetate, toluene, and anisole, obtained by means of AFM (Cypher scanning probe microscope) in tapping mode are shown in Fig. 4.1. The films exhibited very smooth surfaces with root-mean-square values of 2.18 Å, 2.35 Å, and 2.55 Å for butylacetate, toluene, and anisole, respectively. Parallel plate capacitor structures (Al/PMMA/Al) were fabricated to investigate the dielectric properties of PMMA. The leakage current density of the films is in the low 10<sup>-8</sup> A cm<sup>-2</sup> for applied fields of up to 1.4 MV cm<sup>-1</sup> (Fig.

4.2) and measurements of the dielectric constant of PMMA dissolved in the different solvents revealed a decrease of the observed dielectric constant from approximately 3.50 at 5 kHz to 2.81 at 1 MHz. This range of values is in good agreement with other published reports [29,30].

Fig. 4.1: Atomic force micrographs of PMMA films prepared in different solvents.

Fig. 4.2: Current density – electric density characterization for PMMA dielectric film dissolved in butylacetate, toluene, and anisole.

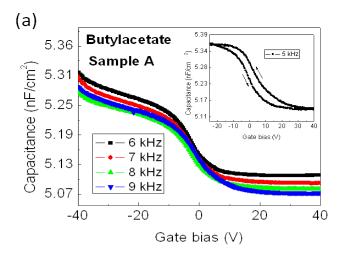

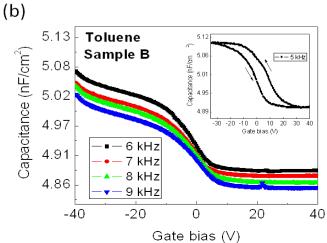

#### 4.2.2 MIS Diode Characteristics

Figure 4.3 shows capacitance-voltage (C-V) characteristics of PFB MIS diodes with PMMA dielectric dissolved in butylacetate, toluene, and anisole measured at four different frequencies in the low kHz range. Observable is the existence of frequency dispersions in the accumulation and depletion regions. The C-V curves are typical of p-type organic MIS behavior characterized by an accumulation of holes at the dielectric/semiconductor interface at large negative bias, a depletion of holes from the dielectric/semiconductor interface at less negative bias, and a deep depletion of holes from the dielectric/semiconductor interfacial region at positive bias, corresponding to the accumulation, depletion, and deep depletion regimes. No inversion is observed, which is typical of organic MIS diodes. The amount of frequency dispersion in