# HIERARCHICAL SCHEDULING AND UNIFORM ACCESS PROGRAMMING FRAMEWORKS FOR HETEROGENEOUS CPU-GPU COMPUTING CLUSTERS

\_\_\_\_\_

A Dissertation

presented to

the Faculty of the Graduate School at the University of Missouri-Columbia

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy

\_\_\_\_\_

by

KITTISAK SAJJAPONGSE

Dr. Michela Becchi, Dissertation Supervisor

JULY 2015

The undersigned, appointed by the dean of the Graduate School, have examined the dissertation entitled

# HIERARCHICAL SCHEDULING AND UNIFORM ACCESS PROGRAMMING FRAMEWORKS FOR HETEROGENEOUS CPU-GPU COMPUTING CLUSTERS

| presented by Kittisak Sajjapongse, a candidate for the degree of doctor of philosophy, |                                                                                                  |  |

|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|

|                                                                                        |                                                                                                  |  |

| and nereby certify                                                                     | that, in their opinion, it is worthy of acceptance.                                              |  |

|                                                                                        |                                                                                                  |  |

|                                                                                        |                                                                                                  |  |

|                                                                                        | Dr. Michela Becchi, Assistant Professor, Department of<br>Electrical and Computer Engineering    |  |

|                                                                                        |                                                                                                  |  |

|                                                                                        | Dr. Guilherme DeSouza, Associate Professor,<br>Department of Electrical and Computer Engineering |  |

|                                                                                        | Dr. Tony Han, Associate Professor, Department of Electrical and Computer Engineering             |  |

Dr. Prasad Calyam, Assistant Professor, Department of Computer Science

#### **ACKNOWLEDGEMENTS**

This work is completed with the help and support from those whom I sincerely respect. Without their support, my efforts could have been far from complete. I am fortunate to have them along the course of my studies and my future career.

My mentor: I would like to deeply thank my advisor, Michela Becchi, for her support and mentorship. I am fortunate and grateful to have worked with her during my studies. The association with Dr. Becchi trained me to think systematically in both professional and personal aspects. I also appreciate her generosity and flexibility in offering me opportunities to interact with other scientists and to explore the research community.

My Colleagues & Friends: Thank you to all the current and previous members of the Networking and Parallel System laboratory, especially Da Li, Ruidong Gu, Huan Troung, Tejaswi Agarwal, and Xiang Wang for working together through difficult times and for their friendship. Thank you to my dear friend and collaborator, Vignesh Ravi, for his valuable discussions and great opportunities. I would also thank to Fadi Muheidat who is very generous and could always keep me positive.

My family: I would like to express my deepest appreciation and thanks to my parents and sisters: Adisak, Tommarat, Jurairat, and Naovarat Sajjapongse for their unconditional love and encouragement. I am very grateful to have a supportive family who puts my education as the first priority.

My wife: My wife, Sasiwimon Yoo-eam, is a great researcher with whom I can always share ideas even though we focus on different disciplines. Thank you for your love, support, staying beside each other, and sharing our lives together.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTSii |        |                                                   |     |

|--------------------|--------|---------------------------------------------------|-----|

| LIST OF IL         | LUSTI  | RATIONS                                           | vii |

| LIST OF TA         | ABLES  | 5                                                 | x   |

| ABSTRAC            | Γ      |                                                   | xi  |

| Chapter            |        |                                                   |     |

| CHAPT              | ER 1   | INTRODUCTION                                      | 1   |

| 1.1                | Introd | luction                                           | 1   |

| 1.2                | Motiv  | vations                                           | 2   |

|                    | 1.2.1  | Software support for GPUs                         | 3   |

|                    | 1.2.2  | Resource Managers                                 | 5   |

|                    | 1.2.3  | Programmability                                   | 7   |

| 1.3                | Contr  | ibutions                                          | 9   |

|                    | 1.3.1  | Runtime Supports for Distributed GPU applications | 9   |

|                    | 1.3.2  | Hierarchical Resource Management                  | 9   |

|                    | 1.3.3  | Programming Framework for Uniform Resource Access | 10  |

| 1.4                | Organ  | nization                                          | 10  |

| СНАРТ              | ER 2   | BACKGROUND AND RELATED WORK                       | 12  |

| 2.1                | Backg  | ground                                            | 12  |

|                    | 2.1.1  | Graphic Processing Units (GPUs)                   | 12  |

|                    | 2.1.2  | Programming Models for Heterogeneous Clusters     | 14  |

|                    | 2.1.3  | Message-Passing Interface (MPI)                   | 17  |

|                    | 2.1.4  | Partitioned Global Address Space (PGAS)           | 18  |

| 2.2                | Relate | ed Work                                           | 21  |

|       | 2.2.1 | Node-level Schedulers and Runtime Support     | 21 |

|-------|-------|-----------------------------------------------|----|

|       | 2.2.2 | Cluster-level Schedulers and Resource Sharing | 23 |

|       | 2.2.3 | Programming Models for Heterogeneous Clusters | 26 |

| СНАРТ | ER 3  | NODE-LEVEL RUNTIME                            | 28 |

| 3.1   | Objec | ctives                                        | 28 |

| 3.2   | Refer | ence Architecture                             | 33 |

| 3.3   | Scheo | duling Policies                               | 35 |

|       | 3.3.1 | Batch Scheduling                              | 35 |

|       | 3.3.2 | Controlled n-way GPU Sharing                  | 36 |

|       | 3.3.3 | Preemptive Sharing                            | 40 |

| 3.4   | Use C | Cases for Preemption                          | 41 |

| 3.5   | Syste | m Design                                      | 44 |

|       | 3.5.1 | Overall Design                                | 45 |

|       | 3.5.2 | Context Queues                                | 46 |

|       | 3.5.3 | Connection Manager                            | 46 |

|       | 3.5.4 | Dispatcher                                    | 47 |

|       | 3.5.5 | Virtual GPUs                                  | 49 |

|       | 3.5.6 | Memory Manager                                | 50 |

|       | 3.5.7 | Fault Tolerance & Checkpoint-Restart          | 57 |

|       | 3.5.8 | Inter-node offloading                         | 58 |

| 3.6   | Suppo | orting Preemptive GPU Sharing                 | 59 |

|       | 3.6.1 | Defining the Preemption Policy                | 59 |

|       | 3.6.2 | Implementation                                | 60 |

| 3.7   | Expe  | rimental Results                              | 63 |

|       | 3.7.1  | Single-process Application63                   |

|-------|--------|------------------------------------------------|

|       | 3.7.2  | Multi-process Application                      |

| СНАРТ | ER 4   | CLUSTER-LEVEL SCHEDULER90                      |

| 4.1   | Objec  | etives90                                       |

| 4.2   | Cluste | er-level Scheduler92                           |

|       | 4.2.1  | Scheduler Architecture95                       |

|       | 4.2.2  | Scheduling API                                 |

| 4.3   | Sched  | luling Policies                                |

|       | 4.3.1  | Co-locating Scheduler                          |

|       | 4.3.2  | Latency-reducing Scheduler                     |

| 4.4   | Expe   | rimental Results                               |

|       | 4.4.1  | Benchmark Applications                         |

|       | 4.4.2  | Experimental Setup                             |

|       | 4.4.3  | Analysis of Co-location                        |

|       | 4.4.4  | Determining the Weights for the Nodes113       |

|       | 4.4.5  | Experiments on Heterogeneous Workloads115      |

| СНАРТ | ER 5   | INTER-NODE VIRTUAL MEMORY PROGRAMMING MODEL118 |

| 5.1   | Objec  | etives118                                      |

| 5.2   | Backg  | ground and Motivations120                      |

|       | 5.2.1  | Traditional Programming Models                 |

|       | 5.2.2  | Load Balancing                                 |

|       | 5.2.3  | The IVM Programming Framework                  |

| 5.3   | IVM    | Framework Design124                            |

|       | 5.3.1  | Execution Model                                |

|        | 5.3.2 | Memory Model                             | 125 |

|--------|-------|------------------------------------------|-----|

|        | 5.3.3 | System Design                            | 127 |

|        | 5.3.4 | GPU Support                              | 130 |

|        | 5.3.5 | IVM Programming Interface                | 133 |

|        | 5.3.6 | Integration to Higher-level Scheduler    | 136 |

| 5.4    | Bench | nmark Applications and Load Balancing    | 137 |

|        | 5.4.1 | Load Balancing Schemes                   | 137 |

|        | 5.4.2 | Benchmark Applications                   | 140 |

| 5.5    | Exper | rimental Evaluation                      | 142 |

|        | 5.5.1 | Experimental Setup                       | 143 |

|        | 5.5.2 | Dynamic Spawning Load Balancing (DS-LB)  | 145 |

|        | 5.5.3 | Online Monitoring Load Balancing (OM-LB) | 147 |

|        | 5.5.4 | Discussion                               | 149 |

| СНАРТ  | ER 6  | CONCLUSION & FUTURE WORK                 | 150 |

| BIBLIO | GRAP  | НҮ                                       | 157 |

| VITA   |       |                                          | 164 |

# LIST OF ILLUSTRATIONS

| Figure Pag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | e, |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

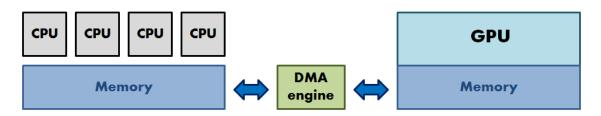

| Figure 2-1 – Memory model between CPUs and GPU1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2  |

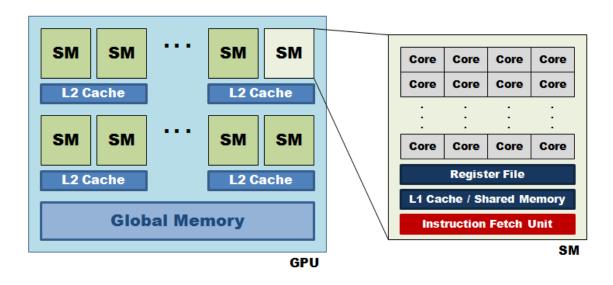

| Figure 2-2 – GPU architecture under CUDA framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3  |

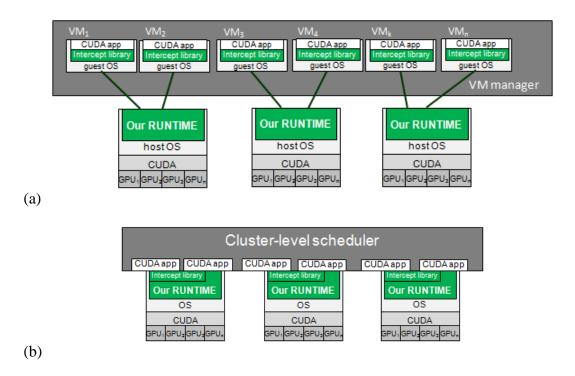

| Figure 3-1 – Two deployment scenarios for our runtime: (a) VM-based cloud computing service and (b) HPC cluster resource manager.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9  |

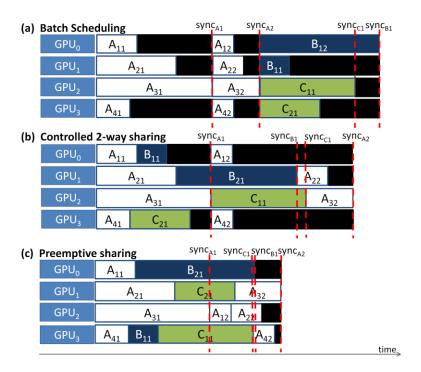

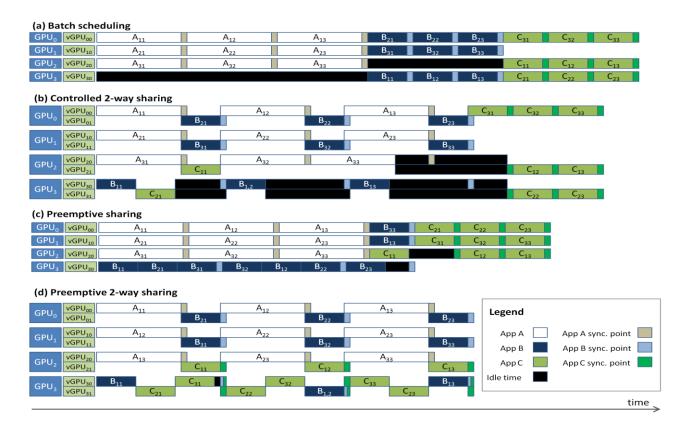

| Figure 3-2 – Operation of different scheduling mechanisms in the presence of multi-tasks distributed applications with synchronizations and <i>intra-application</i> imbalance.  Application A consists of 4 tasks and includes 2 GPU execution phases, with a global synchronization at the end of each. Application B and C consist of two tasks and a single GPU execution phase, also ending with a global synchronization. Synchronizations are represented through (red) dashed vertical lines. A <sub>jk</sub> represents k <sup>th</sup> GPU phase of task j belonging to application A. Idle GPU times are represented in black. | 8  |

| Figure 3-3 – Operation of different scheduling mechanisms in the presence of multi-tasks applications with synchronization and <i>inter-application imbalance</i> .  Application <i>A</i> , <i>B</i> , and <i>C</i> consist of 3 tasks and include 3 GPU execution phases, with a global synchronization at the end of each. <i>A</i> <sub>jk</sub> represents the <i>k</i> <sup>th</sup> GPU execution phase of task <i>j</i> belonging to application <i>A</i> . Idle GPU times are represented in black                                                                                                                                | 2  |

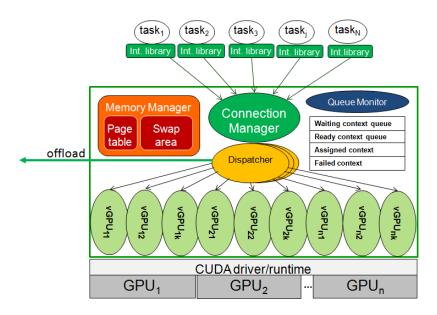

| Figure 3-4 – Overall design of the runtime4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6  |

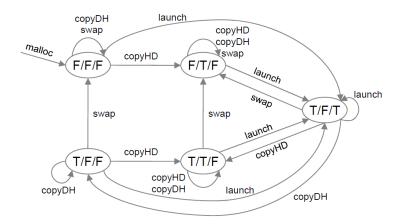

| Figure 3-5 – State diagram showing the transition of isAllocated/toCopy2Dev/toCopy2Swap flags                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2  |

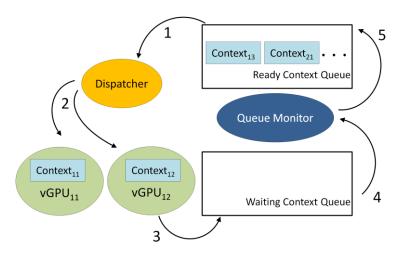

| Figure 3-6 – Preemption cycle6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2  |

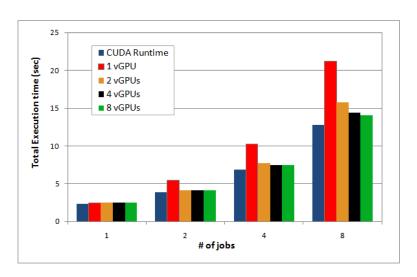

| Figure 3-7 – Execution time reported with a variable number of short-running jobs on a node with one GPU. The bare CUDA runtime is compared with our runtime                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6  |

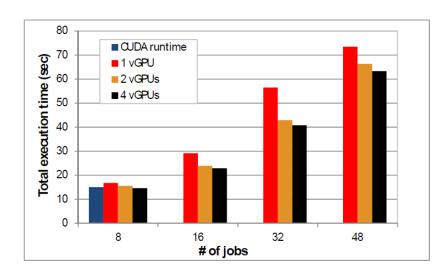

| Figure 3-8 – Execution time reported with a variable number of short-running jobs on a node with three GPUs. The bare CUDA runtime cannot handle more than eight concurrent                                                                                                                                                                                                                                                                                                                                                                        |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| jobs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 67 |

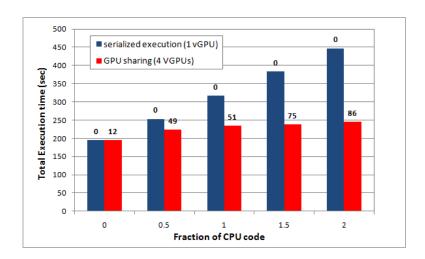

| Figure 3-9 – 36 <i>MM-L</i> jobs (with conflicting memory requirements) are run on a node with three GPUs. The fraction of CPU code in the workload is varied. We indicate the number of <i>swap</i> operations occurred on top of each bar                                                                                                                                                                                                                                                                                                        | 68 |

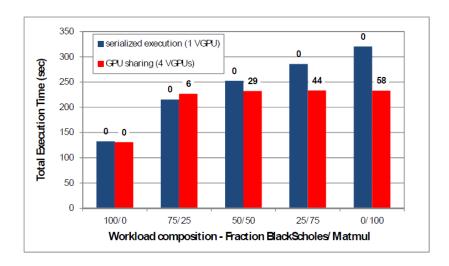

| Figure 3-10 – 36 jobs (BS-L and MM-L) are run on a node with three GPUs. The workload composition is varied. We indicate the number of <i>swap</i> operations that occurred on top of each bar.                                                                                                                                                                                                                                                                                                                                                    | 69 |

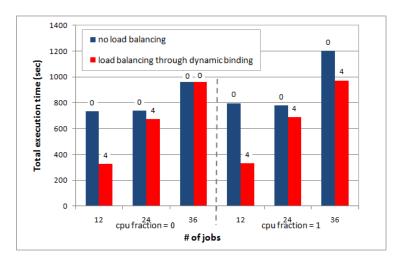

| Figure 3-11 – Unbalanced node with two Tesla C2050s and one Quadro 2000: effect of load balancing through dynamic binding. The number of <i>MM-S</i> jobs migrated to <i>fast</i> GPUs is reported on top of each bar                                                                                                                                                                                                                                                                                                                              | 70 |

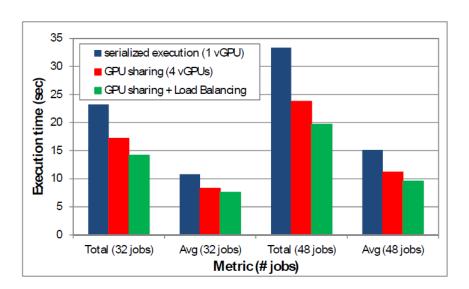

| Figure 3-12 – Two-node cluster using TORQUE: effect of GPU sharing and load balancing via inter-node offloading in the presence of short-running jobs and in the absence of conflicting memory requirements.                                                                                                                                                                                                                                                                                                                                       | 72 |

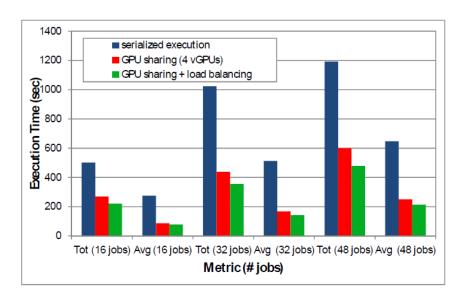

| Figure 3-13 – Two-node cluster using TORQUE: effect of GPU sharing and load balancing via inter-node offloading in the presence of long-running jobs and conflicting memory requirements.                                                                                                                                                                                                                                                                                                                                                          | 73 |

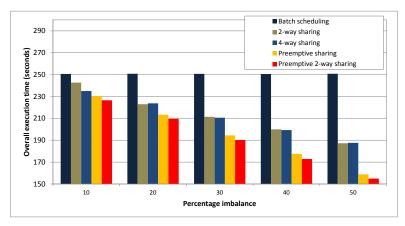

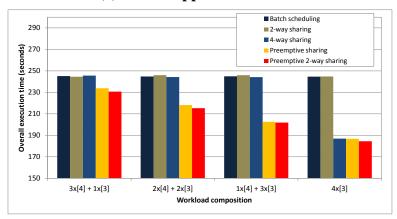

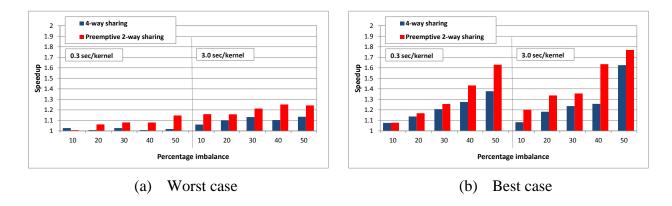

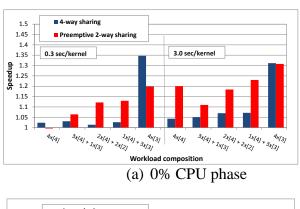

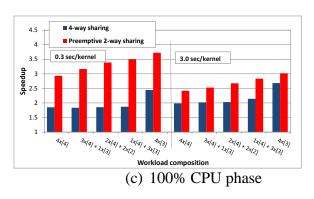

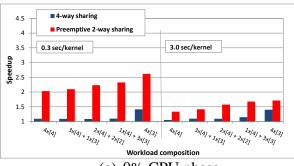

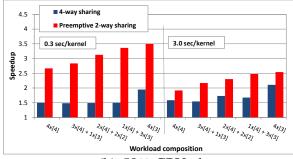

| Figure 3-14 – Preliminary experiments: comparison among five scheduling and sharing schemes for a 4-job workload including <i>all-to-all</i> communication primitives. In (5-a), each job consists of four processes, and the <i>GPU phase duration</i> parameter of one of these processes is higher than that of the other three by a factor <i>percentage imbalance</i> . In (5-b), workload composition $j_1 \times [p_1] + j_2 \times [p_2]$ indicates that $j_1$ jobs consist of $p_1$ processes and $j_2$ jobs consists of $p_2$ processes. | 79 |

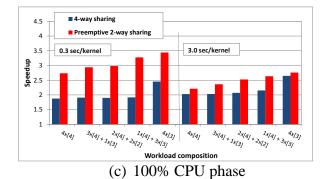

| Figure 3-15 Intra-application imbalancespeedup for broadcast communication pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 82 |

| Figure 3-16 Intra-application imbalancespeedup for scatter-gather communication pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 82 |

| Figure 3-17 Intra-application imbalancespeedup for barrier synchronization pattern                                                                                                                                                               | 82  |

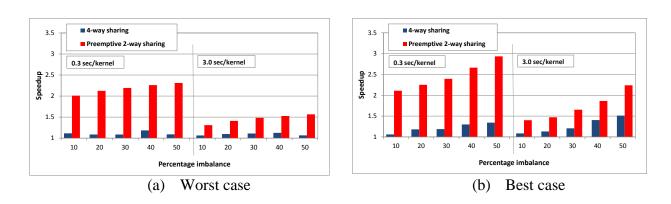

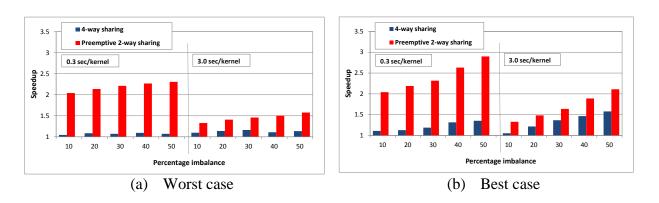

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 3-18 Inter-application imbalance speedup for broadcast pattern                                                                                                                                                                            | 83  |

| Figure 3-19 Inter-application imbalance speedup for scatter-gather pattern                                                                                                                                                                       | 83  |

| Figure 3-20 - Inter-application imbalance speedup for barrier pattern                                                                                                                                                                            | 84  |

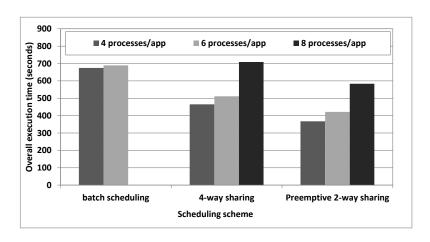

| Figure 3-21 Overall execution time in cluster settings                                                                                                                                                                                           | 88  |

| Figure 4-1 – Architecture of the cluster-level scheduler                                                                                                                                                                                         | 96  |

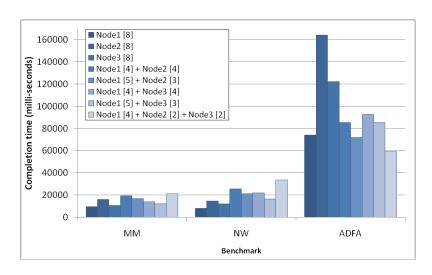

| Figure 4-2 – Performance of three benchmark applications running with 8 processes on different node configurations (from 1 to 3 nodes). Node <sub>i</sub> [j] indicates that j processes are run on Node <sub>i</sub>                            | 103 |

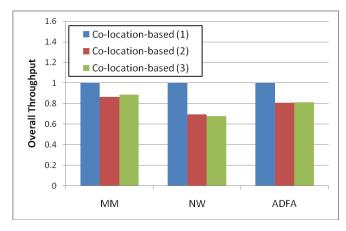

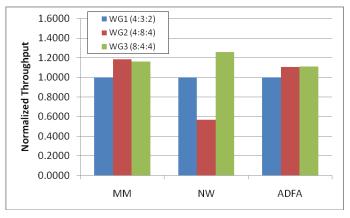

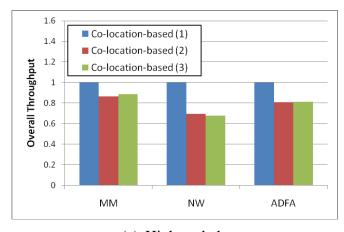

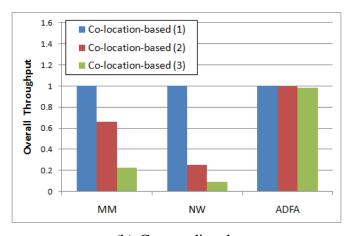

| Figure 4-3 – Co-location-based scheduler with relaxed constraints (1, 2 and 3 nodes/job allowed)                                                                                                                                                 | 113 |

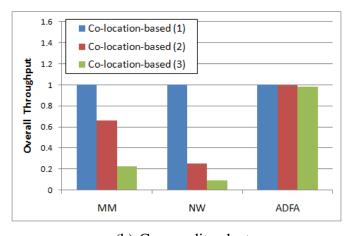

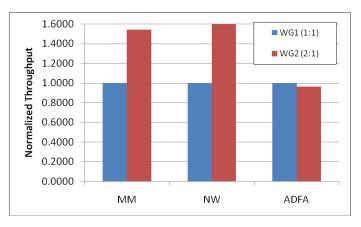

| Figure 4-4 – Throughput for different sets of weight assignments                                                                                                                                                                                 | 115 |

| Figure 4-5 – Overall throughput and QoS for the heterogeneous workload summarized in Table 4-5.                                                                                                                                                  | 117 |

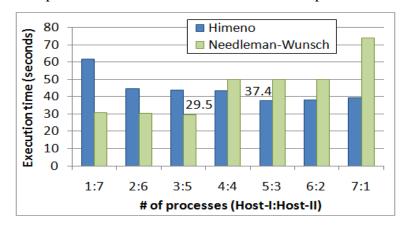

| Figure 5-1 – Overall execution time of MPI-CUDA implementations of the Himeno and Needleman-Wunsch benchmarks under different process-to-node assignments. In all cases, eight processes are run on two heterogeneous nodes (Host-I and Host-II) | 121 |

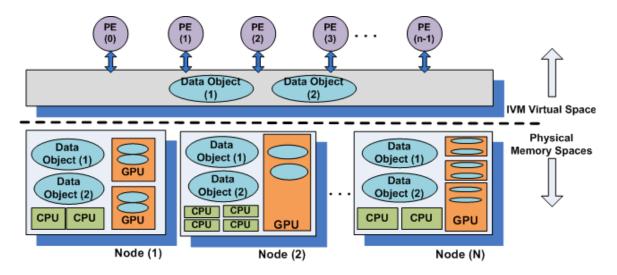

| Figure 5-2 – IVM's Execution and Memory Models                                                                                                                                                                                                   | 125 |

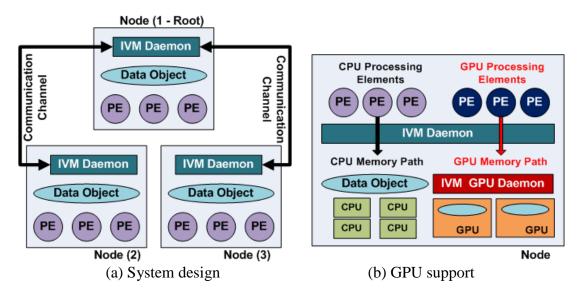

| Figure 5-3 – System design and GPU support                                                                                                                                                                                                       | 128 |

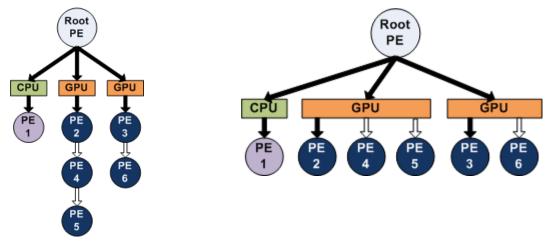

| Figure 5-4 – Graphical representation of load balancing schemes                                                                                                                                                                                  | 138 |

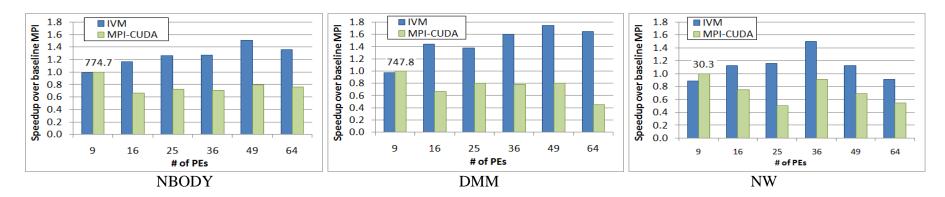

| Figure 5-5 – Speedup and load distribution in case of DS-LB                                                                                                                                                                                      | 144 |

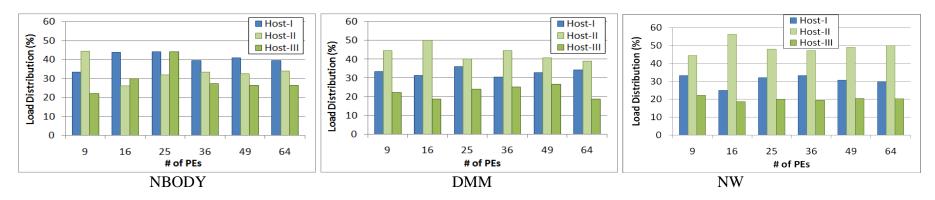

| Figure 5-6 – Execution time of HIMENO with OM-LB                                                                                                                                                                                                 | 148 |

# LIST OF TABLES

| Table                                                                                                                                                                                                                                  | Page |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Table 2-1 – Examples of MPI communication routines                                                                                                                                                                                     | 17   |

| Table 2-2 – Examples of SHMEM communication routines                                                                                                                                                                                   | 20   |

| Table 3-1 – For each routine issued, actions performed by the node-level scheduler and possible errors returned. A black in the third column indicates any error generated by the CUDA runtime (i.e. result ≠ cudaSuccess). VM_entry = | 5.4  |

| Virtual Memory Entry.                                                                                                                                                                                                                  | 4    |

| Table 3-2 – Benchmark programs                                                                                                                                                                                                         | 64   |

| Table 3-3 - Description and setting of the parameters of our benchmark generator                                                                                                                                                       | 75   |

| Table 3-4 – Characteristics of the nodes                                                                                                                                                                                               | 78   |

| Table 4-1 – Scheduling API                                                                                                                                                                                                             | 98   |

| Table 4-2 – Summary of benchmark characteristics                                                                                                                                                                                       | 108  |

| Table 4-3 – High-end cluster setup                                                                                                                                                                                                     | 111  |

| Table 4-4 – Commodity cluster setup                                                                                                                                                                                                    | 111  |

| Table 4-5 – Sequence of jobs submitted (the number of processes spawned is indicated in square brackets)                                                                                                                               | 116  |

| Table 5-1 – IVM Programming API                                                                                                                                                                                                        | 132  |

| Table 5-2 –Hardware setup                                                                                                                                                                                                              | 143  |

# HIERARCHICAL SCHEDULING AND UNIFORM ACCESS PROGRAMMING FRAMEWORKS FOR HETEROGENEOUS CPU-GPU COMPUTING CLUSTERS

# Kittisak Sajjapongse

## Dr. Michela Becchi, Dissertation Supervisor

#### **ABSTRACT**

The advance of the GPU hardware architecture has made GPUs attractive devices for general-purpose computing. Modern GPUs are equipped with an increasing number of cores, a flexible memory hierarchy, and a large memory capacity. While the computational power of modern GPU devices has allowed their introduction in high-performance computing (HPC) clusters and the efficient processing of ever larger workloads, existing software components for HPC clusters still offer basic support for hardware heterogeneity and often cause performance limitations in the presence of GPU devices. In particular, two kinds of limitations are associated with these software components: *runtime support* and *programmability*. We found that these limitations are due to the fact that existing software frameworks for heterogeneous clusters treat GPUs as dedicated coprocessor devices.

In this dissertation, we propose two software frameworks for addressing the performance and hardware underutilization issues found in heterogeneous CPU-GPU clusters as well as increasing their programmability. Our frameworks provide a uniform view of compute resources and treat CPUs and GPUs equally as first-class resources, allowing efficient management of heterogeneous compute resources. First, we propose a hierarchical scheduling framework consisting of a node-level runtime and a cluster-level scheduler that provides abstraction of heterogeneous compute resources at different granularities. This hierarchical framework targets existing applications and does not require their modification. In the node-level runtime, we identify and design mechanisms, such as *virtual GPUs*, *GPU virtual memory*, *dynamic load*

balancing and pre-emption, which are necessary to support efficient sharing and load balancing schemes for GPUs within a compute node. In the cluster-level scheduler, we introduce mechanisms to abstract compute nodes and perform load balancing in concert with the node-level runtime. Our hierarchical scheduling framework allows supporting different load balancing policies and does not require additional inputs (such as profiling information) from users. Second, we propose a programming framework based on a novel memory and execution model. Our memory model hides disjoint addressing spaces (corresponding to different CPUs, GPUs and compute nodes) and provides a view of a single virtual memory space that can be accessed by all compute resources in a heterogeneous cluster. Our execution model provides uniform access to compute resources and allows our framework to treat all CPUs and GPUs equally and to access data in the virtual memory space.

# CHAPTER 1

# INTRODUCTION

#### 1.1 Introduction

For decades, high-performance computing (HPC) has played a major role in pushing research toward answers and new discoveries. Challenging problems in science and engineering have traditionally been solved by simulation and analysis on highperformance computing platforms. Nowadays, the scale of the data used to solve many scientific problems has become significantly larger. As a consequence, the solution of these problems in a reasonable amount of time necessitates even more the aid of highperformance computing clusters. In the last decade, Graphic Processing Units (GPUs) have also been widely used to accelerate scientific and engineering computations. Thanks to their high computational power and low price-per-performance, these devices have gained popularity in the research community. The importance of GPUs is also emphasized by their adoption in the world's largest supercomputers [3]. However, GPUs have been originally intended as dedicated accelerators for simple applications and, therefore, their software stacks was not designed for use in shared computing environments, such as HPC clusters. The use of these software stacks in shared cluster environment causes resource underutilization and performance penalty/degradation.

In this dissertation, we analyze the inefficiencies due to the limitations of existing GPU software stacks and propose hierarchical scheduling frameworks to maximize both overall throughput of HPC clusters and performance of applications. Our frameworks enable dynamic load balancing by performing coarse- and fine-grained scheduling of loads to resources. In the first part of our work, we study the limitations of current software support for GPUs and propose a hierarchical scheduling framework to dynamically schedule applications to compute resources without requiring modifications to the applications. In the second part of our work, we address the inefficiencies of existing programming models for CPU-GPU clusters and propose a programming model that can be supported by a runtime framework, including the resource sharing and scheduling mechanisms that we have identified. Our ultimate goal is to enable applications to exploit fully the hardware capabilities as well as increase programmability of heterogeneous clusters consisting of CPUs and GPUs.

#### 1.2 Motivations

Over the last decade, many-core devices (such as GPUs) have been widely used to accelerate a variety of applications [4-6]. In its online catalog [7], Nvidia lists about 200 GPU-accelerated applications from different domains, including computational chemistry, biology, physics, numerical analytics, weather prediction, computational finance and data mining. The popularity of GPUs is emphasized by their increased use in HPC clusters: as of November 2013, four of the top 10 fastest supercomputers in the world [3] (Tianhe-2, Titan, Piz-Daint and Stampede) are equipped with Nvidia GPUs.

Existing resource management framework for CPU-GPU clusters, such as TORQUE and SLURM, rely on traditional software stacks like CUDA and OpenCL.

These software stacks, however, were designed viewing GPUs as dedicated accelerators, and lack good support for their use in multitenant environments. The use of existing frameworks in heterogeneous clusters can lead to performance and hardware underutilization issues. In the following sections, we discuss these issues in more detail.

#### 1.2.1 Software support for GPUs

Current software stacks for GPU applications, such as CUDA, view GPUs as dedicated accelerators. Applications relying on these software stacks explicitly acquire GPUs, manage them and perform computations on them. The accelerator model views CPUs as *hosts* and GPUs as *devices* where the host handles general tasks including managing GPUs and offloads only major computations to GPU devices. Most GPU applications, therefore, alternate between CPU and GPU phases. The common structure of GPU applications is the following. First, data is initialized and pre-processed on CPU. The CPU then offloads the computation to GPU after the initialization is complete. After the GPU completes the computation, the CPU gathers the results from the GPU and possibly performs post-processing on the results. Since the CUDA runtime also requires applications to explicitly select the GPUs for their computation, the CUDA runtime binds applications to the selected GPUs. The binding between an application and a GPU is static that implies that the application data will only reside on the selected GPU and the computation will be offloaded only to that GPU for the entire lifetime of the application.

This computational model has several issues. First, it is obvious that the alternation between CPU and GPU phases leads to hardware underutilization because either CPU or GPU will be utilized in each phase causing the other type of resource to be idle. A remedy to this issue is to utilize both CPU and GPU for the computation.

However, this utilization comes at the cost of a complex implementation since it requires judicious load balancing between CPUs and GPUs. Second, the explicit GPU procurement can be problematic in the presence of concurrent applications. In a shared environment, each application is not aware of the existence of other applications, possibly leading to resource contention. For example, it is possible that applications may collectively select the same GPU and thus overload it while leaving other GPUs idle. In a shared environment, a resource manager is required to distribute applications to GPUs in a harmonious manner in order to avoid interference between applications. Explicit procurement of GPUs may not be suitable to shared environments since it limits the ability to dynamically distribute the application load to the available GPU devices. Finally, static binding of applications to GPUs may limit the ability to manage GPUs and to perform load balancing at run-time [1]. In one scenario, as an example, a GPU application may be mapped to a GPU with low performance capability due to the temporary unavailability of GPUs with high performance capability. To maximize performance, this application should be moved to a GPU with higher capability as soon as it becomes available. However, static binding prevents dynamic migration of applications among the available GPUs. In another scenario, an application may bind to a specific GPU and store its data on that GPU. However, if the CPU phase of the application is significantly long, the application is binding to the GPU without utilizing the GPU well and also limits the possibility for other applications to use the GPU. This kind of GPU underutilization is particularly problematic for applications with long CPU phases or distributed applications that perform communications frequently. This problem may be avoided by preempting applications [2].

#### 1.2.2 Resource Managers

Traditional frameworks were designed to manage homogeneous clusters and can be inefficient for heterogeneous clusters in term of utilization and performance. Most widely adopted resource managers and cluster schedulers, such as TORQUE [8] and SLURM [9], were designed to target homogeneous clusters. With the increasing popularity of GPUs, they have recently been extended to handle accelerators such as GPUs. Since they mostly rely on software stacks intended for dedicated setting to provide GPU supports, these systems lead to suboptimal throughputs and underutilization.

State-of-the-art resource managers accept resource requests (i.e. CPUs/GPUs, RAM, disk space, network traffics etc.) from users and distribute the load at a coarsegrain by mapping applications to nodes according to the requests and current system load. Once an application is assigned to a node, the assignment is static; and the application will execute on the same set of nodes for its entire lifetime. This design leads to two issues that can cause inefficiencies in heterogeneous clusters. First, the user will need to have some knowledge on the configuration of the cluster to make resource requests to the resource managers [10]. For example, users will need to identify the nodes with GPUs and determine the number of GPUs available on each of the nodes in order to make requests. Second, the coarse-grained mapping of applications to nodes and the finegrained mapping of applications processes to GPUs are static. Load balancing between heterogeneous nodes can be difficult with current resource managers since they do not account for heterogeneity. Under heterogeneous clusters, the amount of load each node will handle is determined by the performance capability of the node prior to applicationto-node mapping/scheduling [10]. This maneuver can be cumbersome to users since they

have to estimate good hardware configurations for their applications in order to make requests to the resource managers. In addition, load balancing is not possible since these resource managers do not directly manage GPUs inside nodes.

In addition, state-of-the-art resource managers offer very limited support for resource sharing, and this support is generally limited to CPU resources. Coarse-grained space sharing is extensively studied with this type of resource managers [11-13]. Backfilling is one of the mechanisms proposed to reduce application latency and improve quality-of-service (QOS) for users. Although some coarse-grained space-sharing policies can be defined within the resource managers, hardware utilization of both CPUs and GPUs can be poor. To understand how space-sharing can be inefficient in current systems, consider an application requesting resources leaving free resources in the cluster that cannot be used to accommodate subsequent requests. For example, suppose we have a cluster consisting of seven nodes with three GPUs on each of the nodes. Three applications request three nodes with eight GPUs each. In this case, the resource managers will allow only two applications to proceed and leave five GPUs and one node idle. This situation can be inefficient since the third application submitted needs to wait for the first two applications to complete before being able to proceed. This causes the latency of the application to increase and the cluster to be underutilized. It is worth noting that existing resource managers do not allow fine-grained space-sharing or time-sharing of a single GPU across applications. Currently, only little study has been conducted on time-sharing resources in clusters. Time-sharing can be a mechanism to improve hardware utilization and, as a result, the quality of service of applications. In the previous example, a resource manager with time-sharing enabled will allow the third application to

execute concurrently with the other two. For example, the third application can be assigned to nodes such that six of its tasks time-share a set of GPUs on these nodes. The application can even be assigned entirely to a single node (the one remaining after mapping the first two applications) to limit application interference. Time-sharing can, however, produce negative effects, such as interference between applications or unexpected performance degradation. A careful study of time-sharing resources in heterogeneous clusters must be conducted to maximize performance, utilization, and quality-of-service.

## 1.2.3 Programmability

Heterogeneous clusters can include CPUs and GPUs with different compute capabilities. Not only does this complicate resource scheduling, but it also requires significant development effort since complex architectural details such as disjoint memory spaces are exposed to programmers. For example, it is necessary for programmers to explicitly manage copies of data on separate nodes and GPUs. In addition, GPUs are viewed as discrete accelerators that are explicitly managed by CPUs. As a consequence, CPUs and GPUs are not accessed in a uniform way. These factors complicate programming of heterogeneous clusters with GPUs.

The development of distributed GPU applications requires a good knowledge of parallel programming at different levels, i.e. inter-node, intra-node, and intra-GPU levels. At the inter-node level, programming models such as MPI and SHMEM are used to support communications between nodes. Programmers need to determine the best communication pattern to achieve the lowest communication latency given a particular system configuration. However, these programming models do not handle alone GPUs.

At the intra-node level, programmers need to mange consistency between copies of data on CPUs and GPUs and judiciously orchestrate the computation. Since each CPU and GPU device has its own physical memory, the clusters are also characterized by a distributed memory system. Lastly, the differences in architectural details among different types of CPUs and GPUs must be carefully taken into account to achieve peak performance. While programming techniques and optimizations for compiler and runtime support for homogeneous CPU systems/nodes are mature, application development on GPUs does still require significant programmer effort. Not only do programmers need to write massively parallel codes, but they need also to deal with complex memory system [14].

Hybrid programming models can be used for developing distributed GPU applications. For example, MPI-CUDA or SHMEM-CUDA can be employed to distribute load between nodes and allow applications to use GPUs on each node. In the presence of heterogeneity, judicious load placement is necessary to avoid performance and underutilization issues. Load balancing can be complex using these hybrid programming models; programmers must implement load balancing schemes at different granularities, i.e. inter-node and intra-node. In our previous work, we have developed a hierarchical load balancing for massive sequence alignments on heterogeneous clusters with GPUs [15]. At the inter-node level, we have implemented a load balancing scheme based on the producer-consumer model and used MPI for inter-node communication. At the intra-node level, we have used multithreading and CUDA streams [14] to manage computations on multiple CPUs and GPUs with different performance capabilities. However, the resulting application complexity is not trivial.

In summary, existing CPU-GPU clusters lead to issues in terms of programmability and runtime support. This dissertation addresses both problems.

#### 1.3 Contributions

In this dissertation, we make the following contributions:

#### 1.3.1 Runtime Supports for Distributed GPU applications

We propose a node-level runtime component that provides runtime support for GPU applications. We identify virtual memory for GPUs and GPU virtualization as essential mechanisms to abstract physical GPUs from users, provide dynamic load balancing, and improve application performance and system utilization. Our node-level runtime provides mechanisms such as *dynamic binding* of applications and *GPU preemption* to enable dynamic load balancing across concurrent applications. These mechanisms efficiently manage applications even in the presence of CPUs and GPUs with different compute capabilities. In addition, our node-level runtime supports dynamic load balancing in case of GPU addition and removal, resilience to hardware failure, and checkpoint-restart capabilities. Our node-level runtime supports different scheduling policies.

#### 1.3.2 Hierarchical Resource Management

We propose a cluster-level scheduler for heterogeneous systems and integrate it with our proposed node-level runtime to form a hierarchical scheduling framework. This hierarchical framework allows better utilization of heterogeneous CPU-GPU clusters by judiciously distributing the load at different levels. At the coarse-grain, applications are distributed to different nodes. At the fine-grained, the node-level runtime dynamically distributes tasks to GPUs. Our cluster-level scheduler is configurable and allows administrators to easily define custom scheduling policies to meet specific requirements

related to cluster setup, applications characteristics, and the users' needs. This hierarchical scheduling framework operates on unmodified CPU-GPU binaries and transparently schedules application and dynamically performs load balancing without the user intervention. We show the effectiveness of the proposed scheduling framework on a variety of workloads.

#### 1.3.3 Programming Framework for Uniform Resource Access

We propose a novel programming framework based on the shared memory model to improve programmability and enable efficient scheduling of application in heterogeneous clusters with GPUs. Our programming framework reduces complexity in development of distributed applications by providing uniform view of the memory space and resources with a heterogeneous cluster. We propose a programming framework called Inter-node Virtual Memory (IVM) that provides the programmer with a uniform view of compute resources and memory spaces within a CPU-GPU cluster, and a mechanism to easily incorporate load balancing within the application. We compare the use of MPI and IVM on four distributed CUDA applications. While the main goal of IVM is programmer productivity, the use of the load balancing mechanisms offered by IVM can also lead to performance gains.

# 1.4 Organization

The rest of this dissertation is organized as follows. Chapter 2 provides a background on programming models and runtime systems for heterogeneous clusters. Chapter 3 describes our node-level runtime for GPU applications. Chapter 4 describes the cluster-level scheduler that we have designed and its integration with our runtime component to form a hierarchical scheduling framework. In Chapter 5, we then describe a novel

programming framework to enable unified programming and facilitate the coding of applications embedding dynamic load balancing in heterogeneous clusters with GPUs. Finally, we provide future directions for the current research in chapter 6.

# **CHAPTER 2**

# **BACKGROUND & RELATED WORK**

## 2.1 Background

## 2.1.1 Graphic Processing Units (GPUs)

Graphics Processing Units (GPUs) have been traditionally used to accelerate image/video processing applications and 3D-games. These platforms have a highly parallel architecture consisting of a large number of processing cores since they were originally designed to handle a large number of pixels concurrently. Current software stacks for GPUs also enable more general purpose computations such as scientific and engineering applications to utilize these devices.

GPUs are generally used as accelerator devices (or coprocessors). The host CPU handles general parts of the application, such as book-keeping, pre-/post-processing, and I/O interface, and offloads compute intensive tasks to the GPUs. Because GPUs have their own memory space, memory transfers between the host CPU and the GPUs are

Figure 2-1 – Memory model between CPUs and GPU

necessary to enable communication between them. Figure 2-1 shows the memory configuration of a hybrid CPU-GPU node. Both CPUs and GPUs have their own disjoint physical memory spaces and they can communicate and exchange data by copying memory content back and forth. Memory transfers are usually performed by a Direct Memory Access (DMA) engine to allow fast transfer and low CPU overhead. The most common scenario in a CPU-GPU interaction is the following. First, the host CPU initializes the datasets and data structures its own memory space (CPU memory). Once this initialization is complete, these data are transferred to the memory space belonging to the GPUs (GPU memory). The CPU can then initiate the computation on the GPUs. The results may finally be transferred from the GPU to the CPU memory for further processing or report generation.

The Compute Unified Device Architecture (CUDA) [16] and Open Computing Language (OpenCL) [17] are well known frameworks for creating GPU applications.

Figure 2-2 – GPU architecture under CUDA framework

These frameworks define the computation and memory models for GPUs. They consist of a runtime library and a compiler. It is worth noting that, while CUDA targets only GPUs, OpenCL also targets other types of accelerators such as FPGA. Since, in this dissertation, we will consider only GPUs, we will mostly refer to CUDA and use terminology defined by this framework. Figure 2-2 shows the high-level architectural details of GPUs under CUDA. A GPU consists of a collection of Streaming Multiprocessors (SMs), which share the same global memory space. The global memory space was earlier referred to GPU memory wherein data from the CPU memory can be stored. A group of SMs share an L2-cache which is fully controlled by the hardware. A SM consists of a collection of scalar cores or SIMD-lanes which share a register file, an L1cache, and one or more instruction fetch units. Since the cores share the same instruction fetch units, they process instruction in lock-step. However, while all cores execute the same instruction, operands for the instruction at a time step can be different which each of them operates on different data. The register file and L1-cache are the storage areas with the lowest access latency. The L1-cache can partially be programmatically configured as shared memory. Shared memory allows software to manage the content of the memory whereas L1-cache is managed by the hardware. Programmers can, therefore, decide what kind of data to be put in the shared memory.

# 2.1.2 Programming Models for Heterogeneous Clusters

In a heterogeneous cluster, multiple compute nodes cooperate to process distributed applications submitted by users. A compute cluster usually consists of a *head node*, which acts as a frontend interface for submitting applications. A resource manager or scheduler usually run on the head node and distributes tasks to the other compute nodes.

Tasks within a distributed application usually communicate with each other. Therefore, tasks on different nodes will cooperate and exchange data. Task execution can be broken into two phases: *computation phase* and *communication phase*. Tasks perform computation independently on CPU or GPU in the computation phase; they communicate and exchange data in the communication phase. Tasks will alternate between the two phases for the entire lifetime of the application. Compute nodes in clusters are commonly connected through either Ethernet networks [18] or Infiniband fabrics [19]. The networks enable compute nodes to exchange data based on relationships and dependencies between tasks.

Ethernet is the most common network technology used in both commodity and high-end clusters. Ethernet offers a reliable stream-based connection for a pair of nodes. All modern operating systems include *socket API* as a programming interface to implement point-to-point communication between nodes through send (*send*) and receive (*recv*) methods. The communication method based on send and recv is called *two-sided communication* since it requires the participation of the sending and receiving side. The correct operation of two-sided communication is guaranteed when information sent from the sending side is acknowledged by the receiving side. Complex communication routines that involve more than two nodes can also be implemented using the socket API.

Infiniband fabric is mostly deployed in high-performance computing clusters. The goal of this network technology is to provide messaging service between nodes without the intervention of the operating system in order to achieve low-latency communication and reduce CPU overhead. Under Unix-based operating systems such as Linux, this allows applications to interface with the network adaptor directly from user-space and

bypass the kernel-space. In addition to the two-sided communication, Infiniband also offers a communication method that allows nodes to directly read from and write to memory locations of remote nodes. This method is technically known as Remote Memory Direct Access (RDMA), and it is used to implement remote read/write (*rem-rd*, *rem-wr*) operations. This communication method is also called *one-sided communication* because only one party will need to complete the information exchange while the other end is free to perform other tasks. This communication method allows communication and computation phases of tasks to execute concurrently in a more efficient manner. Infiniband fabrics also allow nodes to perform atomic operations (e.g., atomic increments and compare-and-swap) on a memory location of a node. Programmers can implement their distributed applications on Infiniband fabric through the Verbs API.

Implementing distributed applications directly on Socket or Verbs is an extremely difficult and challenging task requiring a large development and debugging effort. Most distributed applications in science and engineering are written using programming frameworks based on the Socket or the Verbs API. These frameworks facilitate communication between tasks and allow programmers to easily implement work-distribution methods. The most widely used programming models for distributed applications include the Message-Passing-Interface (MPI) and Partitioned Global Address Space (PGAS). These programming models employ the two communication methods mentioned above. In particular, MPI employs two-sided communication while PGAS mainly employs one-sided communication. These programming models are described in more detail in the next sections.

# 2.1.3 Message-Passing Interface (MPI)

Message-Passing-Interface (MPI) defines a standard for creating distributed applications based on the message-passing paradigm. Tasks in a distributed application communicate by exchanging messages. In many MPI implementations, such as OpenMPI [20], MPICH2 [21], and MVAPICH2 [22], tasks are distributed to nodes in the form of processes managed by the local operating system. These processes can run on the same or different nodes, and each has an identification number called *rank*. These processes do

| MPI routines    | Descriptions                                                                                                            | Type         |

|-----------------|-------------------------------------------------------------------------------------------------------------------------|--------------|

|                 | Point-to-point communication                                                                                            |              |

| MPI_Send()      | Sends a message to a specific rank.                                                                                     | Blocking     |

| MPI_Recv()      | Receives a message from a specific rank.                                                                                | Blocking     |

| MPI_Isend()     | Sends a message to a specific rank in an unblocking manner.                                                             | Non-blocking |

| MPI_Irecv()     | Receives a message from a specific rank in an unblocking manner                                                         | Non-blocking |

| MPI_Testall()   | Tests for the completion of all previously initiated communications. This is useful especially for unblocking routines. | Non-blocking |

| MPI_Waitall()   | Waits for all given communication to complete. This is useful especially for unblocking routines.                       | Blocking     |

|                 | Collective communication                                                                                                |              |

| MPI_Gather()    | Gathers together values from a group of processes.                                                                      | Blocking     |

| MPI_Allgather() | Gathers data from all tasks and distributes it to all.                                                                  | Blocking     |

| MPI_Scatter()   | Sends data from one task to all other tasks in a group.                                                                 | Blocking     |

| MPI_Reduce()    | Reduces values on all processes to a single value.                                                                      | Blocking     |

| MPI_Allreduce() | Combines values from all processes and distributes the result back to all processes.                                    | Blocking     |

| MPI_Alltoall()  | Sends data from all to all processes.                                                                                   | Blocking     |

| MPI_Barrier()   | Blocks until all processes have reached this routine.                                                                   | Blocking     |

| MPI_Bcast()     | Broadcasts a message from the process with rank "root" to all other processes of the group.                             | Blocking     |

**Table 2-1 – Examples of MPI communication routines**

not share memory address spaces or data structures. Each process has its own memory space. Therefore, information exchange only occurs by transferring memory content from one process to another. MPI provides various communication routines implementing point-to-point, one-to-many, many-to-one, or many-to-many communication. The routines involving more than two parties are known as *collective communication* primitives. MPI collective communication primitives implement two-sided communication.

Table 2-1 summarizes the MPI calls for exchanging information among processes. These communication primitives are divided into point-to-point and collective communication routines. These primitives can either be blocking or non-blocking. A blocking routine waits until the communication is complete; a non-blocking routine immediately returns even if the communication is not complete. The non-blocking routines allow a process to post communication requests to the MPI framework while performing other computation or communication tasks in parallel. Programmers can test the completion of non-blocking communication routines by issuing MPI\_Testall() or MPI\_Waitall() calls. The blocking nature of some collective communication routines can be performance bottleneck and cause other performance issues, which will be described in more detail throughout this dissertation.

#### 2.1.4 Partitioned Global Address Space (PGAS)

Partitioned Global Address Space (PGAS) is a programming model for distributed applications that provides a shared-memory abstraction to some degree. In PGAS, tasks are distributed as units called *Processing Elements (PEs)*, which execute in parallel either on the same or on different nodes. PGAS provides a memory model similar to the Non-

Uniform Memory Access architecture (NUMA) wherein the entire memory address space consists of multiple memory regions that are local to different PEs. Each PE has a local region that is divided into two sections. The first section of the region is called private section and can only be accessed by that PE. Examples of variables residing in the private section include local variables that appear in functions or loops, non-static variables and variables or memory regions that are dynamically allocated. The other section is called symmetric region and accesses to it from other PEs are allowed. During execution, PEs can exchange information using the one-sided communication by writing to and reading from memory locations in symmetric sections. The symmetric section includes static variables, global variables, and symmetric heap. The symmetric heap is the central heap that a PGAS programming framework can use to dynamically allocate variables from a PE and allows other PEs to access the variables. Variables residing in the symmetric heap of each PE are called symmetric objects and can be remotely written or read by the other PEs. All PEs have different copies of a symmetric object; these copies will have the same data type and size but may contain different contents. There are several well-known implementations of the PGAS model: Unified-Parallel-C, Co-Array Fortran, and SHMEM. Unified-Parallel-C and Co-Array Fortran use compiler-techniques and provide extensions to standard programming languages (C/Fortran). Such frameworks provide a set of PGAS-enabled compilers, linkers and runtime support for distributed applications. SHMEM is library-based and allows programmers to create distributed applications using generic compilers. SHMEM provides more flexibility and portability by allowing applications to be written in different programming languages. Recently, SHMEM has gained popularity in the high-performance computing community. This framework was

| SHMEM Routines         | Descriptions                                                  |

|------------------------|---------------------------------------------------------------|

|                        | Point-to-point communication                                  |

| shmem_putmem()         | Copies data from a contiguous local data object to a data     |

|                        | object on a specified PE.                                     |

| shmem_getmem()         | Copies data from a data object on a specified PE to a         |

|                        | contiguous local data object.                                 |

|                        | Atomic operations                                             |

| shmem_int_add()        | Performs an atomic addition operation on a remote data        |

|                        | object of a specified PE.                                     |

| shmem_int_cswap()      | Performs an atomic conditional swap on a remote data          |

|                        | object of a specified PE.                                     |

| shmem_int_inc()        | Performs an atomic increment operation on a remote data       |

|                        | object of a specified PE.                                     |

|                        | Collective communications                                     |

| shmem_barrier()        | Registers the arrival of a PE at a barrier and suspends PE    |

|                        | execution until other PEs arrive at the barrier and all local |

|                        | and remote memory updates are completed.                      |

| shmem_broadcast32/64() | Broadcasts a block of data from one PE to one or more         |

|                        | destination PEs.                                              |

| Shmem_collect32/64()   | Concatenates blocks of data from multiple PEs to an array     |

|                        | in every PE.                                                  |

**Table 2-2 – Examples of SHMEM communication routines**

originally designed to take advantage of the RDMA mechanism offered by Infiniband interconnects. SHMEM implementations are available from various manufacturers such as SGI, Mellanox and OpenSHMEM. OpenSHMEM is an open source specification of SHMEM created in a standardization effort. The OpenSHMEM library implements communication routines as a set of function calls included in the Application-Programming-Interfaces (APIs). These communication routines are implemented in the form of remote writes and reads called *Put* and *Get* methods respectively.

Many frameworks, such as Unified Parallel C (UPC) [23], Co-Array Fortran [24] and SHMEM [25], are based on the PGAS programming model. In this dissertation, we will mainly refer to the SHMEM programming model and OpenSHMEM [26] as a

specific implementation of it. Table 2-2 shows a set of OpenSHMEM communication routines. Similarly to MPI, communication routines are also divided into point-to-point and collective routines; and they are based on the one-sided communication paradigm. In addition, the nature of one-sided communication allows atomic routines on variables residing in the symmetric address space.

#### 2.2 Related Work

#### 2.2.1 Node-level Schedulers and Runtime Support

A number of previous studies have proposed node-level techniques and mechanisms for heterogeneous nodes to improve individual performance of applications or aggregated performance and utilization of CPUs and GPUs in clusters. These proposals can be divided into two categories according to the types of applications considered. The first category includes scheduling and virtualization frameworks for single-process GPU applications, where the second covers more complex, distributed applications.

GViM [27], vCUDA [28], rCUDA [29] and gVirtus [30] are runtime systems to enable GPU applications in virtualized environments. These frameworks provide GPU visibility from within virtual machines by using API remoting to submit computation requests for GPUs from guest OS to host OS. GViM and vCUDA leverage the multiplexing mechanism provided by the CUDA runtime in order to allow GPU sharing among different applications. GViM uses a Working Queue per GPU to evenly distribute the concurrent applications to GPUs. As additional feature, GViM provides a mechanism to minimize the overhead of memory transfers when GPUs are used within virtualized environments. In particular, its authors propose using the *mmap* Unix system call to avoid data copies between the guest OS and the host OS. Whenever possible, they also propose

using page locked memory (along with the cudaMallocHost primitive) in order to avoid the additional data copy between host OS and GPU memory. Gelado et al., [31] and Becchi et al., [32] explored GPU abstraction by providing memory-management frameworks for nodes including CPUs and GPUs. These frameworks abstract the underlying distributed memory spaces of CPUs and GPUs and provide a uniform view of the memory space. This eliminates the need for programmers explicitly to transfer memory content between CPUs and GPUs. As optimization, their frameworks also avoid some unnecessary memory transfers.

GPU sharing can be used to improve hardware utilization. Guevara et al., [33] proposed kernel consolidation as a way to share GPUs. They showed that this mechanism is particularly effective in the presence of kernels with complementary resource requirements (e.g.: compute intensive and memory intensive kernels). The concept of kernel consolidation has been reconsidered and explored in the context of GPU virtualization by Ravi et al., [34].

In term of balancing loads across GPUs, our work differs from GViM [27] and vCUDA [28]. These node-level schedulers statically assign applications to GPUs, which can lead to suboptimal performance--especially in the presence of heterogeneity. Our node-level scheduler provides GPU abstraction and enables dynamic scheduling and effective GPU sharing mechanisms. In addition, we designed our framework to allow administrators to implement different load balancing policies in the scheduler. Our GPU sharing mechanism differs from GViM [27], Guevera et al., [33], and Ravi et al., [34]. These proposals allow applications to share GPU based on the assumption that the aggregated memory requirements of applications sharing the same GPU does not exceed

the memory capacity of the GPU. Our scheduler targets multi-tenant environments even in the presence of conflicting memory requirements among applications. On one hand, the memory module we designed has some similarities with the frameworks described by Gelado et al., [31] and Becchi et al., [32]. On the other hand, it extends these frameworks and focuses on multi-tenant scenarios. Some optimizations such as zero-copy memory transfer proposed by GViM [27] are orthogonal to our work and can also be incorporated in our scheduler.

#### 2.2.2 Cluster-level Schedulers and Resource Sharing

Scheduling and resource sharing for distributed applications have been extensively studied. A number of previous studies proposed co-location strategies, such as Gang-Scheduling [35, 36], and Co-Scheduling [37-45], for distributed applications to share resources under homogeneous environments. Some of these frameworks allow applications to share resources so as to avoid interference [46, 47]. The primary goal of these frameworks is to both maximize CPU utilization and performance of individual applications.

Gang-scheduling is a scheduling scheme that aims to minimize the cost of communication among tasks belonging to the same application. This scheduling scheme reduces communication latency by scheduling all tasks to compute resources at the same time, thus reducing the latency incurred by context-switching. Gang-scheduling allows time-sharing to concurrent applications by preempting all the tasks of the same application and yielding compute resources to another application. Feitelson et al., [35] presented a performance evaluation of gang-scheduling in shared-memory systems. Hori et al., [36] proposed an implementation of gang-scheduling across nodes in a cluster.

Since gang-scheduling makes scheduling decisions across all participating tasks, it assumes that all tasks communicate at the same time slot. This situation does not hold for point-to-point communication. In fact, it may incur unnecessary synchronization overhead in the presence of large number of tasks and has limited scalability.

Several proposals [37, 39, 41, 43, 44] have proposed more scalable and efficient co-scheduling schemes aimed at reducing inter-process communication. In particular, Arpaci-Dusseau et al., [39] proposed communication-based co-scheduling. In their scheme, information such as the response time and the type of communication among the processes in a parallel application is used to guide scheduling and sharing decisions. Choi et al., [43] proposed a co-scheduling scheme that blocks processes involved in point-to-point communication and tries to co-schedule processes that perform collective communication. Sobalvarro et al., [44] describe spin-block communication in which communicating tasks spin for a predefined period and then block if the communication is not completed within such period. However, all the aforementioned studies target only homogeneous environments including only multi-core CPUs, and do not address performance and utilization issues faced in heterogeneous environments. Further, no effort has been made to extend these works to enable scheduling of distributed applications on clusters with GPUs.

Existing scheduling frameworks such as TORQUE [8] and SLURM [9] are the most common cluster resource managers used in supercomputing centers, such as Texas Advanced Computing Center (TACC) [48]. These tools have been recently extended with the GPU support capabilities. Although these tools do not allow time-sharing of resources, they use back-filling to allow space-sharing of resources including GPUs [11-