# EXPLORING THE CHARGE STORAGE PROPERTIES OF SUB-2 NM METAL NANOPARTICLES —APPLICATIONS IN FIELD EFFECT TRANSISTOR MEMORY AND DETECTION OF TRACE VAPOR MOLECULES

\_\_\_\_\_

#### A Dissertation

presented to

the Faculty of the Graduate School at the University of Missouri

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy

\_\_\_\_

by

HAISHENG ZHENG

Shubhra Gangopadhyay, Supervisor

July 2016

The undersigned, appointed by the dean of Graduate School, have examined the dissertation entitled

# EXPLORING THE CHARGE STORAGE PROPERTIES OF SUB -2 NM METAL NANOPARTICLES —APPLICATIONS IN FIELD EFFECT TRANSISTOR MEMORY AND DETECTION OF TRACE VAPOR MOLECULES

| Presented by Ha | aisheng Zheng,                                         |

|-----------------|--------------------------------------------------------|

| A candidate for | the degree of doctor of philosophy                     |

| and hereby cert | ify that, in their opinion it is worthy of acceptance. |

|                 |                                                        |

| <u>-</u>        |                                                        |

|                 | SHUBHRA GANGOPADHYAY                                   |

|                 |                                                        |

| -               | WENTH AND HAVE WORKEN THE                              |

|                 | VENUMADHAV R. KORAMPALLY                               |

|                 |                                                        |

| -               | JOHN M GAHL                                            |

|                 | JOHN W GARL                                            |

|                 |                                                        |

| -               | SATISH S NAIR                                          |

|                 |                                                        |

|                 |                                                        |

| -               | CADSTENTILLDICH                                        |

## **DEDICATION**

I wish to dedicate this work to my loving parents, my brothers and sisters, and my wife Biyan Chen. Their love and company has always been my motivation and support for the exploration of life and science. Thank you.

#### **ACKNOWLEDGEMENTS**

I sincerely thank my doctoral committee chair and research supervisor, Prof. Shubhra Gangopadhyay, for giving me the opportunities to work in her research group on these very interesting projects and for providing excellent guidance and advice throughout my time in her group. Without her dedication, this work would not have been possible. Throughout my doctoral study, she's the one who motivates me to see the beauty of science, teaches me how to think out of the box and work in a team, but most importantly, how to become a better person.

I also graciously thank my other doctoral committee members, Prof. Venumadhav R. Korampally, Prof. John M. Gahl, Prof. Satish S. Nair and Prof. Carsten Ullrich for their guidance and helpful discussions.

It would have been nearly impossible for me to reach this point without the help and support provided by my current and previous mentors and group members: Dr. Korampally, Dr. Keshab Gangopadhyay, Dr. Minseong Yun, Dr. Ramalingam Balavinayagam, Dr. Mukjee Somik, Dr. Mathai C. Joseph, Dr. Bok Sangho, Biyan Chen and all my other colleagues.

## TABLE OF CONTENTS

| ACKN(   | OWLEDGEMENTS                                                            | ii    |

|---------|-------------------------------------------------------------------------|-------|

| LIST O  | F FIGURES                                                               | vii   |

| LIST O  | F TABLES                                                                | . xiv |

| Chapter | 1. Introduction                                                         | 1     |

| 1.1     | Sub-2 nm Metal Nanoparticles for Semiconductor Device and Sensor        |       |

| Appli   | ications                                                                | 2     |

| 1.2     | Scope of This Dissertation                                              | 6     |

| Chapter | 2. Theory                                                               | 7     |

| 2.1     | Analytical Model for the Metal-Insulator-Metal Tunneling Barrier        | 7     |

| 2.2     | Helmholtz's free energy, Coulomb blockade and Quantum confinement       | 16    |

| 2.2     | .1 Classical SET – Coulomb Blockade vs. SET tunneling                   | 19    |

| 2.2     | .2 Room temperature Classical SET                                       | 21    |

| 2.2     | .3 Quantum SET – Quantum Level Spacing                                  | 24    |

| 2.3     | Calculation of Related Capacitance Terms of Nanoparticles               | 28    |

| 2.3     | .1 Sphere to Plane Model                                                | 28    |

| Chapter | 3. Sub-1 nm Gold Nanoparticle-based Single-Electron Transistors at Room |       |

| Temper  | ature                                                                   | 30    |

| 3.1     | Introduction                                                            | 31    |

| 3.2     | Experiment                                                              | 34    |

| 3.3      | Disc     | ussion                                                                                                            | 36 |

|----------|----------|-------------------------------------------------------------------------------------------------------------------|----|

| 3.3.     | .1 .     | Au NP number estimation                                                                                           | 36 |

| 3.3.     | 3.2      | Role of pentacene layer in electronic properties                                                                  | 37 |

| 3.3.     | 3.3      | Electron addition energy and quantum level spacing                                                                | 40 |

| 3.4      | Futu     | re Work                                                                                                           | 46 |

| Chapter  | r 4. Ba  | rrier Modification of Metal-contact on Silicon by Sub-2 nm Platinum                                               |    |

| Nanopa   | rticle ( | (Pt NPs)                                                                                                          | 47 |

| 4.1      | Intro    | oduction                                                                                                          | 47 |

| 4.2      | Expe     | eriment                                                                                                           | 50 |

| 4.3      | Disc     | ussion                                                                                                            | 51 |

| 4.3      | .1       | Role of thin dielectric layers (SiO <sub>2</sub> and Al <sub>2</sub> O <sub>3</sub> ) in barrier height reduction | 52 |

| 4.3.     | 3.2      | Role of different stacking configuration & metal                                                                  | 55 |

| 4.3      | .3       | Role of Pt NPs embedded between SiO <sub>2</sub> and Al <sub>2</sub> O <sub>3</sub> thin oxide in barrier         |    |

| mo       | dificat  | tion                                                                                                              | 60 |

| 4.4      | Futu     | re Work                                                                                                           | 63 |

| Chapter  | r 5. Eff | fect of Sub-1 nm Pt NPs on Doping/Strain of Single-Layer-Graphene Field                                           | d- |

| Effect T | Γransis  | stor                                                                                                              | 64 |

| 5.1      | Intro    | oduction                                                                                                          | 64 |

| 5.2      | Expe     | eriment                                                                                                           | 67 |

| 5 2      | Dica     | ussion                                                                                                            | 60 |

| 5.3.1         | Pt NP size determination and growth mechanism on graphene               |

|---------------|-------------------------------------------------------------------------|

| 5.3.2         | Electrical characterization of Pt NP-Graphene based FETs                |

| 5.3.3         | Raman Spectroscopy Study                                                |

| Chapter 6. Or | ganic non-volatile memory with embedded sub-nanometer Pt NPs 82         |

| 6.1 Intro     | oduction                                                                |

| 6.2 Exp       | eriment                                                                 |

| 6.3 Disc      | eussion                                                                 |

| 6.3.1         | Transistor Characteristics                                              |

| 6.3.2         | Observation of Size Dependent Effective Work Function of Pt NP Layer in |

| an OFET       | Architecture                                                            |

| 6.3.3         | Electrically charging and discharging behavior via sub-2 nm Pt NPs 91   |

| Chapter 7. Pe | entacene OFET-based Detector for Trace Vapor Explosive Detection 97     |

| 7.1 Intro     | oduction                                                                |

| 7.2 Exp       | eriment                                                                 |

| 7.3 Disc      | cussion                                                                 |

| Chapter 8. Va | apor Phase Molecular Imprinting on Pentacene OFET based Vapor Detector  |

|               |                                                                         |

| 8.1 Intro     | oduction                                                                |

| 8.2 Exp       | eriment                                                                 |

| 8.2.1         | Organic field-effect-transistor fabrication                             |

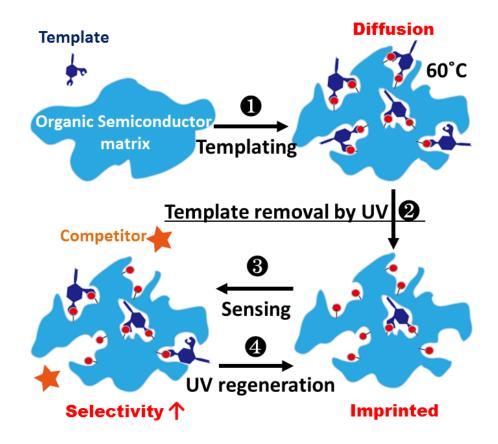

| 8.2.2      | Molecular imprinting method                                   | 116 |

|------------|---------------------------------------------------------------|-----|

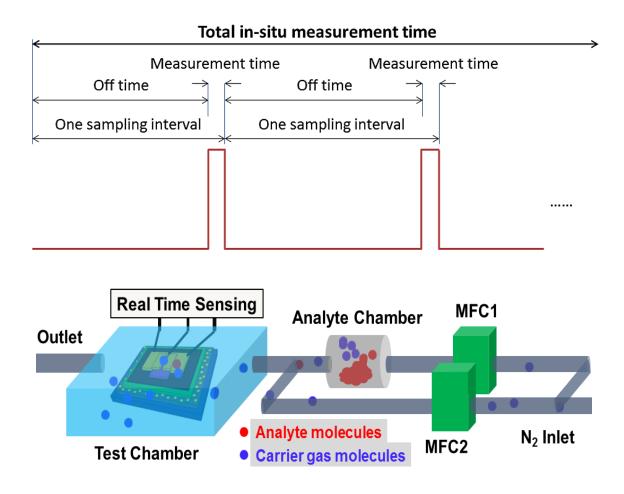

| 8.2.3      | Measurement system                                            | 117 |

| 8.3 Dis    | scussion                                                      | 119 |

| 8.3.1      | Transistor characteristics                                    | 119 |

| 8.3.2      | Change in transfer characteristics after molecular imprinting | 120 |

| 8.3.3      | Selective detection of 2, 4-dinitrotoluene                    | 121 |

| 8.4 Fut    | ure Work                                                      | 124 |

| REFERENC   | CES                                                           | 125 |

| LIST OF PU | JBLICATIONS                                                   | 135 |

| VITA       |                                                               | 137 |

## LIST OF FIGURES

| Figure 2-1 Schematics of energy band diagram for the metal-insulator (vacuum)-metal                |

|----------------------------------------------------------------------------------------------------|

| tunneling junction with asymmetrical barrier height of nanoelectrodes: (a) $V = 0$ ; (b)           |

| $-\phi L < V < 0$ for direct tunneling; (c) $V < -\phi L$ for Fowler-Nordheim tunneling; (d) $0 <$ |

| V < φR                                                                                             |

| Figure 2-2 I-V characteristics for the metal-insulator (vacuum)-metal nanogap tunneling            |

| junction using the same fitting parameters as [26]                                                 |

| Figure 2-3 Simulated I-V characteristics for the metal-insulator (vacuum)-metal nanogap            |

| tunneling junction using the same fitting parameters as shown in [26]                              |

| Figure 2-4 Simulated I-V characteristics for the Metal-Insulator (Vacuum)-Metal                    |

| Nanogap tunneling junction with symmetric barrier heights of 4.5 eV                                |

| Figure 2-5 Equivalent circuit of a single island tunneling device with source, drain and           |

| gate electrodes                                                                                    |

| Figure 2-6 Comparison of Coulomb Blockade vs. SET tunneling modes for a Classical                  |

| SET                                                                                                |

| Figure 2-7 Typical classical three terminal SET stability plot with Coulomb diamond                |

| pattern and $I_D$ - $V_{is}(V_g)$ characteristics showing the Coulomb oscillation. (Inset: the     |

| corresponding equivalent circuit)                                                                  |

| <b>Figure 2-8</b> Effect of temperature to the stability plot of a SET with a 0.98 nm Au NP as     |

| an island                                                                                          |

| <b>Figure 2-9</b> Comparison of simulated stability plot of 0.98 nm Au NP SET with (a) Al <sub>2</sub> O <sub>3</sub> |

|-----------------------------------------------------------------------------------------------------------------------|

| (b) SiO <sub>2</sub> , and (c) air, at 300 K                                                                          |

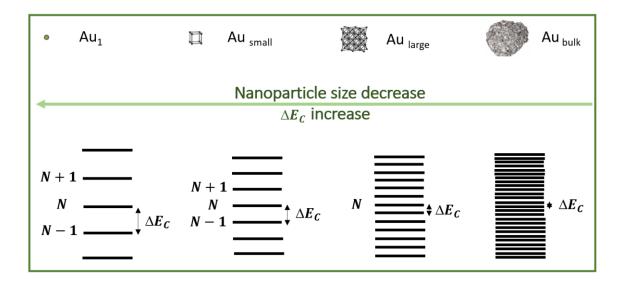

| <b>Figure 2-10</b> Schematics showing the size dependent quantum-level spacing                                        |

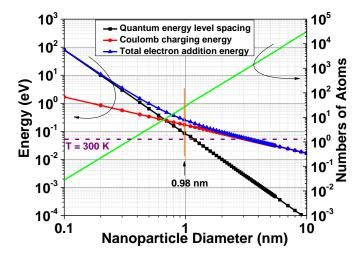

| <b>Figure 2-11</b> Theoretical Coulomb Charging Energy (●), the Quantum Confinement                                   |

| Energy level spacing ( $\blacksquare$ ), total electron addition energy ( $\triangle$ ), and the estimated numbers    |

| of atoms vs. the NP diameter (/). The dotted line indicates the thermal energy at $T=300$                             |

| K25                                                                                                                   |

| Figure 2-12 Comparison of energy band diagram of (a) Classical SET vs. (b) Quantum                                    |

| SET                                                                                                                   |

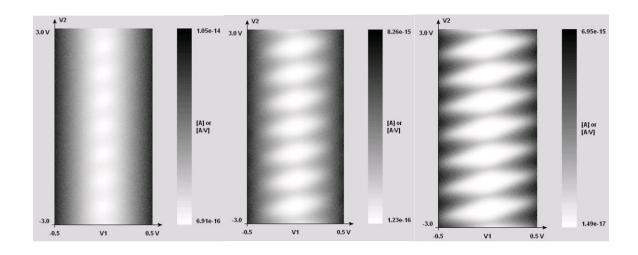

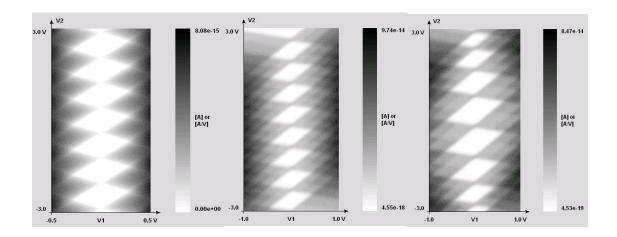

| Figure 2-13 Comparison of simulated stability plot of a (a) classical SET vs. (b)                                     |

| quantum SET with equal QCE vs. (c) quantum SET with unequal QCE at 4.2 K 27                                           |

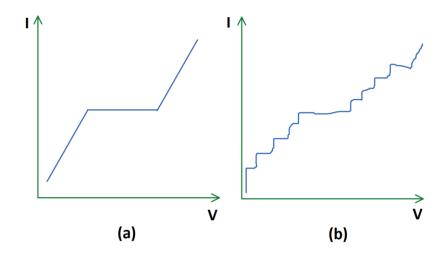

| Figure 2-14 Comparison of I-V characteristics of a (a) classical SET vs. (b) quantum                                  |

| SET with quantum staircase effect                                                                                     |

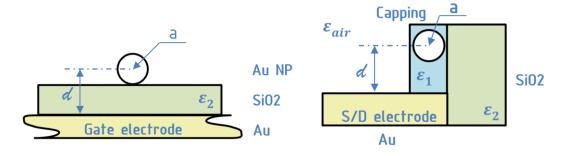

| Figure 2-15 Schematics of a sphere-plane capacitor for (left) a gate electrode coupled to                             |

| a single NP (right), which is an embedded NP coupled to a source or drain electrode 28                                |

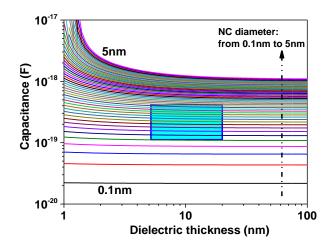

| Figure 2-16 Calculated bottom-gate-NP capacitance vs. NP size and dielectric thickness                                |

| $(SiO_2 \ or \ pentacene).$ The cyan rectangle is the possible tunneling capacitance range of our                     |

| SET studied in 2.3. In this region (0.5 nm $<$ NP diameter $<$ 1.5 nm, 5 nm $<$ dielectric                            |

| thickness $< 20 \text{ nm}$ ), the tunneling capacitance is dependent on the NP size and somewhat                     |

| independent of the dielectric thickness.                                                                              |

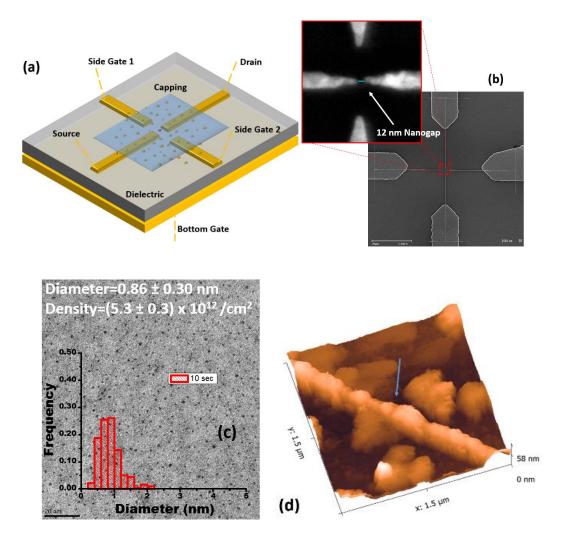

| Figure 3-1 (a) Schematic of SET device structure; (b) SEM image of the e-beam                                              |

|----------------------------------------------------------------------------------------------------------------------------|

| patterned nanoelectrodes (scale bar 20 μm); inset: nanoelectrode structure with 12 nm                                      |

| gap. The two side gates were not used in this study; (c) Transmission electron                                             |

| microscopy image of 0.86 nm Au NPs with the inset showing the Au NP size                                                   |

| distribution. The scale bar is 20 nm; (d) AFM images of Au nanoelectrodes after                                            |

| pentacene deposition                                                                                                       |

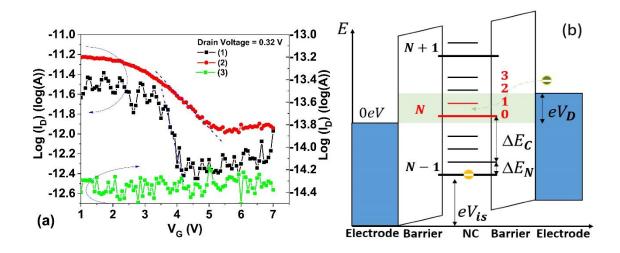

| Figure 3-2 (a) Drain current vs. gate voltage characteristics of the devices with: (1) 0.86                                |

| nm Au NP and pentacene capping layer, (2) pentacene capping layer only, and (3) 0.86                                       |

| nm Au NP only; (b) Energy band diagram for the biased SET                                                                  |

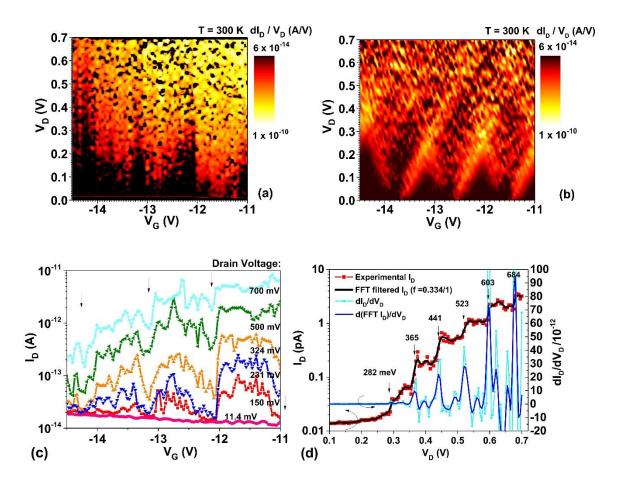

| Figure 3-3 (a) Experimental and (b) simulated 2-D stability plot of dID/dVD vs.                                            |

| VD and VG for VG from -14.5 V to -11 V at 300 K; (c) $I_D$ vs. $V_G$ plot with different $V_D$                             |

| showing $V_G$ modulation of Coulomb oscillation at 300 K, arrows indicate Coulomb                                          |

| blockade valleys; and (d) $I_D$ vs. $V_D$ plot with $V_G = 12.3$ V showing quantum confinement                             |

| staircases                                                                                                                 |

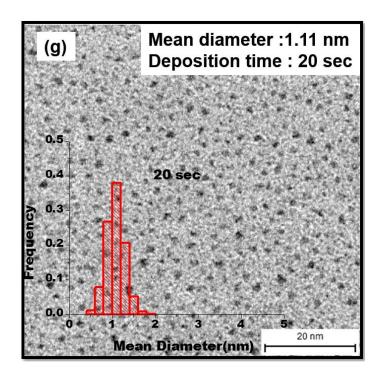

| Figure 4-1 TEM image of 1.11 nm TTS-deposited Pt NPs                                                                       |

| Figure 4-2 Comparison of Ti-p Si contact with different thicknesses and types of                                           |

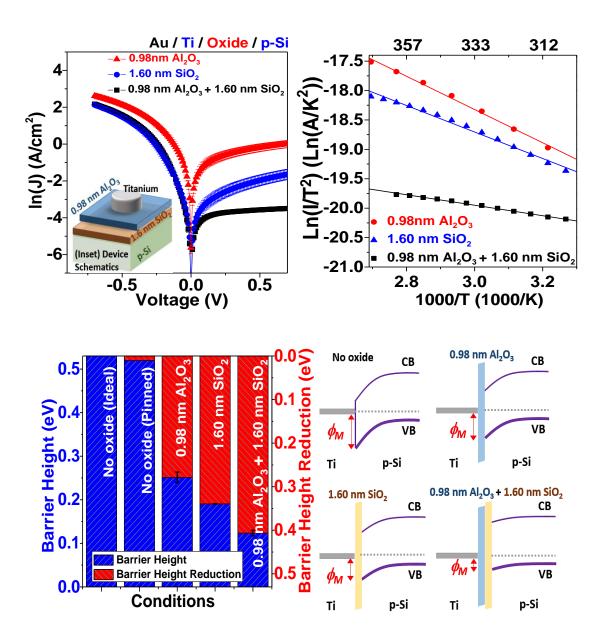

| dielectrics (a) Ln (J)-V characteristics. Inset: Schematics of device structures; (b) the                                  |

| Richardson plots; (c) the barrier heights; (d) schematics of energy band diagram showing                                   |

| the barrier reduction of Ti-p Si contact by insertion of thin dielectrics                                                  |

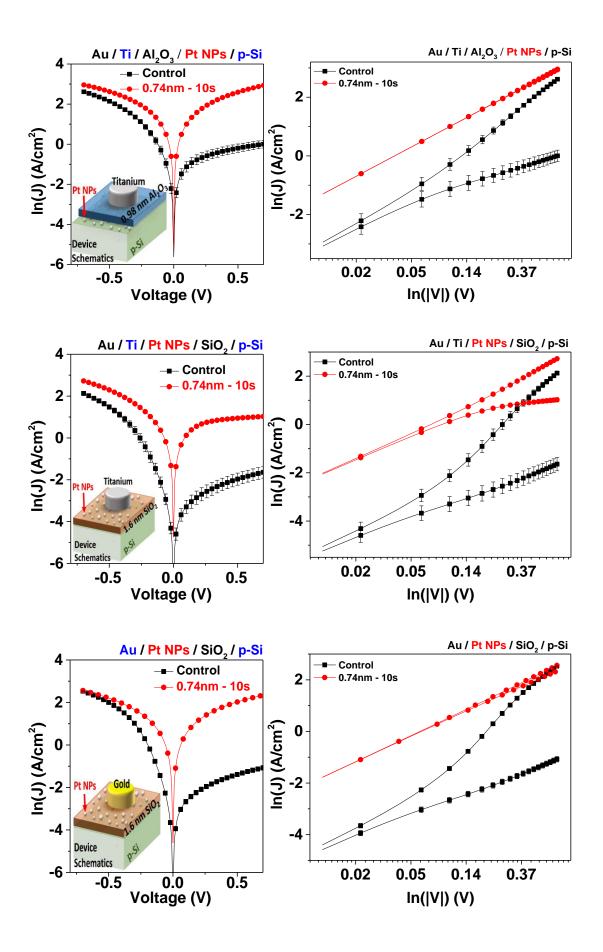

| <b>Figure 4-3</b> Comparison of ln(J)-V and ln(J)-ln(V) characteristics for (a, b) Ti-Al <sub>2</sub> O <sub>3</sub> -p Si |

| contact with and without 0.74 nm Pt NPs between the Al <sub>2</sub> O <sub>3</sub> and Si surface; (c, d) Ti-              |

| SiO <sub>2</sub> -p Si contact with and without 0.74 nm Pt NPs between the Ti electrode and SiO <sub>2</sub>               |

| surface; (e, f) Au-SiO <sub>2</sub> -p Si contact with and without 0.74 nm Pt NPs between the Au                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------|

| electrode and SiO2 surface; Inset: Schematics of the device structures. (g) Schematics                                                        |

| showing the dipole formation between Ti electrode and Pt NP. (h, i) Schematics of                                                             |

| energy band diagram showing the reduction of depletion width with the presence of Pt                                                          |

| NPs                                                                                                                                           |

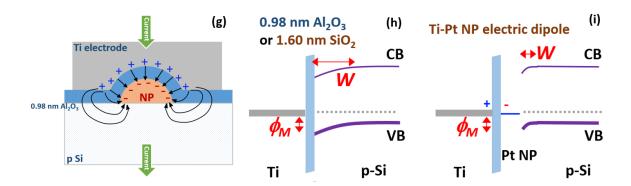

| <b>Figure 4-4</b> Comparison of (a) C <sub>D</sub> -V, (b) G <sub>P</sub> -V, and (c) depletion width Ti-Al <sub>2</sub> O <sub>3</sub> -p Si |

| contact with and without 0.74 nm Pt NPs (10s)                                                                                                 |

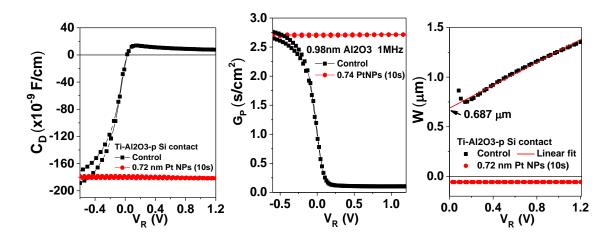

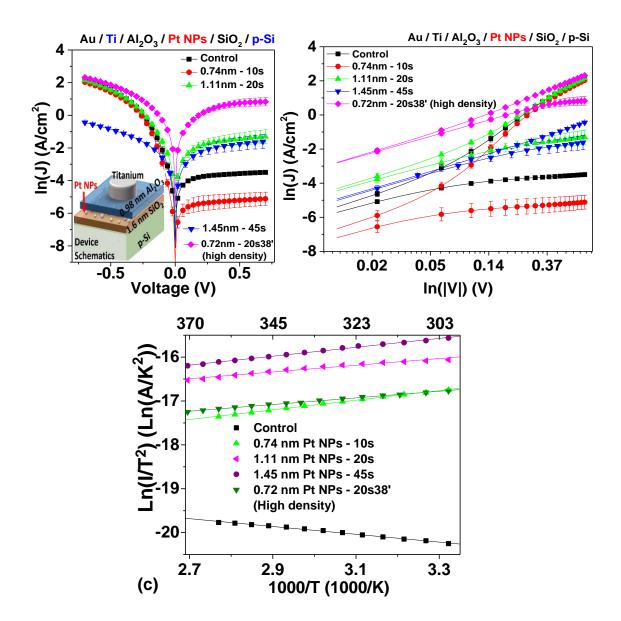

| Figure 4-5 Comparison of Ti-p Si contact with different sizes of Pt NPs sandwiched                                                            |

| between the 0.98 nm $Al_2O_3$ and 1.6 nm $SiO_2$ (a) $Ln(J)$ -V characteristics. Inset:                                                       |

| Schematics of device structures; (b) $Ln(J)-Ln( V )$ characteristics; (c) the Richardson                                                      |

| plots; (d) schematics showing the dipole formation between Ti electrode and Pt NP; (e)                                                        |

| Equivalent circuit of the device showing the Coulomb blockade effect; (f, g) schematics                                                       |

| of energy band diagram showing the electron wave penetration and the reduction in                                                             |

| depletion width with the presence of Pt NPs                                                                                                   |

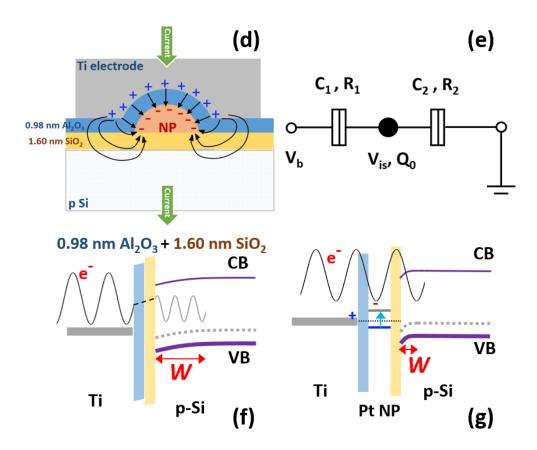

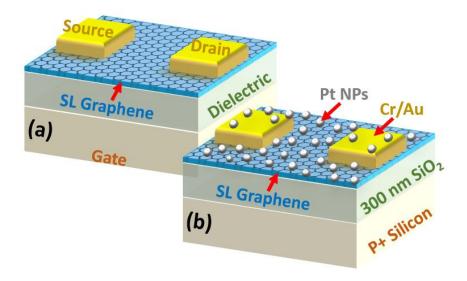

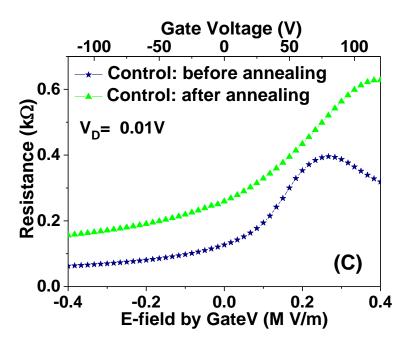

| Figure 5-1 Device schematics of graphene FET (a) without and (b) with Pt NPs                                                                  |

| deposited on top of graphene. (c) R-E characteristics of control sample before and after                                                      |

| H <sub>2</sub> annealing                                                                                                                      |

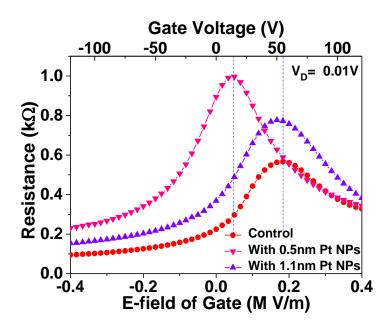

| Figure 5-2 Comparison of resistance-electric field characteristics for devices with and                                                       |

| without conduction channel modification by different sizes of Pt NPs                                                                          |

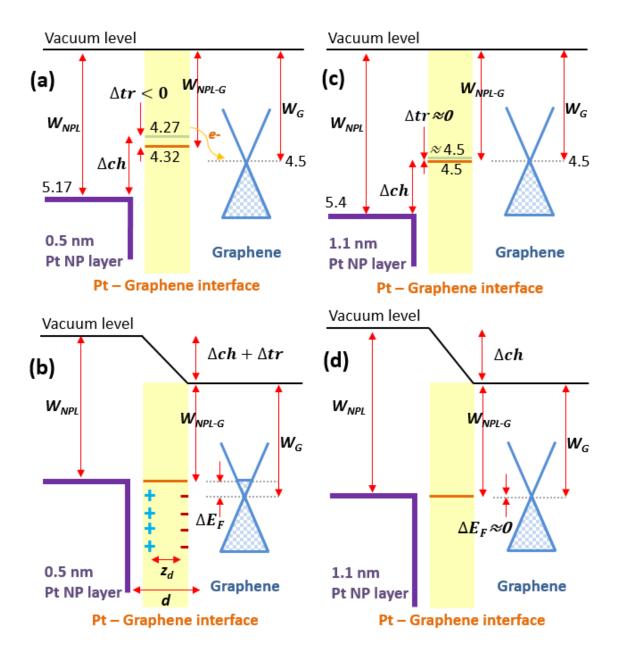

| Figure 5-3 Schematic of changes in energy band diagram for graphene-based FET before                                                          |

| (a, c) and after (b, d) Pt NP deposition: (a, b) device with 0.5 nm Pt NP layer showing n-                                                    |

| type doping behavior; (c, d) device with 1.1 nm Pt NP layer showing no doping behavior.     |

|---------------------------------------------------------------------------------------------|

|                                                                                             |

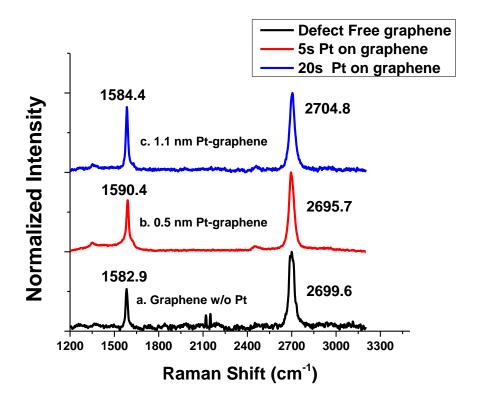

| Figure 5-4 Representative Raman spectra of the control graphene sheet (curve a) and         |

| after depositing 0.5 nm Pt NPs (curve b) with 1.1 nm Pt NPs (curve c) on top79              |

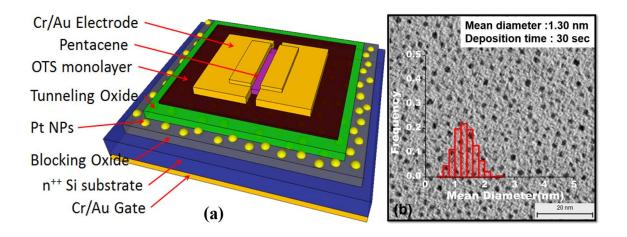

| Figure 6-1 (a) Schematic illustration of pentacene FET; (b) plane view TEM image of         |

| uniformly distributed 1.30 nm Pt NPs with scale bar: 20 nm (Inset: frequency distribution   |

| of 1.30 nm Pt NP)                                                                           |

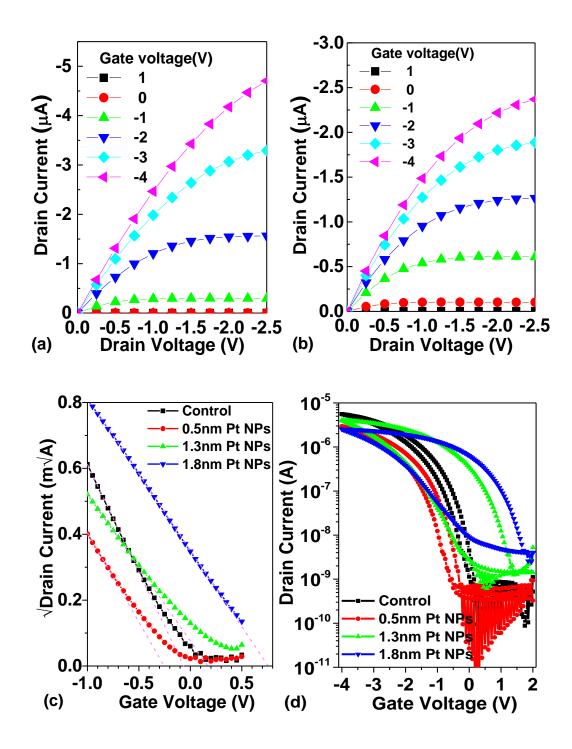

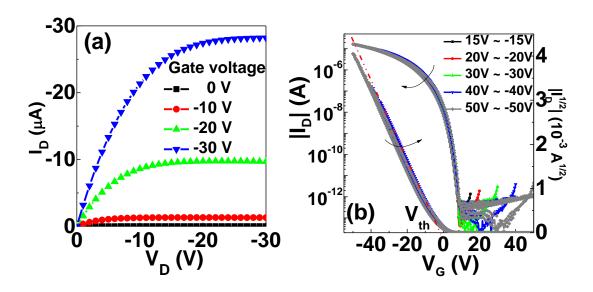

| Figure 6-2 (a) and (b) Output characteristics of (a) control device and (b) device with     |

| embedded 1.3 nm Pt NPs; (c) and (d) Comparison of pentacene FET transfer                    |

| characteristics without and with Pt NPs measured at -2.5 V drain voltage with gate          |

| voltage sweeping from (c) 0.5 V to -1 V and (d) 2 V to -4 V                                 |

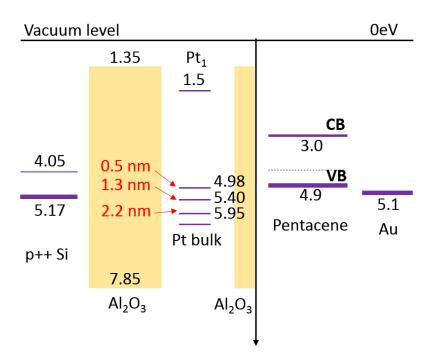

| Figure 6-3 Energy band diagram of pentacene FET with embedded Pt NPs under flat             |

| band condition                                                                              |

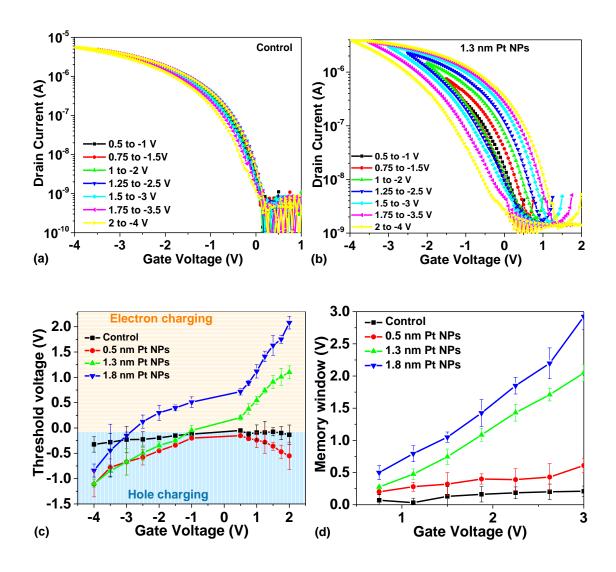

| Figure 6-4 (a & b) Memory behavior of pentacene FET (a) without and (b) with 1.3 nm         |

| Pt NPs measured at -2.5 V drain voltage and sweeping gate voltage; (c) threshold voltage    |

| shift and (d) memory window under different gate bias sweeping for sample with              |

| different size Pt NPs                                                                       |

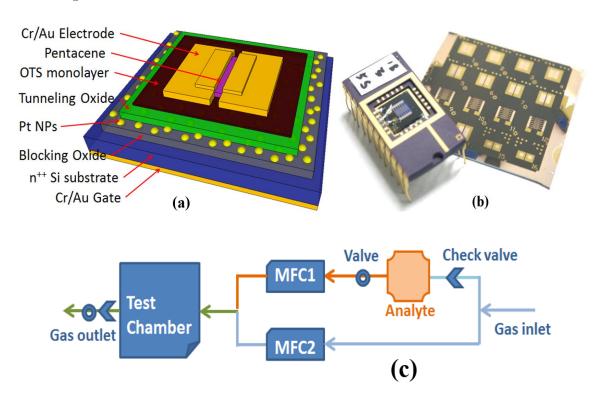

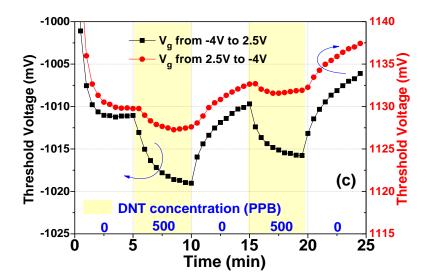

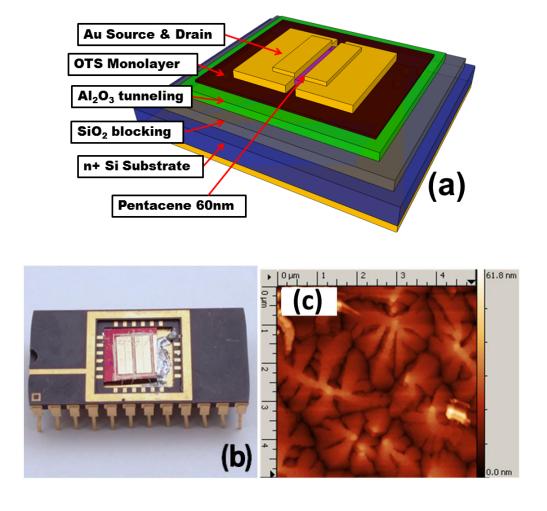

| Figure 7-1 Pentacene-based OFET: (a) Schematic of device structure; (b) actual devices      |

| with different width length ratios and sensor within a dual-inline package for sensing; (c) |

| schematics of analyte vapor generation and in situ vapor detection system                   |

Figure 8-3 Experimental setup for sensor characterization and in-situ vapor detection.118

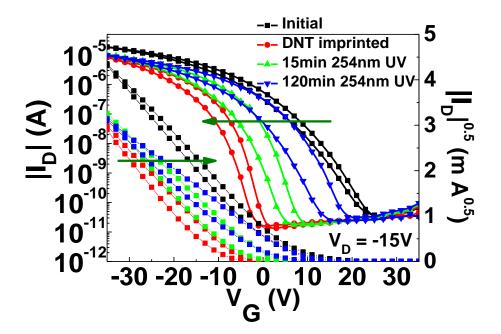

| Figure 8-4 (a) Output characteristics and (b) transfer characteristics of pentacene-based |

|-------------------------------------------------------------------------------------------|

| OFET with 50:1 width: length ratio                                                        |

| Figure 8-5 Changes in OFET transfer characteristics before and after DNT saturation and   |

| after 254 nm UV exposure for 15 min and 120 min                                           |

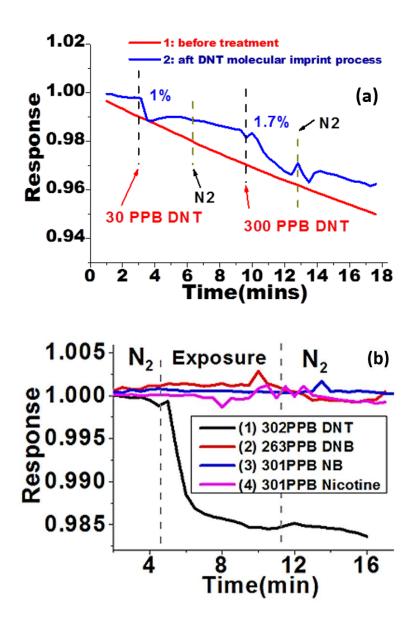

| Figure 8-6 (a) Comparison of drain current response of the pentacene OFET sensor          |

| against various concentrations of DNT vapor before and after vapor phase MIP; (b) drain   |

| current response of the imprinted pentacene OFET sensor toward target and interfering     |

| analytes (black: 300 ppb DNT [target]; red: 260 ppb DNB; blue: 300 ppb NB, and pink:      |

| 300 ppb Nicotine)                                                                         |

## LIST OF TABLES

| Table 2-1 Simulation parameters and characteristic values of Figure 2-9.    22          |

|-----------------------------------------------------------------------------------------|

| Table 2-2 Simulation parameters and characteristic values of Figure 2-10.    23         |

| Table 4-1 Summary of the Pt NP conditions used in this study    51                      |

| Table 5-1 Summary of average G and 2D peaks positions taken at five separate points     |

| across the samples and the G and 2D peak shift magnitudes with the uncertainty for each |

| condition (based on the propagation of errors method) in <b>Figure 5-4</b>              |

| Table 6-1 Experimentally derived effective work function of different size Pt NPs       |

| embedded within the Al <sub>2</sub> O <sub>3</sub> dielectric                           |

| Table 6-2 Summary of pentacene NVM device memory characteristics without and with       |

| embedded Pt NPs                                                                         |

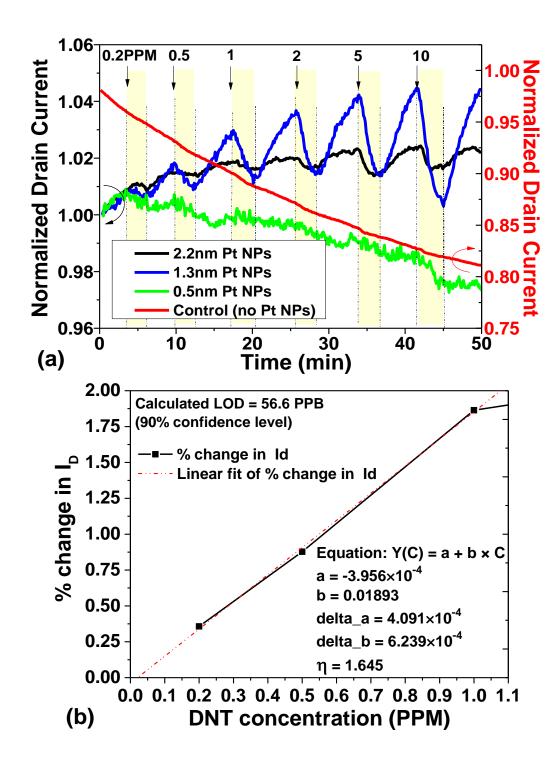

| <b>Table 7-1</b> Summary of Platinum NPs properties with different sizes                |

| Table 8-1 Changes of various OFET sensor parameters during molecular imprinting         |

| process                                                                                 |

#### EXPLORING THE CHARGE STORAGE PROPERTIES OF SUB-2 NM METAL

#### NANOPARTICLES - APPLICATIONS IN FIELD EFFECT TRANSISTOR

#### MEMORY AND DETECTION OF TRACE VAPOR MOLECULES

#### Haisheng Zheng

Dr. Shubhra Gangopadhyay, Dissertation Supervisor

#### **ABSTRACT**

Sub-2 nm size metal nanoparticles are unique compared to their bulk counterparts in semiconductor device and sensor applications due to their size-dependent behaviors, such as Coulomb blockade effect, quantum confinement effect, and the size-dependent work function. In this thesis, the single electron charging behaviors of these nanoparticles are studied through the room temperature operable single charge tunneling devices. Further, by embedding these nanoparticles as discrete charge storage sites in a macroscopic organic field-effect transistor, the electron or hole charging behaviors due to the nanoparticle size-dependent work function are investigated. These memory devices are utilized as sensitive trace vapor detector with the embedded nanoparticles as detection sites. Lastly, the application of these nanoparticles as charge injection hotspots for achieving ideal Ohmic metal-semiconductor contacts, and the doping effects of the nanoparticles to the conduction channel of 2D material-based field effect transistors are studied.

### **Chapter 1. Introduction**

Metal nanoparticles (MNPs) have attracted great interest in different areas due to their unique electrical and physical-chemical properties at the nanoscale [1]-[4]. Bulk electrical phenomena expected of metals (e.g., Ohm's Law) also lose validity as the electron bands become discretized due to quantum confinement [3]. Adding single charges to MNPs costs energy because the energy levels can no longer be considered as continuous, as in the case of bulk metals [3]. The properties that separate MNPs from their conducting bulk metal counterparts are derived from their physical dimensions, including surface-tovolume atom ratio, free electron density, quantized energy level, charging energy, and surface-dipole-enhanced local electric field [5]-[7]. By utilizing the size-dependent behavior of sub-nm MNPs, room temperature operable single charge storage devices can be developed. Because of these excellent charge storage and catalytic properties, MNPs have found roles in integrated electronic/electrochemical device architectures, in which they function as discrete charge storage or catalytic materials [4], [7]–[9]. By embedding MNPs as discrete charge storage sites in a macroscopic field-effect transistor, the program/erase lifetime and retention rate can be improved significantly when compared to traditional floating gate memory.

A large fraction of the atoms in an MNP contain only a few hundred atoms and are located on the surface. These surface atoms are more electrically and electrochemically active due to the fact that they are less coordinately saturated [10]. Charges in a charged MNP also tend to distribute on the outer perimeter of the MNP surface due to the electrostatic interaction and formation of a surface electric dipole with the environmental

charges [11]. The smaller the nanocrystal, the larger the resultant electric field enhancement due to this surface electric dipole and a corresponding change in the MNP work function at their surface, a property that is especially powerful for MNPs in the sub-2 nm diameter regime. The size-dependent work function leads to important applications of MNPs as catalytic molecules and in trace vapor explosive molecule detection since MNPs with dipole-enhanced surface electric field and proper work function facilitate charge transfer between molecules [12]–[14]. MNPs with a large surface electric dipole due to their interaction with other metal or semiconductors also tend to modulate the localized electric field, thus allowing their use for barrier modulation of a macroscopic metal-semiconductor contact or doping 2-D materials such as graphene [15], [16].

## 1.1 Sub-2 nm Metal Nanoparticles for Semiconductor Device and Sensor Applications

Noble metal nanoparticles (MNPs) have proven advantageous over semiconductor clusters and organic molecules in single-electron transistor (SET) applications due to their higher environmental stability, greater density of states, and mature fabrication techniques [5]–[7]. Theory predicts that MNP dimensions less than 1 nm are required for the quantum confinement energy to surpass the room temperature (RT) thermal noise sufficiently enough to probe single electron quantum excitation states [17]–[19]. Meanwhile, the relatively small electron charging energies of MNP-based SET devices have so far prevented clear RT observation of these Coulomb oscillations and quantum confinement states [17]–[19]. This dissertation is based on the study of controlled deposition of sub-2 nm MNPs by a recently developed tilted target sputtering (TTS) process as well as their applications for single charge storage [5], [7], [12], [20], multi-bit memory [21], metal-

semiconductor contact modification, graphene conduction channel modification [15], [16] and trace explosive vapor detection [13]. MNP sizes and areal densities are controlled by varying the TTS deposition time and deposition (RF) power [22]. Using TTS-deposited MNPs as discrete charge storage nodes, their ultra-small sizes provide the ability to observe and control charge storage and transfer down to the single electron level at ambient temperature (300 K). SET devices incorporating single ~1 nm Au nanoparticles (Au NPs) as a charge transport island were used to study the quantum Coulomb blockade and quantized energy level spacings at room temperature (300 K).

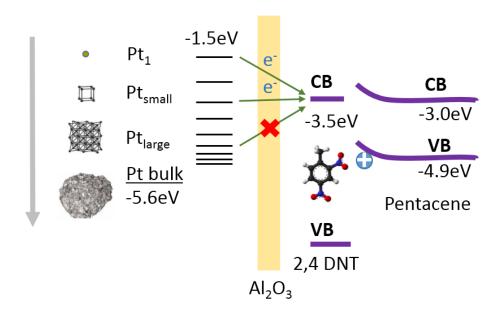

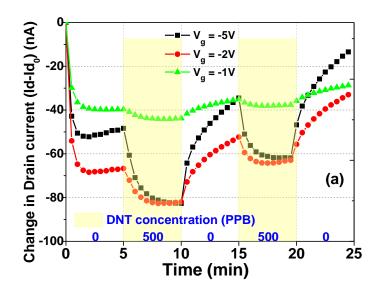

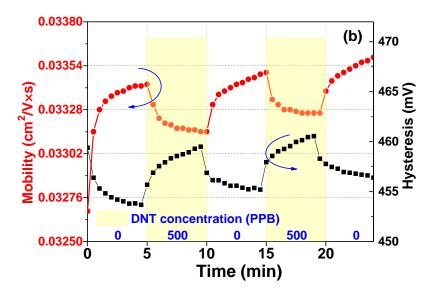

In order to observe the single electron charging behavior of MNPs in macroscopic devices, a device schematic was proposed in which size-tunable sub-2 nm Pt nanoparticles (Pt NPs) were embedded between the tunneling and blocking dielectric layers of a low operation voltage pentacene transistor non-volatile memory (NVM). Controllable work function was observed in the embedded Pt NPs through the size-dependent threshold voltage shift. Non-volatile memory transistors containing embedded Pt NPs exhibited sizeand density-dependent memory windows in their transfer characteristics, which was attributed to electron and hole charging and discharging behavior. While devices with small (0.5 nm) Pt NPs demonstrated strong Coulomb blockade and quantum confinement with electron addition energy as large as 1.993 eV, those made with larger (1.8 nm) Pt NPs, allowed for storage of a single charge per NP memory. Pentacene NVM with embedded sub-2 nm Pt NPs were also studied for sensitivity towards trace nitroaromatic explosive vapors. Exploiting the unique electronic properties of Pt NPs, a detection limit of 56.6 parts per billion of 2,4-dinitrotoluene (DNT) vapor was demonstrated while control samples without Pt NPs showed no observable sensitivity to DNT vapor. This remarkable sensitivity has been attributed to the ability of sub-2 nm Pt NPs to function as discrete nodes participating in charge transfer with adsorbed nitroaromatic molecules. Pentacene-based FET sensor device selectivity was further improved by a vapor phase molecular imprinting (MIP) technique developed and reported below. This OFET-based sensor using pentacene as the molecularly imprinted monomer showed enhanced selectivity to DNT vapor against various interfering analytes. This method can be extended to improve the selectivity of most OFET- and chem-resistor-based sensors without adversely affecting device electronic properties, which is promising for the development of highly selective, low-cost, flexible OFET sensors.

Sub-2 nm MNPs with enhanced localized electric field also find application in barrier modification of the metal-semiconductor contact. One longstanding issue in fabrication of semiconductor devices is Fermi level pinning of the semiconductor at the metal-semiconductor interface. Selecting metals with different work functions provides only limited control over Ohmic contact or Schottky contact barrier height. Extensive studies have demonstrated the benefits of using reduced metal-semiconductor contact resistance using thin insulating tunnel barriers with fixed charges [23], [24]. However, the optimal insulating layer thickness (e.g. ~1 nm for Al<sub>2</sub>O<sub>3</sub>) is difficult to fabricate and thicker insulator layers increase the contact resistance due to reduction in tunneling probability. Dielectric layers below this thickness are generally unreliable due to surface discontinuities. In this study, the metal-semiconductor contact barrier is controlled by the introduction of sub-2 nm Pt NPs) deposited by TTS. We show the size-dependent Pt NP properties and their role in Fermi level depinning at the metal-silicon interface with a 0.98 nm Al<sub>2</sub>O<sub>3</sub> or 1.6 nm SiO<sub>2</sub> dielectric layer. The initial study demonstrated that samples

modified with 0.74 nm Pt NPs show  $>10^3$  times higher current density compared to a Tithin oxide-Si contact (control). It also further revealed that the contact can be modulated to be either Schottky or Ohmic using the same contact metal by varying only Pt NP size and areal density.

Another application of MNPs with enhanced localized electric field is in conduction channel modification of 2-D material-based FETs. Graphene's promising electronic properties make graphene-based transistors attractive platforms for future devices. It is well documented that graphene exhibits ballistic transport at the submicron scale and can be doped heavily using a multitude of techniques without significant loss of mobility [25]. Meanwhile, choosing the same metal as the contact electrode for doping is sometimes preferable over using other destructive techniques to minimize contamination. In this report, the doping/strain introduced by ultrafine sputtered Pt NPs of different sizes on single layer graphene has been studied through conduction channel modification of graphene-based FETs and their Raman characterization. For sub-nm (0.5 nm) diameter Pt NPs, a substantial Dirac point shift was observed in the I-V characteristics, suggestive of n-type doping of the large area single layer graphene through the process of charge transfer and chemical interaction. Conversely, for larger (1.1 nm) Pt NPs, a minimal Dirac point shift was observed, indicating lack of the charge transfer-induced doping effect. The representative Raman signatures corroborate with the electrical characterization results and indicate that while charge transfer dominates Raman peak shift for the 0.5 nm Pt NP decorated graphene, strain effect dominates in case of the larger 1.1 nm Pt NP.

#### **1.2 Scope of This Dissertation**

This dissertation is divided into eight chapters dealing with the different applications of sub-2 nm MNPs in semiconductor device and trace vapor molecule sensor systems. Chapter 2 starts with discussion of theories and concepts that will be used throughout the dissertation. Subtopic 2.3 discusses the size-dependent charging energy and quantum level spacing of sub-1 nm Au NP and its application in room temperature operable SET devices. Chapter 4 discusses the barrier modification of metal-silicon contact by sub-2 nm Pt NPs as an alternative to reduce contact resistance and improve current injection in semiconductor devices. While exploring the interaction of MNPs on a metalsemiconductor interface, Chapter 5 discusses the effects of sub-1 nm Pt NPs on doping/strain of single layer graphene and its role in modulating the conduction properties of a graphene-based FET. Chapter 6 discusses the utilization of sub-2 nm Pt NPs to achieve low operation voltage pentacene-based NVM by embedding them between the tunneling and blocking dielectric layers. The observation of the controllable effective work function of the Pt NP layer through the size-dependent threshold voltage shift was also discussed. Further exploration of pentacene NVM with embedded Pt NPs for improving the sensitivity of detection toward trace vapor explosives and the NP size-dependent charge interaction with analytic molecules are discussed in Chapter 7. Chapter 8 discusses the development of a vapor-phase molecular imprinting method to further improve the selective detection capability of pentacene FET-based sensors. The terms nanoparticle (NP), island, nanocluster (NC) and quantum dot may be used interchangeably throughout the context of this dissertation when appropriate.

### Chapter 2. Theory

#### 2.1 Analytical Model for the Metal-Insulator-Metal Tunneling Barrier

In classical mechanics, if the energy of a particle E is smaller than the maximum height of the potential barrier V of a quantum well, the particle remains in the well forever. Whereas in quantum mechanics, an electron can escape even if its energy E is below the height of the barrier V. Quantum tunneling has no counterpart in classical physics.

For designing a SET device, it is a good practice to have some idea on the tunneling current level of a metal-insulator-metal (MIM) barrier without the charge storage island. Analytical models have been well developed by earlier works and used to estimate the current level. Mangin et al. [26] showed that the tunneling resistance is not only determined by the width of the barrier, but is also due to the strong function of the barrier height of the electrodes on both sides. Namely, one cannot determine the size of the nanogap simply by evaluating the resistance under low bias condition (direct tunneling). However, for determining the tunneling resistance for an SET working in a single electron tunneling region (low bias), we assume that the barrier height is relatively high, and the barrier is in a rectangular shape (direct tunneling).

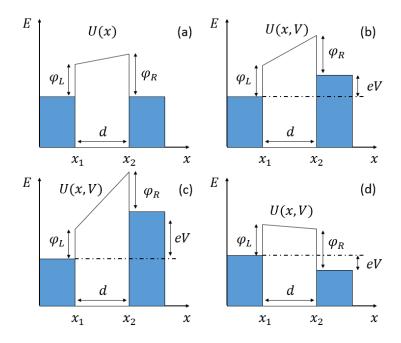

**Figure 2-1** Schematics of energy band diagram for the metal-insulator (vacuum)-metal tunneling junction with asymmetrical barrier height of nanoelectrodes: (a) V = 0; (b)  $-\varphi_L < V < 0$  for direct tunneling; (c)  $V < -\varphi_L$  for Fowler-Nordheim tunneling; (d)  $0 < V < \varphi_R$ .

**Figure 2-1** shows the schematics of an energy band diagram for the metal-insulator (vacuum)-metal nanogap tunneling junction with an asymmetrical barrier height of nanoelectrodes under different bias conditions. The potential profile of the insulating gap between the nanoelectrodes under applied voltage V is given by

$$U(x,V) = \varphi_L + \frac{\varphi_R - \varphi_L - eV}{d} * x$$

,  $x_1 < x < x_1 + d$  (2-1)

The wave function of an electron  $\psi$  is determined by the Schrodinger equation [27]

$$\frac{d^2\psi}{dx^2} + \frac{2m^*}{\hbar^2} [E - U(x)]\psi = 0, \qquad (2-2)$$

where  $m^*$  is the electron mass and  $\hbar$  is the Planks constant. By using the Wentzel Kramers Brillouin (WKB) approximation, the electron transmission probability across the nanogap

T(E,V) is given by [26]

$$T(E,V) = \frac{|\psi_R|^2}{|\psi_L|^2} \approx exp\left\{-\int_{x_1}^{x_1+d} \frac{4\pi}{\hbar} \sqrt{2m^*[U(x,V) - E]} \, dx\right\}$$

(2-3)

where E is the total energy of an incoming electron under a bias voltage of V. Assuming the constriction is ballistic with a size comparable to the Fermi wavelength  $\lambda_F$  with a single transmission channel, a one dimensional model is used in this study. Considering the electron tunneling in the nanogap as a scattering problem, the tunneling current is calculated by applying the Landauer-Buttiker formalism, which is determined by

$$I(V) = \frac{2e}{\hbar} \int_0^{+\infty} \left[ F(E) - F(E - eV) \right] * T(E, V) dE$$

(2-4)

where F(E) and F(E - eV) are the Fermi-Dirac distribution of electrons in the electrodes under thermal equilibrium and an applied voltage V, respectively. f(E) and f(E - eV) are given, respectively, by [27]

$$F(E) = \frac{1}{1 + exp(\frac{E - E_F}{kT})}$$

and  $F(E - eV) = \frac{1}{1 + exp(\frac{E - E_F - eV}{kT})}$  (2-5)

where  $E_F$  is the Fermi level of the electrode (in the case of this work, gold).

A typical I-V characteristics of an MIM nanogap fabricated by performing a controlled electro-migration on an e-beam deposited gold nanobridge, measured and simulated by Mangin et al. can be found in [26]. The parameters used by the paper for fitting are as follows: Gap size: 1.2 nm, barrier height for the two sides: left 0.29 eV and right 0.95 eV, respectively, with a tunneling area of 10 nm<sup>2</sup>. Note that the reduced barrier is drastically lower than the usually reported experimental work function of gold (~5.1–5.3 eV). According to the author, this reduced barrier height could be due to surface contamination.

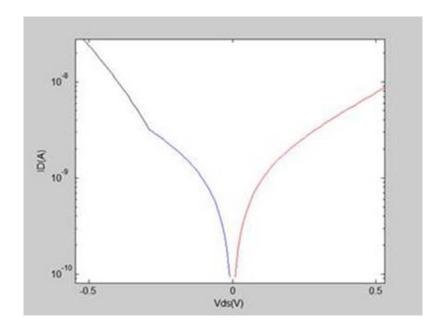

By using the model given in Eq.(2-4) and using the same parameters given above, a simple MATLAB<sup>®</sup> code was written to obtain the simulated IV characteristics shown in **Figure 2-2**. The results are comparable to what is in [26].

**Figure 2-2** I-V characteristics for the metal-insulator (vacuum)-metal nanogap tunneling junction using the same fitting parameters as [26].

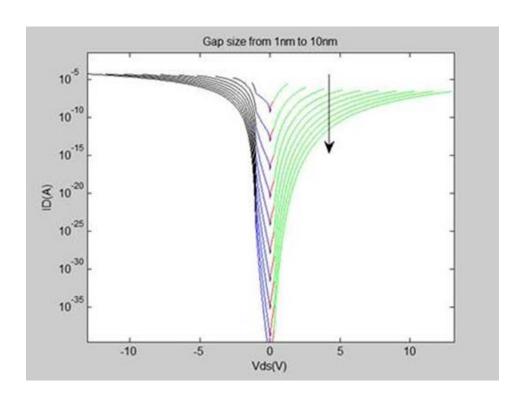

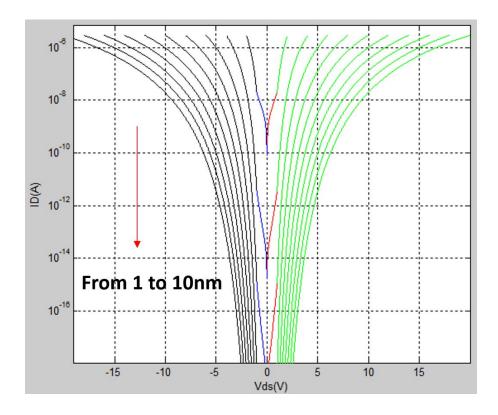

If we assume having a similar nanogap to the one in [26] with an asymmetric barrier height of left 0.29 eV and right 0.95 eV, except for ranging the gap size from 1 nm to 10 nm, with a 1 nm step size, the simulation result is found to be the same as that shown in **Figure 2-3**. For a 10 nm gap, 5 to 10 V is expected to give a 1 x  $10^{-10}$  to 1 x  $10^{-8}$  A of current level. In comparison, **Figure 2-4** shows the results for symmetric barrier heights of 4.5 eV for both sides of the electrode. This model is only applicable for a device operating before the avalanche breakdown takes place, in which condition the configuration of the nanogap might change permanently due to electron migration. So in our study, we operated the device within 1 x  $10^{-8}$  A of compliance current.

**Figure 2-3** Simulated I-V characteristics for the metal-insulator (vacuum)-metal nanogap tunneling junction using the same fitting parameters as shown in [26].

**Figure 2-4** Simulated I-V characteristics for the Metal-Insulator (Vacuum)-Metal Nanogap tunneling junction with symmetric barrier heights of 4.5 eV.

The MATLAB code used for the above simulation is given as follows:

| %% Modeling of MIM nanogap tunneling junction                             |

|---------------------------------------------------------------------------|

| clear;clc;                                                                |

| %% Defining constants                                                     |

| PI=3.1415926535897932; % Pi constant                                      |

| Q=1.60217733E-19; % Electronic charge [C]                                 |

| TEMP=300; % Temperature [K]                                               |

| KB1=1.380658E-23; % Boltzmann's constant [J/K]                            |

| KB2=8.6174E-5; % Boltzmann's constant [eV/K]                              |

| KT=0.0256; % Thermal energy [eV]                                          |

| HP1=6.62617E-34; % Plank's constant [J*s]                                 |

| HP2=4.1357E-15; % Plank's constant [eV*s]                                 |

| e=2.7183;                                                                 |

| Me=9.1095e-31 *1;  % Relative Effective electron mass of insulator * free |

| electron mass [kg]                                                        |

| Me_AL2O3 = Me *0.25;  % Effective electron mass of al2o3                  |

|                                                                           |

|                                                                           |

% Relative permittivity of SiO2

EP\_SIO2=3.9;

EP0=8.8542E-12; % Vacuum permittivity [F/m]

%% Defining Parameters

%syms Vds;

FIL=4.5; % Barrier height of left electrode [eV]

FIR=4.5; % Barrier height of left ele

ctrode [eV]

V1R=0:0.01:FIR; % Define the step size

V1L=-FIL:0.01:0; % Define the step size

ramp=0.5;

VR= FIR:.01:(FIR+FIL)\*ramp; % Define the step size

VL=(-FIL-FIR)\*ramp:.01:-FIL; % Define the step size

FIA1R=(FIR + FIL - V1R)./2; % Barrier height of left electrode [eV]

FIA1L=(FIR + FIL + V1L)./2; % Barrier height of left electrode [eV]

FIAR= FIL/2; % Barrier height of left electrode [eV]

FIAL= FIR/2; % Barrier height of left electrode [eV]

GAP=ramp\*1e-9; % Length of the gap [m]

GAP\_CM=GAP\*100; % Length of the gap [m]

```

GAPW=3e-9;

GAPH=3e-9;

GAPR = abs((GAP * FIL) . / (VR - FIR + FIL));

GAPL = abs((GAP * FIR) . / (-VL + FIR - FIL));

J01 = Q^2/2/PI/HP1./(GAP).^2;

JOR = Q^2/2/PI/HP1./(GAPR).^2;

J0L = Q^2/2/PI/HP1./(GAPL).^2;

C1 = 4* PI * sqrt(2*Me*Q) / HP1 .* (GAP);

CR = 4* PI * sqrt(2*Me*Q) / HP1 .* (GAPR);

CL = 4* PI * sqrt(2*Me*Q) / HP1 .* (GAPL);

T_AREA=GAPW*GAPH;

T_AREA_CM=T_AREA*1e4;

AREA_GAP_BOTTOM=T_AREA;

AREA_PAD=2.5E-7;

% Area of the electrode pad 5e-4m*5e-4m=2.5E-7m^2

% Quantum conductance [S]

CON_QT=2*Q^2/(HP1);

R_QT=1/CON_QT;

% Quantum resistance [R]

```

%% the low voltage tunneling current

```

J1R = J01 .* FIA1R .* exp(-C1.* sqrt(FIA1R)) - J01 .* (FIA1R+V1R) .* (FIA1R+V1R)

C1.* sqrt(FIA1R+V1R));

J1L = J01 .* FIA1L .* exp(-C1.* sqrt(FIA1L)) - J01 .* (FIA1L-V1L) .* exp(-

C1.* sqrt(FIA1L-V1L));

JR = J0R .* FIAR .* exp(-CR.* sqrt(FIAR)) - J0R .* (FIAR+VR) .* exp(-CR.*)

sqrt(FIAR+VR));

JL = JOL .* FIAL .* exp(-CL.* sqrt(FIAL)) - JOL .* (FIAL-VL) .* exp(-CL.*)

sqrt(FIAL-VL));

I1R = T_AREA * J1R;

I1L = T_AREA * J1L;

IR = T_AREA * JR;

IL = T_AREA * JL;

J1R\_CM = J1R *1e-4;

J1L_CM = J1L *1e-4;

JR\_CM = JR *1e-4;

JL_CM = JL *1e-4;

%%

figure

semilogy (V1R,I1R,'r-',V1L,I1L,'b-',VR,IR,'G-',VL,IL,'k-');

```

## 2.2 Helmholtz's free energy, Coulomb blockade and Quantum confinement

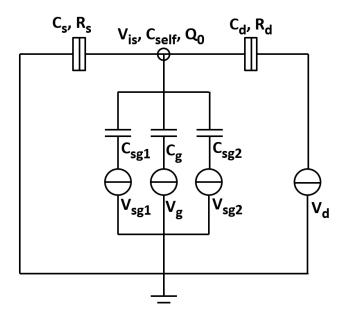

**Figure 2-5** Equivalent circuit of a single island tunneling device with source, drain and gate electrodes

For the single island tunneling device discussed in this dissertation, it usually consists of at least one electrode coupled to the island with a tunneling junction consisting of a thin dielectric and either another electrode with a tunneling junction or a gate electrode accompanied by a blocking dielectric. A tunneling junction is usually represented by a junction resistor and a capacitor in parallel. The gate electrode with a blocking dielectric is represented by a gate capacitance. **Figure 2-5** shows the equivalent circuit of a typical single island tunneling device with source and drain electrodes with two tunneling junctions, and a bottom gate electrode and two other side gate electrodes. Two other terminal single electron tunneling devices studied in this dissertation can be simplified from this model.

The energy that determines the charge transport to the SET is described by Helmholtz's

free energy (F) [17]:

$$F = E_{\Sigma} - W \tag{2-6}$$

The total electron additional energy  $E_{\Sigma}$  (EAE) stored in a SET can be written as:

$$E_{\Sigma} = E_C + E_N \tag{2-7}$$

where  $E_C$  is the Coulomb charging energy (CCE), and  $E_N$  is the quantum confinement energy (QCE). The charge of the island is the sum of the charge induced by each electrode plus an initial offset charge:

$$Q = -Ne = Q_0 + V_{is}(C_s + C_{self}) + (V_{is} - V_d)C_d + (V_{is} - V_g)C_g + (V_{is} - V_{sg1})C_{sg1} + (V_{is} - V_{sg2})C_{sg2}$$

$$(2-8)$$

The electro static capacitive energy of the island with N excess electrons can be rewritten as:

$$U(N) = \frac{1}{2}C_{tot}V_{is}^2 = \frac{(-Ne - Q_0 + V_dC_d + V_gC_g + V_{sg1}C_{sg1} + V_{sg2}C_{sg2})^2}{2C_{tot}}$$

(2-9)

where the total capacitance is given by:

$$C_{tot} = C_s + C_d + C_g + C_{sg1} + C_{sg2} + C_{self}$$

(2-10)

The calculation of the capacitance terms will be discussed in the next session. To add the N<sup>th</sup> electron to the island with N-1 electron, the energy required would be,

$$U_N(N) = U(N) - U(N-1) + E_N(N)$$

(2-11)

$$U_N(N) = \frac{e^2 \left(N - \frac{1}{2}\right)}{c_{tot}} + \frac{eQ_0}{c_{tot}} - \frac{eV_d c_d}{c_{tot}} - \frac{eV_g c_g}{c_{tot}} - \frac{eV_{sg1} c_{sg1}}{c_{tot}} - \frac{eV_{sg2} c_{sg2}}{c_{tot}} + E_N(N)$$

(2-12)

By solving  $U_N(N) = 0$  and  $V_d = 0$ , the degeneracy points can be calculated. Assuming one control gate is in use, i.e.  $V_{sg1}$  and  $V_{sg2}$  to be zero for simplification, the degeneracy points are:

$$V_g(N) = \frac{e(N-\frac{1}{2}) + Q_0}{C_g} + \frac{C_{tot} * E_N(N)}{C_g}$$

(2-13)

The periodicity of the conductance peaks in the Coulomb diamonds is:

$$T_g(N) = \frac{e}{c_g} + \frac{c_{tot}[E_N(N) - E_N(N-1)]}{c_g} \quad \text{or just} \quad T_g(N) = \frac{e}{c_g}$$

(2-14)

depending on the filling of the electron shell structure of the quantum dot. For quantum dots with size larger than 100 nm, the CCE is negligible compared to the  $\frac{e}{c_g}$  term and thus,  $T_g(N)$  can be simplified as:

$$T_g = \frac{e}{c_g} \tag{2-15}$$

The peak positions of the Coulomb diamonds can then be determined by finding the following:

$$Max(U_N(N)) (2-16)$$

Assuming a single electron charging condition, the peak energy values are:

$$E_{\Sigma}(N) = Max(U_N(N)) = \frac{e^2}{c_{tot}} + \Delta E_N(N) \quad \text{or just} \quad \frac{e^2}{c_{tot}}$$

(2-17)

For quantum dots with size larger than 100 nm again, this would become:

$$E_c = E_{\Sigma} = \frac{e^2}{c_{tot}} \tag{2-18}$$

#### 2.2.1 Classical SET – Coulomb Blockade vs. SET tunneling

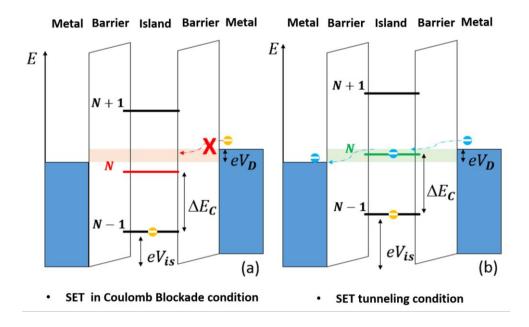

**Figure 2-6** Comparison of Coulomb Blockade vs. SET tunneling modes for a Classical SET.

**Figure 2-6** shows the energy band diagram comparing the Coulomb Blockade condition vs. SET tunneling condition for a three terminal classical SET where the QCE is ignored. The equivalent circuit is shown in the inset of **Figure 2-7**, which is a simplified condition of the one shown in **Figure 2-5**. The bias of source-drain electrodes  $V_D$  sets a window allowing charges to tunnel through the energy levels within, while tunneling through the levels out of the window is forbidden. A gate bias  $V_{is}$  offsets the potential of the island

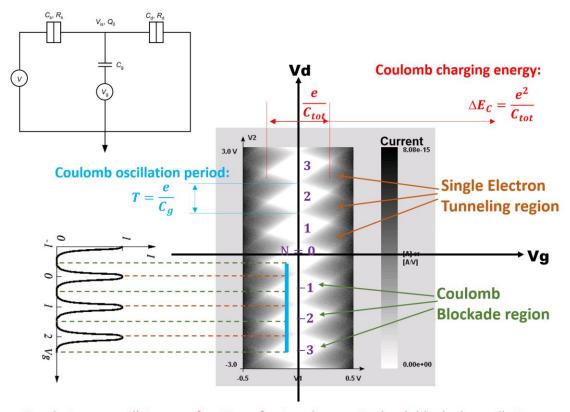

energy levels (..., N+1, N, N-1, ...0, ..., -(N-1), -N, -(N+1), ...). When no energy levels are within the tunneling window, the SET is under the Coulomb Blockade mode; when there is one energy level sitting within the window, the SET is under a single electron tunneling mode, during which one electron can either tunnel onto the island or tunnel out of the island, thus forming a single electron tunneling current. By shifting the gate bias  $V_{is}$ , it is possible to observe the periodic change between the two operation modes by measuring the Coulomb oscillation of the tunneling current. By plotting the 2D stability plot ( $V_D$   $v_s$ .  $V_{is}$   $v_s$ .  $I_D$ ), a diamond like pattern can be observed which is a result of the boundary conditions of change between the two operation modes with respect to  $V_D$  and  $V_{is}$ . Figure 2-7 shows a typical classical three terminal SET stability plot with the Coulomb diamond pattern and  $I_D$ - $V_{is}(V_g)$  characteristics showing the Coulomb oscillation, which is drastically different from the characteristics of traditional field effect transistors without the SET behavior.

• Conductance oscillates as a function of gate voltage – Coulomb blockade oscillations

**Figure 2-7** Typical classical three terminal SET stability plot with Coulomb diamond pattern and  $I_D$ - $V_{is}(V_g)$  characteristics showing the Coulomb oscillation. (Inset: the corresponding equivalent circuit)

While it is possible to allow more than one electron to tunnel at a time when having a tunneling window larger than the separation of two energy levels, it is still very difficult to observe these patterns due to the poorer S/N ratio compared to the SET condition. Hence, SET is the preferred mode rather than the multi-electron tunneling for these devices.

# 2.2.2 Room temperature Classical SET

Although most characterization of the classical SET behaviors have been performed under low temperature (< 100 K), it is possible, to operate these devices at room temperature, given that the CCE is larger than the thermal energy

$$\Delta E_C = \frac{e^2}{c_{tot}} > K_B T = 0.26 \ eV \ (T = 300 \ K)$$

(2-19)

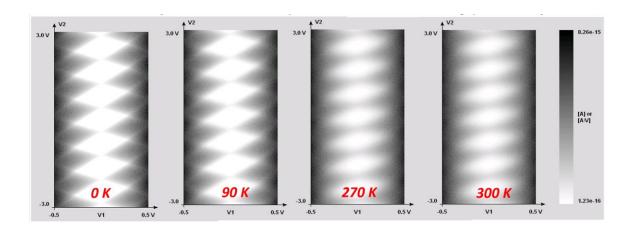

**Figure 2-8** Effect of temperature to the stability plot of a SET with a 0.98 nm Au NP as an island

**Figure 2-8** shows the effect of temperature to the stability plot of a SET with a 0.98 nm Au NP as an island. The stability plots were simulated by a Monte Carlo based simulator-SIMON2 developed by C. Wasshuber [28]. The simulation parameters and characteristic values are summarized in **Table 2-1**.

**Table 2-1** Simulation parameters and characteristic values of **Figure 2-8**.

| Parameters                   | Units | Values          |

|------------------------------|-------|-----------------|

| Gap size                     | nm    | 10              |

| Au NP size                   | nm    | 0.9             |

| Self-capacitance             | С     | 9.7635E-20      |

| Gate capacitance             | С     | 1.9571E-19      |

| Tunneling capacitance        | С     | 2.0445E-19      |

| Total capacitance            | С     | 6.0440E-19      |

| Gate/total capacitance ratio |       | 0.3234          |

| Temperature                  | K     | 0, 90, 270, 300 |

| Tunneling resistance         | Ohm   | 4.20E+13        |

| Characteristic values Units | Values |

|-----------------------------|--------|

|-----------------------------|--------|

| Periodicity:                    | eV | 0.8196 |

|---------------------------------|----|--------|

| Classic Coulomb charging energy | eV | 0.2651 |

It is clear that a high enough thermal energy defined by  $K_BT$  can assist the electron tunneling even at the boundary condition of the Coulomb Blockade and smear out the diamond pattern of the Coulomb blockade/SET tunneling. For room temperature operation of the SET, it is, therefore, necessary to reduce the total capacitance coupled to the island, essentially, reducing the size of the island and reducing the dielectric constant. The effect of dielectrics with different dielectric constants in the island is embedded in that which was simulated and shown in **Figure 2-9**. The simulation conditions are summarized in **Table 2-2**. The effect of NP size will be discussed in more detail in the next section.

**Figure 2-9** Comparison of simulated stability plot of 0.98 nm Au NP SET with (a)  $Al_2O_3$  (b)  $SiO_2$ , and (c) air, at 300 K.

**Table 2-2** Simulation parameters and characteristic values of **Figure 2-9**.

| Parameters            | Units | 5nm AL2O3  | 5nm SiO2   | no capping |

|-----------------------|-------|------------|------------|------------|

| Dielectric constants  |       | 9          | 3.9        | 1          |

| Tunneling capacitance | С     | 4.7101E-19 | 2.0445E-19 | 1.0490E-19 |

| Gate capacitance      | С     | 1.9571E-19 | 1.9571E-19 | 1.9571E-19 |

| Total capacitance     | С     | 1.1410E-18 | 6.0440E-19 | 4.0590E-19 |

| Periodicity:                    | eV | 0.8196 | 0.8196 | 0.8196 |

|---------------------------------|----|--------|--------|--------|

| Classic Coulomb charging energy | eV | 0.1407 | 0.2651 | 0.3954 |

## 2.2.3 Quantum SET – Quantum Level Spacing

For the case when the quantum dot size is not negligible, such as the sub-2 nm size nanoparticle used in this study, the  $\Delta E_N(N)$  cannot be ignored and can be generally estimated by a 2D growth model from the following:

$$\Delta E_N(N) = \left(\frac{1}{2\pi^2 N}\right)^{1/3} \frac{\hbar^2}{2m^* d^2} \tag{2-20}$$

Figure 2-10 Schematics showing the size dependent quantum-level spacing.

As illustrated in **Figure 2-10**, a smaller NP size yields larger quantum level spacing that can be observed more easily during measurements. **Figure 2-11** shows the theoretical CCE, QCE, EAE and the estimated numbers of atoms vs. the NP diameter using the above model

at 300 K. For a room temperature operational SET, an NP size smaller than 4 nm may be required. Note that in an actual case, the exact electron shell structure and QCE of a nanoparticle can be difficult to determine by simply the disk or sphere assumption due to the non-negligible effect of many different cluster structures for clusters with the same number of atoms. In this case, the cluster structure has to be exact and first principle simulation can be used to estimate the exact shell structure.

**Figure 2-11** Theoretical Coulomb Charging Energy ( $\bullet$ ), the Quantum Confinement Energy level spacing ( $\blacksquare$ ), total electron addition energy ( $\blacktriangle$ ), and the estimated numbers of atoms vs. the NP diameter (/). The dotted line indicates the thermal energy at T = 300 K.

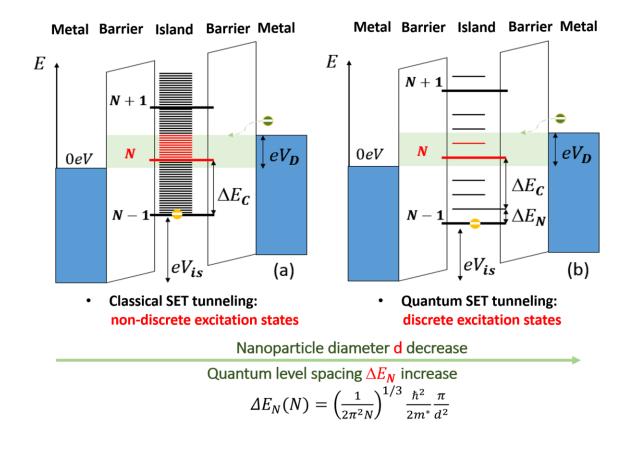

**Figure 2-12** Comparison of energy band diagram of (a) Classical SET vs. (b) Quantum SET.

**Figure 2-12** compares the energy band diagram of a classical SET vs. a Quantum SET. For the classical SET with a large size island, the quantum-level spacing is much smaller than the thermal energy which can be considered a continuous empty band or excitation states of the ground states (N-1, N, N+1) (not showed in **Figure 2-6** for simplification). Each excitation state and ground state within the tunneling window can be considered as one possible tunneling path to charge or discharge the island. Increasing the tunneling window linearly will result in a linear increase of the tunneling possibility of a charge; hence, a linear increase of tunneling current will occur in the single electron tunneling regime.

For the quantum SET, however, the quantum level spacing is comparable to the thermal

energy, resulting in discrete excitation states. Increasing the tunneling window in this case results in stepwise increase of the tunneling possibility, and hence, a stepwise increase of tunneling current, referred to as the quantum staircase effect. **Figure 2-13** compares the simulated stability plot of a classical SET (a) vs. a quantum SET (b) at 4.2K. Additional fine features (lines and smaller diamonds) due to the quantum staircase effect are observed in the single electron tunneling regime of a quantum SET compared to that of a classical SET. Note that the quantum level spacing is set as constant for **Figure 2-13** (b) which is an idealized case. In reality, these quantum level spacings are dependent on the electron shell structure of the cluster, and the energy level of each electron as illustrated in **Figure 2-13**(c). The staircase effect in the I-V characteristic is illustrated in **Figure 2-14**.

**Figure 2-13** Comparison of simulated stability plot of a (a) classical SET vs. (b) quantum SET with equal QCE vs. (c) quantum SET with unequal QCE at 4.2 K.

**Figure 2-14** Comparison of I-V characteristics of a (a) classical SET vs. (b) quantum SET with quantum staircase effect.

### 2.3 Calculation of Related Capacitance Terms of Nanoparticles

#### 2.3.1 Sphere to Plane Model

For a more precise estimation of the energy terms, all capacitances coupled to the NP are computed and summed up for the total capacitance. Due to the relatively small dimension of our Au/Pt NPs (0.5–2.5nm) compared to the size of coupling electrodes (> 30 nm) studied in this dissertation, the NP – electrode capacitance can be estimated by a sphere-plane capacitance model [29] as illustrated in **Figure 2-15**.

**Figure 2-15** Schematics of a sphere-plane capacitor for (left) a gate electrode coupled to a single NP (right), which is an embedded NP coupled to a source or drain electrode.

This capacitance is given by:

$$C = 2\pi\epsilon\sqrt{d^2 - 4a^2} \sum_{j=0}^{\infty} \left(\coth\left[\left(j + \frac{1}{2}\right) arcosh\left(\frac{d}{2a}\right)\right] - 1\right) \tag{2-21}$$

where a is the radius of the sphere, d is the distance between the sphere and the plane and  $\epsilon$  is the permittivity of the dielectric material. For a three terminal SET with source, drain and gate electrode, the three capacitance terms can be represented as

$$C_S = 2\pi\epsilon_{pen}\sqrt{d^2 - 4a^2}\sum_{j=0}^{\infty}\left(\coth\left[\left(j + \frac{1}{2}\right)arcosh\left(\frac{d}{2a}\right)\right] - 1\right) \tag{2-22}$$

$$C_D = 2\pi\epsilon_{pen}\sqrt{(g-d)^2 - 4a^2}\sum_{j=0}^{\infty}(\coth\left[\left(j + \frac{1}{2}\right)arcosh\left(\frac{g-d}{2a}\right)\right] - 1) \tag{2-23}$$

$$C_G = 2\pi\epsilon_{SiO2}\sqrt{(t_G + a)^2 - 4a^2}\sum_{j=0}^{\infty}\left(coth\left[\left(j + \frac{1}{2}\right)arcosh\left(\frac{t_{gate} + a}{2a}\right)\right] - 1\right) \tag{2-24}$$

The dielectric constants of  $SiO_2$  and pentacene that are studied in Chapter 2.3 are ~3.9 and 4, respectively. As seen in **Figure 2-16**, the bottom-gate-NP capacitance is a strong function of the NP size when the size is less than 1 nm. The smaller the spherical island, the smaller the electrode to island capacitances, and the larger the CCE. The capacitance is also a strong function of the dielectric thickness when the NP is larger than 1 nm and the dielectric layer thickness is less than 10 nm.

**Figure 2-16** Calculated bottom-gate-NP capacitance vs. NP size and dielectric thickness ( $SiO_2$  or pentacene). The cyan rectangle is the possible tunneling capacitance range of our SET studied in 2.3. In this region (0.5 nm < NP diameter < 1.5 nm, 5 nm < dielectric thickness < 20 nm), the tunneling capacitance is dependent on the NP size and somewhat independent of the dielectric thickness.

# Chapter 3. Sub-1 nm Gold Nanoparticle-based Single-Electron Transistors at Room Temperature

This chapter discusses the size-dependent charging energy and quantum level spacing of sub-1 nm gold nanoparticles (Au NPs) and their application in room temperature (RT) operable single-electron transistors (SETs). This work is a critical foundation to help explain the effects of sub-nm metal NPs on the macroscopic device structures studied in

the next few chapters. The effects of embedded Au NPs demonstrated here include their utility as discrete charge storage nodes and the ability to control and observe charge storage and transfer down to the single electron levels at ambient temperature. SETs incorporating single ~1 nm Au NPs as charge transport islands are used to study the quantum Coulomb blockade and quantized energy level spacings at RT (300 K). Monodisperse ultra-small (0.86  $\pm$  0.30 nm) Au NPs were deposited by the tilted-target sputtering (TTS) technique into 12 nm nanogaps fabricated by high-resolution e-beam lithography. Tunneling resistance was modulated to ~10 $^9$   $\Omega$  by addition of a pentacene layer, allowing clear observation of quantum staircases and Coulomb oscillations with an on/off current modulation ratio of ~100 in room temperature current-voltage (I-V) measurements. Uneven addition energy was also observed and attributed to filling of the AuNC electron shell structure. The maximum electron addition energy and quantized energy level spacing were found to be 350 meV and 172 meV, respectively, which are significantly larger than the thermal energy at 300 K (25.9 meV).

#### 3.1 Introduction

Single-electron transistor (SET) devices are promising candidates for low-power integrated circuits and ultra-high sensitivity detectors of single charges, photons, or molecules due to their operation at the single electron level and high susceptibility to charge interaction. Noble metal nanoparticles (MNPs) have proven advantageous over semiconductor clusters and organic molecules in SET applications due to their greater environmental stability, higher density of states, and mature fabrication techniques [5]–[7]. Theory predicts that MNP dimensions less than 1 nm are required for the quantum

confinement energy to surpass the RT thermal noise enough to probe single electron quantum excitation states [17]–[19]. Meanwhile, the relatively small electron charging energies of MNP-based SET devices have so far prevented clear room temperature (RT) observation of these Coulomb oscillations and quantum confinement states [17]–[19].

Fabrication and integration of monodisperse ~1 nm MNPs in a device configuration has been a major challenge in the progress of SET device technology. Recently, MNP SETs fabricated by thermal evaporation with island sizes mostly in the 5-10 nm range and some particles as small as 2 nm demonstrated Coulomb blockade and quantum confinement effects in measurements below 4.2 K [30], [31]. However, Pashkin et al. [31] reported an on/off current ratio of Coulomb oscillation of only 1.12 at 300 K, which was observed in only 1 of 56 SETs fabricated, and no quantum confinement states could be resolved. The thermal evaporation technique used for island fabrication in the aforementioned studies suffers from poor control of MNP size and size distribution, resulting in low yield of functional SET architectures and widely varying MNP size-dependent transistor properties [30], [31]. Utilizing the radially dispersed deposition flux in a tilted-target sputtering (TTS) technique, we have demonstrated monodisperse sub-2 nm Pt MNPs and their utility as discrete charge storage nodes [2], [5], [7], [20]. The TTS method demonstrates superior control on MNP size and size distribution (95% of metal islands fall in the range of 0.5– 1.5 nm), which is an important step toward improving SET yield and consistency with subnm metal islands.

Optimizing the nanogap electrode spacing into which the MNP is deposited is critical to controlling SET tunneling resistance and capacitance. In general, confining charged electrons in the MNP "quantum dot" requires that the tunneling resistance ( $R_T$ )

satisfy the condition  $R_T \ge \hbar/e^2 \approx 26 \text{ k}\Omega$  [17]–[19]. Considering the practical application of direct tunneling through a nanogap, the tunneling current should be sufficiently strong enough to be detected by a commercial low current (fA level) measurement system, which would require  $R_T < 10^{14} \Omega$ . Assuming vacuum as the dielectric, the resultant required tunneling distance (i.e., distance between electrode and MNP) is less than 2 nm. Many techniques have been developed to fabricate sub-20 nm nanogaps for SET applications within the last decade, including break junction/electron migration [30], [32], [33], scanning tunneling microscopy (STM) [34], [35], and electron beam lithography (EBL) [36]. Break junctions must be fabricated individually, making the method incompatible with traditional large-scale complementary metal-oxide semiconductor (CMOS) fabrication techniques [30], [32], [33]. Liu *et al.* [36] presented e-beam overlap and overexposure EBL techniques to fabricate nanogaps with a 15% success rate for sub-5 nm gaps and with a100% success rate for sub-10 nm gaps. Further improvement in the yield for sub-5 nm gap devices is of crucial importance for sub-1 nm MNPs.

In this work, we have incorporated ~1 nm gold MNPs (Au NPs) into EBL-generated metal nanogaps. Au NPs were deposited using the TTS technique to achieve tunable size and narrow size distributions [2], [4], [5], [7], [13], [20]–[22], [37], [38]. A loosely packed layer of organic semiconductor pentacene was thermally deposited over the whole nanogap-Au NP assembly to reduce the tunneling resistance and obtain measurable current. Clear uneven quantum Coulomb oscillations and quantum level spacings were demonstrated at 300 K. We also report unique features in the charge transport characteristics that may indicate signatures of pentacene vibronic states. More than one-third (37%) of the devices showed SET behavior with consistent characteristic single

electron behavior over the 5-day measurement time frame. To the best of our knowledge, this is the first RT demonstration of MNP quantum-level spacings in a CMOS-compatible SET.

#### 3.2 Experiment

**Figure 3-1** (a) Schematic of SET device structure; (b) SEM image of the e-beam patterned nanoelectrodes (scale bar 20  $\mu$ m); inset: nanoelectrode structure with 12 nm gap. The two side gates were not used in this study; (c) Transmission electron microscopy image of 0.86 nm Au NPs with the inset showing the Au NP size distribution. The scale bar is 20 nm; (d) AFM images of Au nanoelectrodes after pentacene deposition.

The MNP SET device schematic is illustrated in **Figure 3-1** (a). The SET substrate

consisted of heavily doped p-type silicon with Cr-Au bottom gate contacts and a 200 nm thermally grown silicon dioxide (SiO<sub>2</sub>) blocking layer. Nanogaps were patterned in a 100 nm poly(methyl methacrylate) (PMMA) resist layer using an Elionix ELS-7000 EBL system operated at 100 kV accelerating voltage and 200 pA beam current. The triangular geometries forming the gap regions were patterned using half the dose of that used for the remainder of the electrodes to enhance the precision and reproducibility of the gaps. The resist was developed in a 1:3 ratio of methyl isobutyl ketone to isopropyl alcohol (1:3 MIBK:IPA) at 0 °C followed by the deposition of 2 nm Cr as an adhesion layer for a 30 nm Au layer [39], [40]. The electrodes were then connected to larger contact pads defined by photolithography to enable electrical measurements. The pads were defined by aligning a second photo mask with the EBL-patterned nanogap electrodes followed by resist development and deposition of 100 nm Au film. The final Au nanogaps varied in length from 8–21 nm with an average gap dimension of 13 nm (**Figure 3-1** (b)). Au NPs with 0.86  $\pm$  0.30 nm diameter (range: 0.5–2.2 nm) and (5.3  $\pm$  0.3)  $\times$  10<sup>12</sup> cm<sup>-2</sup> particle number density were then synthesized by TTS technique using 10 s sputtering time, 18 W power, 38.8° target angle, and 4 m Torr working pressure (**Figure 3-1** (c)) [4], [5], [7], [20], [22], [37], [38], [41]. Pentacene was finally thermally deposited as a capping layer to reduce tunneling resistance over the whole Au nanogap-Au NP assembly (**Figure 3-1** (d)). Pentacene grain sizes obtained through AFM measurements ranged from 200–300 nm with height ranging from 30-80 nm.

Atomic force microscope (AFM, Bruker) was used to image the nanoelectrodes before and after pentacene deposition. Imaging was carried out using an SNL-10-B probe (2 nm nominal radius). Electrical characterizations were carried out in a triaxial guarded

and electromagnetic shielded probe station (Signatone WL-210E) in a dark, nitrogen environment at room temperature (~300 K). The current-voltage (I-V) measurements were taken by a Keithley 4200-SCS semiconductor characterization system with pulse generators and pre-amplifiers. During the measurement, the source was fixed at 0 V while the drain and gate electrodes were biased at different values.

#### 3.3 Discussion

#### 3.3.1 Au NP number estimation

Addressing Au NP formation within the nanogap, the Au NP size distribution and number density would be severely affected in this case of depositing Au within the nanogap. Here, it can be safely assumed the nanogaps have sharp tips, and characteristic SET electronic signatures are determined by Au NPs falling in the direct line of contact between the two tips (12 nm gap length). Thus, the nanogap region has an effective width of 2 nm. Furthermore, after considering the Au NP size distribution/number density and a deposition surface with feature sizes less than 2 nm in height, the number of Au NPs lying within the 12 nm gap can be calculated to be two or three. However, after considering the pronounced aspect ratio of the nanogap (30 nm Au sidewall height to 12 nm gap length), the number of Au atoms/clusters actually reaching the 12 nm SiO<sub>2</sub> surface is severely reduced. The acceptance angle of the cone was determined based on the positioning of the target with respect to the substrate holder [22]. This reduction in number of Au NPs reaching the SiO<sub>2</sub> surface is because a majority of the thermalized Au atoms/clusters outside the acceptance cone would more likely deposit on the Au sidewalls due to better matching between the surface energy of the Au atoms/clusters and polycrystalline Au

sidewall surface, compared to a lower energy SiO<sub>2</sub> surface. Thus, within the acceptance cone, the volume of the thermalized Au atoms clusters is reduced to just 12% of the expected value on a relatively featureless surface. This leads to the conclusion that there might be one or zero Au NPs within the 12 nm nanogap when deposited using the TTS configuration being employed here. This matches well with the observation that, although experimental features were prominently seen in the SET characteristics at room temperature for some devices (with one Au NP in the gap), some devices were found without any experimental SET indicative features, which is further indicative of zero Au NPs existing within the nanogap.

#### 3.3.2 Role of pentacene layer in electronic properties

**Figure 3-2** (a) Drain current vs. gate voltage characteristics of the devices with: (1) 0.86 nm Au NP and pentacene capping layer, (2) pentacene capping layer only, and (3) 0.86 nm Au NP only; (b) Energy band diagram for the biased SET.

**Figure 3-2** (a) shows the drain current-gate voltage (I-V) characteristics of three device configurations: (1) device with both 0.86 nm Au NP and pentacene capping layer; (2) device with pentacene layer only; and (3) device with 0.86 nm Au NP only. These I-V

curves were measured from different devices out of necessity as the order of Au and pentacene depositions required to fabricate the complete Au NP/pentacene device made it practically impossible to measure the same nanogap in all device configurations. The potential leakage current due to the pentacene conduction channel in devices (1) and (2) is dictated by variations in nanogap size (8–22 nm), pentacene coverage, and molecular arrangement within the nanogaps. The baseline current observed in device (2) is higher than device (1) for this reason. However, the actual contribution of pentacene to the leakage current in SET device (1) is difficult to separate from the contribution of Au NP. The leakage current due to the presence of pentacene may partially offset the measured transport current of the Au NP SET.