# Analysis of Performance/Accuracy Tradeoffs for Floating Point Applications on GPUs

A thesis

presented to

the Faculty of Graduate School at University of Missouri-Columbia

In Partial Fulfillment

of the Requirements for the Degree

Master of Science

by

Huyen Nguyen

Dr. Michela Becchi, Thesis Advisor

May 2016

The undersigned, appointed by the dean of the Graduate School, have examined the thesis entitled

# ANALYSIS OF PERFORMANCE/ACCURACY TRADEOFFS FOR FLOATING POINT APPLICATIONS ON GPUS

presented by Huyen Nguyen, a candidate for the degree of Master of Science, and hereby certify that, in their opinion, it is worthy of acceptance.

| Professor Michela Becchi |                              |  |  |  |  |

|--------------------------|------------------------------|--|--|--|--|

|                          |                              |  |  |  |  |

|                          |                              |  |  |  |  |

|                          | Professor Grant Scott        |  |  |  |  |

|                          |                              |  |  |  |  |

|                          |                              |  |  |  |  |

|                          | Professor Filiz Bunyak Ersoy |  |  |  |  |

**ACKNOWLEDGEMENTS**

First and foremost, I would like to express my sincere gratitude to my research advisor,

Michela Becchi. Thank you for your invaluable guidance and advice during my graduate

studies. Your ideas and contributions have had a major influence on my thesis. From you,

I have learned how to participate in groups, how to work more efficiently, and especially

how to do better research.

I would like to thank all friends in the NPS lab at Mizzou. The knowledge you have

shared and the happy environment you have created have made my time in the lab very

enjoyable. You are an indispensable factor contributing to the success of my studies.

I am thankful to my Vietnamese friends at Mizzou for bringing me a happy life at

Columbia, MO. You have helped me integrate into the community quickly and easily.

Thanks for becoming my friends during these years; our friendships will last forever. I

want to especially thank the family of Thong Thai and Nguyen Doan, the family of Tu

Vu and Lan Tran; you have made my life at Mizzou healthier with your delicious meals.

Finally, I cannot thank my family enough for their love and support. I thank my parents

for encouraging me to join graduate school; you always make my life better. I also thank

my parents-in-law for supporting me while away from home. I extremely thank my

husband – Nam Pham for taking care of our daughters and encouraging me through my

years in graduate school. I am very happy to have you by my side.

Thank you!

Huyen

University of Missouri-Columbia

May 2016

ii

## **TABLE OF CONTENTS**

| ACKNOWLEDGEMENTS                                          | ii |

|-----------------------------------------------------------|----|

| LIST OF ILLUSTRATIONS                                     | vi |

| LIST OF TABLES                                            | ix |

| ABSTRACT                                                  | xi |

| Chapter 1 Introduction                                    | 1  |

| 1.1 Contributions                                         | 3  |

| 1.2 Organization                                          | 3  |

| Chapter 2 Background                                      | 5  |

| 2.1 Floating Point Arithmetic                             | 5  |

| 2.1.1 Floating Point Definition and Notation.             | 5  |

| 2.1.2 IEEE 754 standard for Floating Point Numbers        | 7  |

| 2.1.3 Sources of Numerical Errors                         | 8  |

| 2.1.3.1 Round-off errors                                  | 8  |

| 2.1.3.2 Truncation errors                                 | 9  |

| 2.2 Composite floating point number library               | 9  |

| 2.3 GNU Multiple Precision (GMP) and CUMP                 | 11 |

| 2.3.1 GMP – The GNU Multiple Precision Arithmetic Library | 11 |

| 2.3.2 CUMP                                                | 13 |

| 2.4 Introductions to GPUs                                 | 13 |

| 2.4.1 NVIDIA GPU Architecture                             | 14 |

| 2.4.2 CUDA programming model                                             | 16              |

|--------------------------------------------------------------------------|-----------------|

| 2.4.3 Floating point for NVIDIA GPUs                                     | 17              |

| Chapter 3 Research Questions and Methodology                             | 19              |

| 3.1 Research questions                                                   | 19              |

| 3.2 Methodology                                                          | 19              |

| Chapter 4 Related work                                                   | 22              |

| Chapter 5 Global Summation                                               | 25              |

| 5.1 Global summation with GMP and CUMP                                   | 25              |

| 5.2 Global summation with single/double floating point and composite pre | ecision numbers |

|                                                                          | 30              |

| Chapter 6: Micro-benchmark for analyzing the effect of arithmetic in     | tensity on the  |

| performance/accuracy tradeoff on GPU                                     | 43              |

| Chapter 7 Gaussian Elimination and LU Decomposition (LUD) Bench          | marks 54        |

| 7.1 Introduction to Gaussian Elimination and LU Decomposition            | 54              |

| 7.1.1 Gaussian Elimination                                               | 54              |

| 7.1.2 LU Decomposition                                                   | 55              |

| 7.2 Gaussian Elimination Benchmark                                       | 57              |

| 7.3 LU Decomposition Benchmark                                           | 60              |

| Chapter 8 Micro-benchmarks for analyzing the behavior of composite       | precision       |

| multiplication and division                                              | 67              |

| Reference                                    | 83 |

|----------------------------------------------|----|

| Chapter 9 Conclusion                         | 81 |

| 8.2.2 Do-undo benchmark                      | 71 |

| 8.2.1 Background related to divisions on GPU | 69 |

| 8.2 Do-undo micro-benchmark                  | 69 |

| 8.1 Multiplication micro-benchmark           | 67 |

# LIST OF ILLUSTRATIONS

| Figure Page                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1: GMP floating point number representation                                                                                        |

| Figure 2: NVIDIA Fermi Architecture                                                                                                       |

| Figure 3: NVIDIA Fermi Streaming Multiprocessor                                                                                           |

| Figure 4: Error value propagation in Global summation                                                                                     |

| Figure 5: Accuracy of global summation                                                                                                    |

| Figure 6: Execution time (seconds) of 8M-array global summation using various                                                             |

| precisions and different kernel configurations                                                                                            |

| Figure 7: Accuracy vs. Execution time with intervals: $(10^{-2}, 10^{-1}) & (10^{+1}, 10^{+2}) \dots 39$                                  |

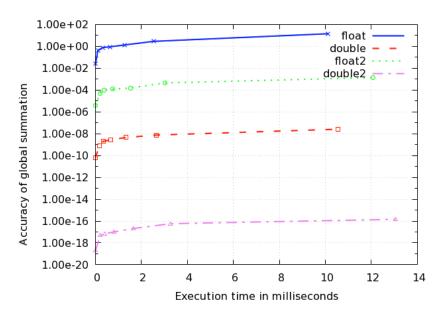

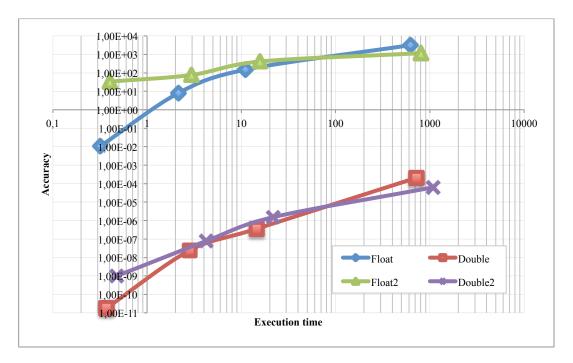

| Figure 8: Accuracy vs. Execution time with intervals: (10 <sup>-3</sup> , 10 <sup>-2</sup> ) & (10 <sup>+2</sup> , 10 <sup>+3</sup> )     |

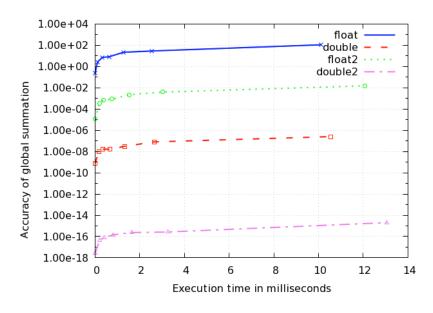

| Figure 9: Accuracy vs. Execution time with intervals: (10 <sup>-4</sup> , 10 <sup>-3</sup> ) & (10 <sup>+3</sup> , 10 <sup>+4</sup> )     |

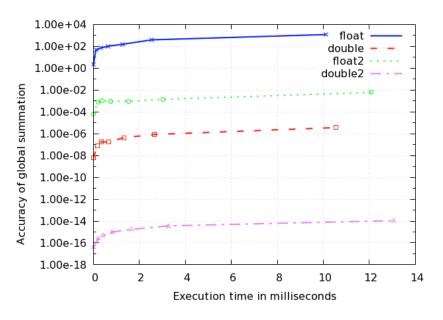

| Figure 10: Accuracy vs. Execution time with intervals: (10 <sup>-5</sup> , 10 <sup>-4</sup> ) & (10 <sup>+4</sup> , 10 <sup>+5</sup> ) 40 |

| Figure 11: Accuracy vs. Execution time with intervals: (10 <sup>-6</sup> , 10 <sup>-5</sup> ) & (10 <sup>+5</sup> , 10 <sup>+6</sup> ) 41 |

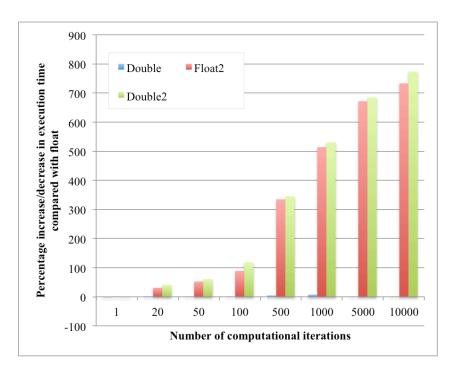

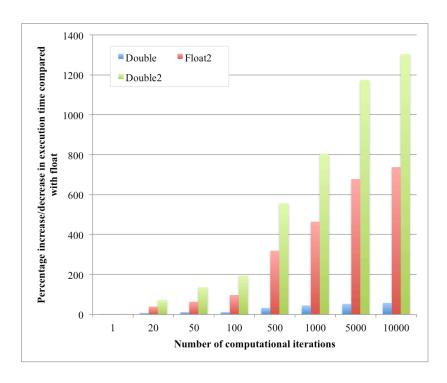

| Figure 12: Percentage increase/decrease in running time for addition kernels of compute-                                                  |

| intensive micro-benchmark with block-size = 1, grid-size = 1                                                                              |

| Figure 13: Percentage increase/decrease in running time for the addition kernel in the                                                    |

| compute-intensive micro-benchmark with grid-size = 1, block-size = 256 50                                                                 |

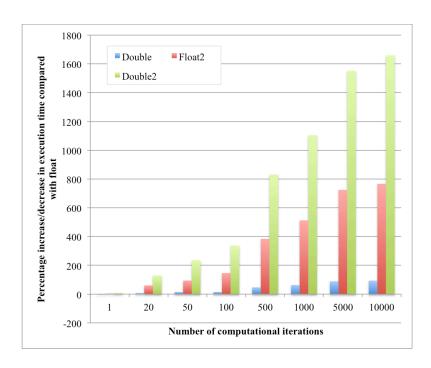

| Figure 14: Percentage increase/decrease in running time for addition kernel of compute-                                                   |

| intensive micro-benchmark with grid-size = 1, block-size = 512                                                                            |

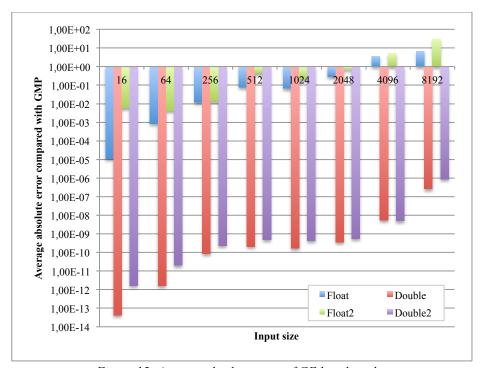

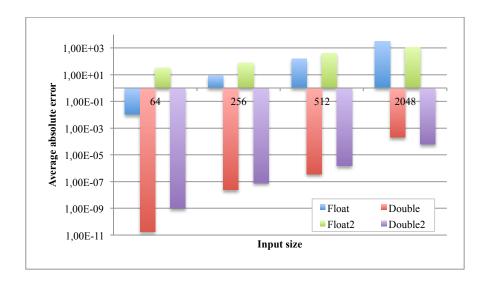

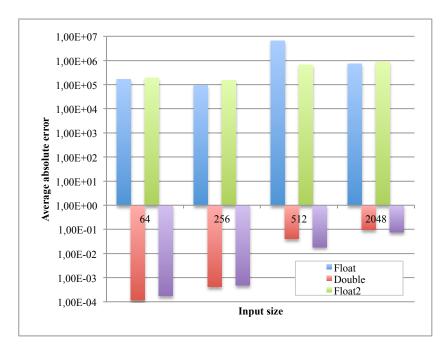

| Figure 15: Average absolute error of GE benchmark. 58                                                                                     |

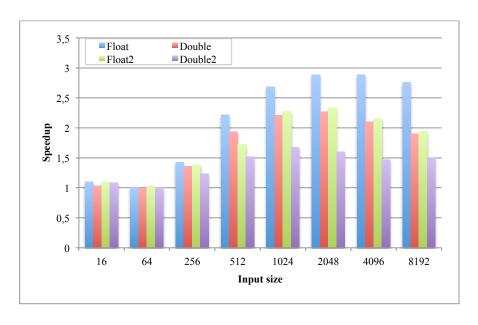

| Figure 16: Speedup of GE benchmark as we increase the block-size of the Fan2 kernel                                                       |

| from 4x4 to 8x8                                                                                                                           |

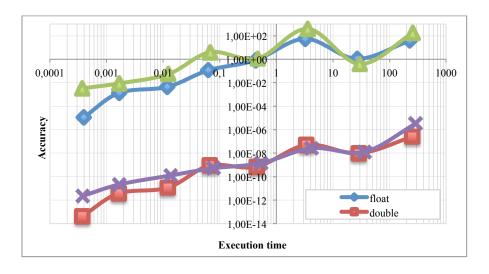

| Figure 17: | Accuracy vs. Execution time of GE benchmark                                               | 60  |

|------------|-------------------------------------------------------------------------------------------|-----|

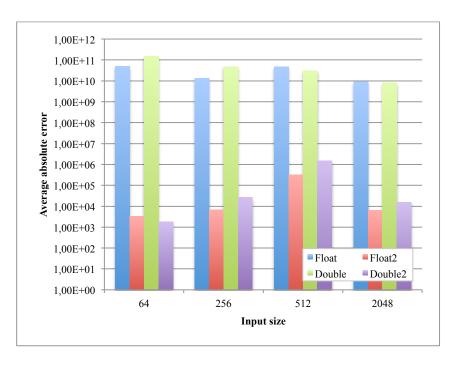

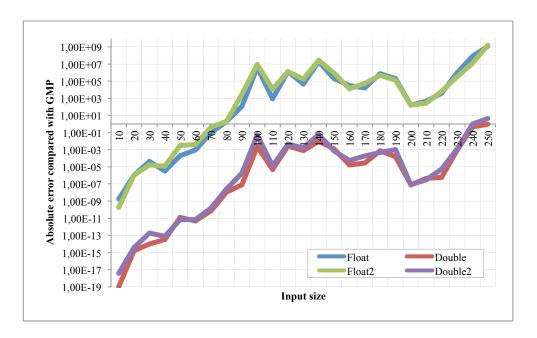

| Figure 18: | Average absolute error of LUD benchmark when the elements in the input                    |     |

|            | matrix are randomly drawn from intervals $(10^{-1}, 10^{+0}) \& (10^{+0}, 10^{+1}) \dots$ | 63  |

| Figure 19: | Average absolute error of LUD benchmark when the elements in the input                    |     |

|            | matrix are randomly drawn from intervals $(10^{-3}, 10^{-2}) & (10^{+2}, 10^{+3})$        | 63  |

| Figure 20: | Average absolute error of LUD benchmark when the elements in the input                    |     |

|            | matrix are randomly drawn from intervals $(10^{-5}, 10^{-4}) & (10^{+4}, 10^{+5})$        | 64  |

| Figure 21: | Accuracy vs. Execution time of LUD benchmark                                              | 66  |

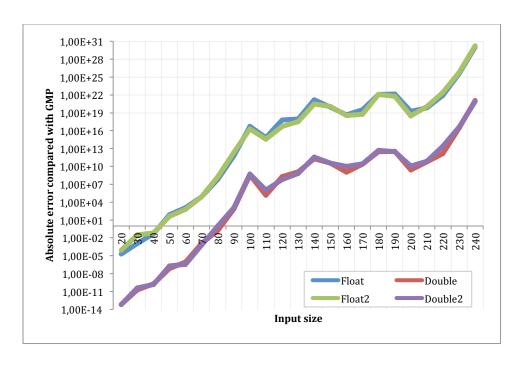

| Figure 22: | Absolute error of multiplication micro-benchmark when the input elements a                | ıre |

|            | drawn from intervals (0.1; 1.0)&(1.0; 6.0)                                                | 68  |

| Figure 23: | Absolute error of multiplication micro-benchmark when the input elements a                | ıre |

|            | drawn from intervals (0.1; 1.0)&(1.0; 10.0)                                               | 69  |

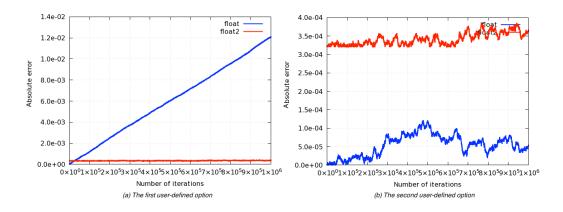

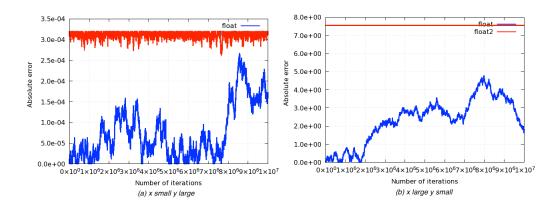

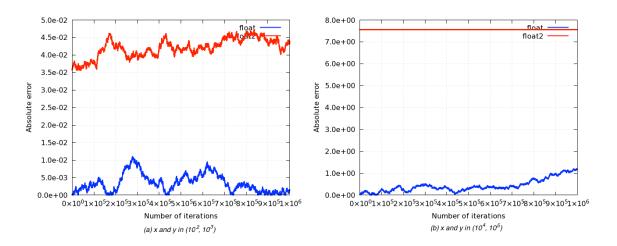

| Figure 24: | float vs. float2 absolute error of do-undo micro-benchmark withuse-fast-                  |     |

|            | math option enabled                                                                       | 75  |

| Figure 25: | the absolute error of do-undo micro-benchmark with -use-fast-math option f                | or  |

|            | 10M iterations with x small and y small                                                   | 76  |

| Figure 26: | the absolute error of do-undo micro-benchmark with –use-fast-math option f                | or  |

|            | 10M iterations with x large and y large                                                   | 76  |

| Figure 27: | the absolute error of do-undo micro-benchmark with –use-fast-math option f                | or  |

|            | 10M iterations with different magnitudes of x and y                                       | 77  |

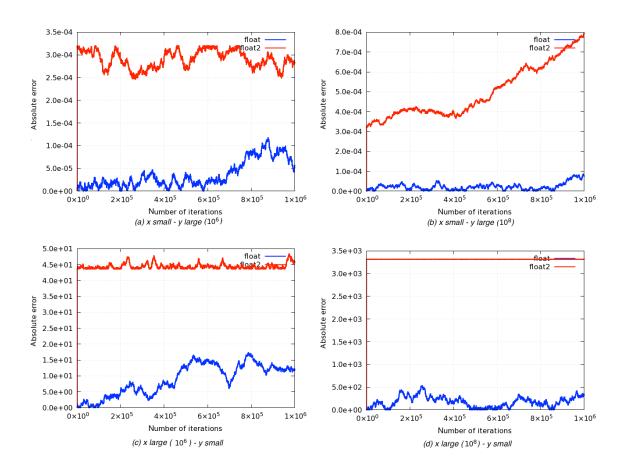

| Figure 28: | the absolute error of do-undo micro-benchmark with –use-fast-math option f                | or  |

|            | 1M iterations with different magnitudes of x and y                                        | 78  |

| Figure 29: th | e absolute error  | of do-undo | micro-benc  | hmark wit  | h –use-fast-mat | h option for |

|---------------|-------------------|------------|-------------|------------|-----------------|--------------|

| 1             | M iterations with | the same n | nagnitude o | of x and y |                 | 79           |

# LIST OF TABLES

| Table Page                                                                                      |

|-------------------------------------------------------------------------------------------------|

| Table 1: The accuracy of the global summation on CPU                                            |

| Table 2: Format of single and double precisions in IEEE 754 standard                            |

| Table 3: Data structure for single and double precision composite arithmetic                    |

| Table 4: Algorithms for the single composite floating-point arithmetic                          |

| Table 5: Fermi vs. Kepler features.                                                             |

| Table 6: Latencies (clock cycles) of math data-path 32-bit floating-point operations over       |

| Fermi and Kepler NVIDIA GPUs                                                                    |

| Table 7: Accuracy of global summation using GMP and CUMP. Device = Tesla C2075                  |

|                                                                                                 |

| Table 8: Execution time of GMP and CUMP vs. double precision                                    |

| Table 9: Number of registers using by kernels                                                   |

| Table 10: Execution time (in seconds) of global summation using CUMP with various               |

| kernel configurations. Array size = 1,048,576. Device = Tesla C2075 30                          |

| Table 11: Accuracy of global summation using various precisions and five input ranges.          |

|                                                                                                 |

| Table 12: Execution time of 8M-array global summation using various precisions and              |

| different kernel configuration, intervals: $(10^{-6}, 10^{-5}) & (10^{+5}, 10^{+6})$ , device = |

| Tesla C2070                                                                                     |

| Table 13: Execution time (in milliseconds) of compute-intensive benchmark with a                |

| varying number of computational iterations. Kernel configuration: block-                        |

| size=1, grid-size=1, device = Tesla C2070                                                       |

| Table 14: Execution time (in milliseconds) of compute-intensive benchmark with a               |      |

|------------------------------------------------------------------------------------------------|------|

| varying number of computational iterations: grid-size=1, block-size=256,                       |      |

| device = Tesla C2070.                                                                          | . 50 |

| Table 15: Execution time of compute-intensive benchmark with different computations            | al   |

| iterations. Kernel configuration: grid-size=1, block-size=512, device = Tesla                  | ì    |

| C2070                                                                                          | . 51 |

| Table 16: Running time (in seconds) of GE benchmark when the size of matrix A variety          | es   |

| from 16x16 to 8,192x8,192.                                                                     | . 59 |

| Table 17: Number and percentage of mismatches between original matrix A and the                |      |

| product of L*U for float/float2/double2 precisions                                             | . 62 |

| Table 18: LUD running time (milliseconds) on CPU                                               | . 64 |

| Table 19: LUD running time (milliseconds) in GPU                                               | . 65 |

| Table 20: Gap between $(x*y)$ and y in $(x*y)/y$ the small value is in $(0.0; 10.0)$ ; and the |      |

| large value is bigger than 10 <sup>4</sup> .                                                   | . 79 |

#### ANALYSIS OF PERFORMANCE/ACCURACY TRADEOFFS FOR

#### FLOATING POINT APPLICATIONS ON GPUS

#### Huyen Nguyen

Dr. Michela Becchi, Thesis Supervisor

#### **ABSTRACT**

Floating-point computations produce approximate results, which can lead to inaccuracy problems. Existing work addresses two issues: first, the design of high precision floatingpoint representations; second, the study of methods to trade-off accuracy and performance of serial CPU applications. However, a comprehensive study of the trade-off between accuracy and performance for multithreaded applications is missing. In my thesis, I study this trade-off on GPU. In particular, my study covers the use of different floating-point precisions (i.e., single and double floating-point precision in IEEE 754 standard, GNU Multiple Precision, and composite floating-point precision) on a variety of real-world and synthetic benchmark applications. I explore how the use of multithreading and instruction-level parallelism on GPU can allow the use of higher precision arithmetic to improve accuracy without paying in terms of execution time. As a result of my analysis, I provide insights to guide users to the selection of the arithmetic precision leading to a good performance/accuracy tradeoff depending on the arithmetic operations used in their program (addition, multiplication, division), the degree of multithreading of their program, and its arithmetic intensity.

Keywords – floating-point arithmetic; parallel computing; multithreading.

## **Chapter 1 Introduction**

Applications relying on floating-point arithmetic are common in various fields such as graphics, finance, engineering and science. Floating-point numbers are an approximation of real numbers, and therefore their use can lead to inaccuracy problems, which are often ignored by programmers. The following simple example illustrates an inaccuracy problem due to the use of floating-point arithmetic. Let us consider a large array of floating-point numbers with two properties: (i) the accurate summation of all values in the array is zero; and (ii) the absolute value of the elements in the array belongs either to a subset of very small numbers, or to a subset of very large numbers. In other words, the elements in the array may have substantially different orders of magnitude. Table 1 shows the results obtained by summing all elements of 8M-element array with these properties using single and double floating-point precision on CPU in a sequential fashion. In different columns we shows the result for arrays constructed using different intervals.

Table 1: The accuracy of the global summation on CPU

| Precision        | Intervals: $(10^{-3}, 10^{-2}) & (10^2, 10^3).$ | Intervals: $(10^{-4}, 10^{-3}) & (10^{3}, 10^{4}).$ | Intervals: $(10^{-6}, 10^{-5}) & (10^{5}, 10^{6}).$ |

|------------------|-------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|

| Single (32 bits) | -3.57E+01                                       | -2.49E+02                                           | -3.77E+03                                           |

| Double (64 bits) | 1.52E-08                                        | -2.89E-06                                           | -4.26E-05                                           |

As can be seen, in all cases the result computed is inaccurate (i.e., it is different from zero). Further, the accuracy of the computation decreases as the difference in order of magnitude of the elements increases. While the use of higher arithmetic precision can improve accuracy, it may lead to degraded performance. For some applications (such as medical studies, climate modeling, quantum theory) result accuracy is paramount; others

can tolerate a moderate loss of accuracy, especially if better accuracy comes at a cost of degraded performance. While there have been studies addressing this problem for sequential CPU computation [8][9], very little work has considered the effect of multithreading on the performance/accuracy tradeoff. The goal of this thesis work is to provide insights into performance/accuracy tradeoffs on GPU. In particular, we consider different floating-point precisions, including: single and double floating-point precision in IEEE 754 standard, GNU Multiple Precision (GMP), and composite floating-point precision defined by M. Taufer et al. [1]. Our study focuses on NVIDIA devices and uses NVIDIA CUDA as GPU programming language. However, our results can be generalized to other parallel architectures using the IEEE 754 floating point standard, as well as different parallel programming models.

Our study shows that on GPU higher precision may lead to a better tradeoff between execution time and accuracy, and provides directions on the selection of the arithmetic precision that optimizes this tradeoff. Our study covers real-world benchmark applications with different computational characteristics. As a side result, our analysis of these benchmark applications led us to the identifications of inaccuracy problems due to the use of the composite precision library designed by M. Taufer et al. [1]. To complement our analysis, we construct two micro-benchmarks: the first aims to provide better insights and a deeper examination of the effect of the arithmetic intensity and the degree of multithreading on the performance/accuracy tradeoffs, and the second aims to analyze the behavior of the multiplication and division operations using different arithmetic precisions, with a focus on composite precision.

#### 1.1 Contributions

In this thesis we make the following contributions:

- A detailed investigation of the performance/accuracy tradeoff for different floating-point precisions single precision (*float*), double precision (*double*), composite precision (*float2* based on float, and *double2* based on double), and multiple precision (*GMP*) [7] using global summation in [1] and two benchmark applications from the Rodinia Benchmark Suite [2]. We modified these applications to use all types of precisions above and run on NVIDIA GPUs.

- Micro-benchmarks to: (1) analyze the effect of arithmetic intensity on the performance/accuracy tradeoff on GPU, and (2) explain the behavior of composite precision multiplication and division.

- Insights to guide users to the selection of the arithmetic precision leading to a good performance/accuracy tradeoff depending on the arithmetic operations used in their program (addition, multiplication, division), the degree of multithreading of their program, and its arithmetic intensity.

## 1.2 Organization

The remainder of the thesis is organized into nine chapters. In Chapter 2 we provide background information. In Chapter 3 we discuss our research questions and methodology. In Chapter 4 we discuss the related work. In Chapters 5 we present and discuss results on global summation program. Chapter 6 describes the compute-intensive micro-benchmark we designed to provide an in-depth discussion of the effect of the arithmetic intensity and multithreading on the performance/accuracy tradeoff and the

results obtained by this analysis. In Chapter 7 we study the LU decomposition and Gaussian Elimination benchmarks In Chapter 8 we describe the *multiplication* and *do-undo* micro-benchmarks designed to study different types of multiplications and divisions on GPUs, and discuss the results of this analysis. In Chapter 9 we conclude and discuss future research directions.

## **Chapter 2 Background**

This chapter provides background information on floating-point arithmetic and on the GPU architecture. Section 2.1 provides a definition of floating-point arithmetic, and describes its notation and the IEEE 754 standard. In addition, it provides a discussion of the sources of floating-point inaccuracy. Section 2.2 introduces the composite floating-point precision library. Section 2.3 describes the GNU Multiple Precision library (GMP) and the CUDA Multiple precision (CUMP) libraries. Section 2.4 introduces NVIDIA GPUs including their hardware and software architecture and their floating-point support.

### 2.1 Floating Point Arithmetic

#### 2.1.1 Floating Point Definition and Notation

<u>Definition:</u> According to Wikipedia, "in computing, 'floating-point' is the formulaic representation that approximates a real number in computer language so as to support a trade-off between range and precision" [15]. The floating-point arithmetic can be less or more accurate depending on the computer hardware and configuration.

Floating-point notation: Floating-point notation is a representation of real numbers using a scientific notation [6] that allows handling very small and very large numbers. Generally, a floating-point number is composed of three parts: a *sign* that indicates whether the number is positive or negative, a *significand* (aka *mantissa*) that contains significant digits, and an *exponent* that indicates the position of the radix point (decimal point in base 10 or binary point in base 2). The scientific notation of a number is as indicated in formula (1) below.

$$number = -1^{sign} * significand * base^{exponent}$$

(1)

The *base* is the *base* of the number system in use. The floating point number for *base* two is called "binary floating-point", for base ten it is called "decimal floating-point." For instance, 12.5 could be represented in "decimal floating-point" notation as *significand* 1.25 with an *exponent* of 1 and a *sign* of 0, and in "binary floating point" notation as *significand* 1.1001 with an exponent of 3 and a *sign* of 0.

The floating-point notation has two advantages over integer data-types. First, real values between integers (real numbers) can be represented. Second, a floating-point number can represent a very large range of values because of the scaling factor (or the sliding window technique). Using sliding windows of precision, some of the less important digits can be sacrificed to let the machine represent a very large number. For example, the number 123,456,321,123 cannot be represented using the integer data-type, but it can be represented in "decimal floating-point" as a *significand* 1.2345632 (the window slides to the left) with an *exponent* of 11 and a *sign* of zero; the machine only needs to store 1.2345632, 11 and 0. The same rule applies to very small numbers; in this case, the window is slid to the right. For example, the number 0.00000001234 can be stored as a *significand* 1.234 with an *exponent* of -8 and a *sign* of zero.

A disadvantage of the floating-point representation in binary machines is that some numbers do not have an exact binary representation. Although a many numbers have a compact and exact decimal representation, they have very long or infinite expansion in binary. As a result, many decimal numbers cannot be represented exactly in binary format, and they have to be stored as approximated binary floating-point numbers in the machine. For example, there is no exact value of decimal 0.1 which has the 32-bit binary

representation as 0 01111011 1001100110011001101101 with the exponent 01111011 (123 in decimal) and infinite digits of *significand* 1001 1001 1001 1001 1001 ...

The advantage of the sliding window technique is also a disadvantage of the floating-point representation, since it causes the truncation of some of the least significant bits. The number 123,456,321,123 is represented by  $1.2345632 \times 10^{11}$ , and the last digits "1123" are lost.

#### 2.1.2 IEEE 754 standard for Floating Point Numbers

IEEE 754 is the IEEE standard for binary floating-point arithmetic established in 1985, and commonly used in most of modern hardware and programming languages. According to the IEEE 754 standard, a floating-point number is encoded into 3 components:

- A one-bit sign field: this leftmost bit indicates whether the number is positive (sign bit = 0) or negative (sign bit = 1).

- An *exponent* field: the exponent can be negative as well as positive (signed). To store the exponent as an unsigned integer, the technique "biasing" is used and the stored exponent is called "biased exponent". In this technique, before storing into a floating-point format, a positive bias number (127 for single, 1023 for double or  $2^{n-1} 1$  for n-bit exponent) is added to the real exponent. For instance, if the exponent is 3, the stored exponent field is 130 for single, and 1026 for double.

- A *significand* field: these bits combined with the implicit leading significant bit with value 1 except for subnormal numbers and zero give the true *significand*.

The distributions of these fields for 32-bit single precision (*float* type in C) and 64-bit double precision (*double* type in C) are indicated in Table 2.

Table 2: Format of single and double precisions in IEEE 754 standard

| Format           | Total bits | Sign | Exponent | Significand | Smallest                   | Largest              |

|------------------|------------|------|----------|-------------|----------------------------|----------------------|

| Single precision | 32         | 1    | 8        | 23          | ~1.2 * 10 <sup>-38</sup>   | $\sim 3.4 * 10^{38}$ |

| Double Precision | 64         | 1    | 11       | 52          | ~2.23 * 10 <sup>-308</sup> | ~1.8 * 10308         |

The floating-point notation has a specific representation for the following special numbers: *zero* is represented with *exponent* 0 and *significand* 0; *infinity* is represented with *exponent* 255 and *significand* 0; *NaN (not-a-number)* is represented with stored 255 and non-zero *significand*.

The value of an IEEE floating point number is computed using formula (2) below, in which m is the number of significant bits, and e is the stored exponent.

$$(-1)^{sign} * (1 + \sum_{i=1}^{m} b_{m-i} 2^{-i}) * 2^{(e-bias \ number)}$$

(2)

For example:

#### 2.1.3 Sources of Numerical Errors

Numerical errors happening during the computations are the combined effect of two types of errors: *round-off errors* (due to limited precision of representation) and *truncation errors* (limited time of computation).

#### 2.1.3.1 Round-off errors

Round-off errors occur because it is impossible to represent exactly all real numbers in binary format. Each machine-hardware uses a finite number of precision bits (n bits) to store and manipulate (finite or infinite) real numbers that require more than n bits, leading to an approximation.

Although the round-off error can be small for a given numerical step, it can be accumulated and become significant after a number of iterations. Our research focuses on this kind of error.

#### 2.1.3.2 Truncation errors

A truncation error corresponds to the fact that a process is terminated, or a mathematical procedure is approximated after a certain finite number of steps, and the approximation result differs from the mathematical result.

For example, when using logarithms, exponentials, trigonometric functions, hyperbolic functions, the infinite term  $\infty$  is replaced with a finite term n ( $\sum_{i=0}^{\infty} a_i x^i \rightarrow \sum_{i=0}^{n} a_i x^i$ ). The truncation error is  $\sum_{i=n+1}^{\infty} a_i x^i$ .

## 2.2 Composite floating point number library

Because of the hardware limitation, traditional floating-point numbers cause numerical errors that cannot be accepted in many applications requiring high accuracy. To improve the accuracy of applications, many scientists have explored techniques to extend the available precision in software. In 1971, Dekker [3] introduced a technique for expressing multi-length floating-point arithmetic in terms of single-length floating-point arithmetic. In particular, he illustrated a method to split a floating-point number into two half-length floating-point numbers.

The pseudo-code of the splitting method is below:

```

Error-free split of a floating-point into two parts [hx, tx] \ split \ (float \ x) \ \{ c = fl(2^{t1}+1); \ // \ t1 = 12 \ for \ single \ or \ t1 = 27 \ for \ double p = fl(x \ X \ c)

```

```

hx = fl(p - (p - x));

tx = fl(x - hx);

```

Dekker's splitting method has been used in several studies, including Thall's work on the use of extended-precision floating-point numbers for GPU computation [4]. More recently, Taufer et al. [1] have redefined the extended-precision arithmetic described in [4] and introduced the composite floating-point arithmetic library that we use in this thesis.

The single composite floating-point precision representation (*float2*) proposed in [1] is a data structure consisting of two single floating-point numbers: a *value* component and an *error* component. The single precision value of a composite precision number is the addition of its value and error components.

Similarly, the double composite floating-point precision (*double2*) uses two double floating-point numbers to represent a number. The data structures of single and double composite floating-point numbers are presented in Table 3.

Table 3: Data structure for single and double precision composite arithmetic.

```

struct float2{

float x; // x2.value

float y; //x2.error

} x2;

float x2 = x2.x + x2.y; // x2.value +

x2.error;

struct double2{

double x; // x2.value

double y; //x2.error

} x2;

double x2 = x2.x + x2.y; // x2.value +

x2.error;

```

In the composite precision library in [1], multiple single precision additions, subtractions, multiplications, as well as reciprocal are used to perform single composite precision addition, subtraction, multiplication, and division. Not only do the composite precision algorithms perform the calculation, but they also keep track of the error. Table 4 shows that single composite precision addition and subtraction require four single precision additions and four single precision subtractions; single composite multiplication requires

four single precision multiplications and two single precision additions; single composite division needs a single floating-point reciprocal, four single precision multiplications, one single precision addition, and one single precision subtraction. These algorithms obviously slow down the performance because of the extra operations.

Table 4: Algorithms for the single composite floating-point arithmetic

| Addition          |                                          | Subtraction     |                                |  |

|-------------------|------------------------------------------|-----------------|--------------------------------|--|

| Pseudo Code       | Implementation                           | Pseudo Code     | Implementation                 |  |

| float2 x2, y2, z2 | float2 x2,y2,z2                          | float2 x2,y2,z2 | float2 x2,y2,z2                |  |

| z2 = x2 + y2      | float t                                  | z2 = x2 + y2    | float t                        |  |

| _                 | z2.value= x2.value + y2.value            | _               | z2.value= x2.value + y2.value  |  |

|                   | t = z2.value - x2.value                  |                 | t = z2.value - x2.value        |  |

|                   | z2.error = x2.value                      |                 | z2.error = x2.value            |  |

|                   | - (z2.value -t)                          |                 | - (z2.value -t)                |  |

|                   | + (y2.value -t)                          |                 | + (y2.value -t)                |  |

|                   | + x2.error                               |                 | + x2.error                     |  |

|                   | + y2.value                               |                 | + y2.value                     |  |

|                   | Multiplication                           |                 | Division                       |  |

| Pseudo Code       | Implementation                           | Pseudo Code     | Implementation                 |  |

| float2 x2,y2,z2   | float2 x2,y2,z2                          | float2 x2,y2,z2 | float2 x2,y2,z2                |  |

| z2 = x2 * y2      | float t                                  | z2 = x2 / y2    | float t, s, diff               |  |

|                   | z2.value= x2.value * y2.value            |                 | t = (1/y2.value)               |  |

|                   | <pre>z2.error= x2.value * y2.error</pre> |                 | s = t * x2.value               |  |

|                   | + x2.error * y2.value                    |                 | diff = x2.value                |  |

|                   | + x2.error * y2.error                    |                 | - (s * y2.value)               |  |

|                   |                                          |                 | z2.value = s + t * diff        |  |

|                   |                                          |                 | <pre>z2.error = t * diff</pre> |  |

|                   |                                          |                 |                                |  |

## 2.3 GNU Multiple Precision (GMP) and CUMP

## 2.3.1 GMP – The GNU Multiple Precision Arithmetic Library

GMP [7] is a free library for arbitrary-precision arithmetic, operating on integers, rational numbers, and floating-point numbers. Arbitrary-precision arithmetic, also called big-num arithmetic, multiple precision arithmetic, or sometimes infinite-precision arithmetic, indicates that calculations are performed on numbers whose digits of precision are limited by the available memory of the host system. In principle, arbitrary-precision arithmetic should be able to allocate additional space dynamically whenever the accurate representation of a variable requires it. However, the current version of the GMP library

(GMP 6.0.0) supports the automatic expansion of the precision only of integer and rational numbers. The precision of floating point numbers in GMP has to be chosen statically, and the size of the variables doesn't change after initialization.

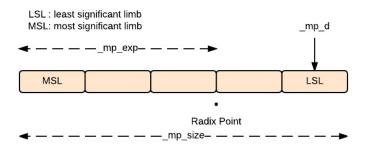

GMP floating-point numbers are stored in objects of type  $mpf_t$  and functions operating on them have the  $mpf_t$  prefix. The GMP floating-point representation is illustrated in Figure 1.

Figure 1: GMP floating point number representation

The GMP floating-point representation is based on the following definitions:

- *limb*: the part of a multi-precision number that fits in a single word. Normally a limb contains 32 or 64 bits. The C type of limb is *mp limb t*.

- \_mp\_size: the number of current limbs used to represent a number, or the negative of that if the represented number is negative. If the number is zero: \_mp\_size and \_mp\_exp are zero, \_mp\_d is unused.

- \_mp\_prec: the precision of the mantissa, in limbs. At initialization, given number of precision bits, GMP library computes mp\_prec, and (mp\_prec + 1) limbs are allocated to \_mp\_d. If there is a carry while implementing GMP floating point operations, the carry value is stored in the extra limb. \_mp\_size can be smaller than \_mp\_prec, if a represented number need less limbs; \_mp\_size can be larger than \_mp\_prec when we use all (mp\_prec + 1) allocated limbs.

- \_mp\_d: A pointer to the array of limbs, which is the absolute value of the mantissa. \_mp\_d[0] points to the least significant limb and \_mp\_d[ABS(\_mp\_size)-1] points to the most significant.

- \_mp\_exp: The exponent, in limbs, decides the position of the implied radix point.

If \_mp\_exp is zero, the radix point is just above the most significant limb. If \_mp\_exp is positive, the radix point offset is between the most significant limbs and the least significant limbs. Negative exponents shows that a radix point is further above the highest limb.

#### 2.3.2 CUMP

The CUDA Multiple Precision Arithmetic Library (CUMP) [10] is a free library for arbitrary precision arithmetic on CUDA, operating on floating point numbers. It is based on the GNU MP library (GMP). CUMP provides functions for host and device codes, the former operating on CPU and the latter operating on GPU.

CUMP supports only a restricted amount of the functionality of the original GMP library. Specifically, in the current version CUMP only supports three arithmetic operations: addition, subtraction, and multiplication.

### 2.4 Introductions to GPUs

Graphic Processing Units (GPUs) were originally designed for graphics processing. Nowadays, modern GPUs are not only a very powerful computer-graphics and image-processing engine, but also an efficient accelerator for parallel computing and data intensive applications. Thanks to the rapid increase in their computational power and programmability (through the advent of the CUDA programming model), more and more

scientists have progressively accelerated their applications on GPUs. In this section, we give a brief introduction to NVIDIA GPUs that we use in our research.

#### 2.4.1 NVIDIA GPU Architecture

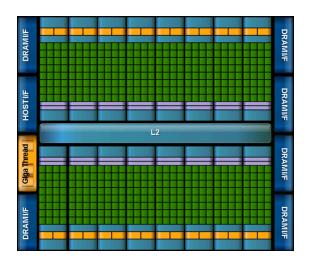

Modern NVIDIA GPUs are composed of multiple highly threaded Streaming Processors (SMs). Figure 2 shows the architecture of a Fermi GPU that consists of 16 SMs.

Figure 2: NVIDIA Fermi Architecture

The general architecture of a single SM contains:

- Several Streaming Processors (SPs) (also called single-precision CUDA cores),

- Double-precision units (DFUs),

- Special function units (SFUs),

- Load/store units (LD/ST),

- A register file,

- A shared memory/cache.

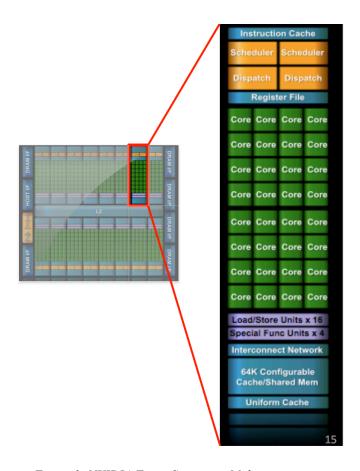

Figure 3 shows the design of a SM in the Fermi architecture.

Figure 3: NVIDIA Fermi Streaming Multiprocessor

Table 5 provides a brief comparison between the NVIDIA Fermi and Kepler GPU architectures. From Fermi to Kepler, the number of CUDA cores has increased by a factor 6.42 (from 448 to 2880 cores). Higher clock rates allow faster instruction execution by each core, but lead to higher power consumption. To limit the power consumption, the clock frequency has been slightly reduced moving from Fermi to Kepler GPUs.

Table 5: Fermi vs. Kepler features

|                                                  | Fermi GF100 [11][13]<br>(Tesla C2070) | Kepler GK110 [12][14]<br>(Tesla K40c) |

|--------------------------------------------------|---------------------------------------|---------------------------------------|

| Number of SMs                                    | 14                                    | 15                                    |

| SPs per SM                                       | 32                                    | 192                                   |

| DFUs per SM                                      | 16                                    | 64                                    |

| SFUs per SM                                      | 4                                     | 32                                    |

| LD/STs per SM                                    | 16                                    | 32                                    |

| Registers per block                              | 32768                                 | 65536                                 |

| Shared memory per block                          | 49152 bytes                           | 49152 bytes                           |

| GPU max clock rate                               | 1147 MHz (1.15 GHz)                   | 745 MHz (0.75 GHz)                    |

| Peak double-precision floating point performance | 515 GFLOPS                            | 1.43 TFLOPS                           |

| Peak single-precision floating point performance | 1 TFLOPS                              | 4.29 TFLOPS                           |

| Warp Schedulers per SM                           | 2                                     | 4                                     |

| Dispatch unit per SM                             | 2                                     | 8                                     |

| Max of active threads per SM                     | 1536                                  | 2048                                  |

| Max of threads per block                         | 1024                                  | 1024                                  |

| Max of active blocks per SM                      | 8                                     | 16                                    |

#### 2.4.2 CUDA programming model

For both Kepler and Fermi GPUs, a CUDA application generally spawns hundreds to thousands of threads to populate the SM and hide memory accesses/computation pipeline latency. From the programmer's perspective, the work is partitions across threads, the threads are grouped into thread blocks, and the thread blocks are grouped into grids. Each block is mapped to one SM at execution time, and threads within a block are split into warps. The warp is the basic scheduling unit of NVIDIA GPUs, and contains 32 threads. Because the scheduler issues instructions in warps, the block-size (number of threads per block) should be a multiple of the *warp-size* (32 threads) to avoid wasting threads. For example, if the kernel configuration has a *block-size* 16 threads, the instruction is still issued to 32 cores, and 16 cores are wasted. The *grid-size* can be assigned based on the number of active threads and blocks on a SM.

In addition, when considering occupancy and massive parallelism, the registers and shared memory resource are also significant. If a kernel requires too many registers, it limits the number of active threads. This limitation will be explored in Chapter 5.

#### 2.4.3 Floating point for NVIDIA GPUs

The capabilities of NVIDIA GPUs have been expanded in each hardware generation from only supporting single precision in early NVIDIA architectures, to fully supporting IEEE single, double precision, and including FMA (Fused-Multiply-Add) operations in modern generations such as Fermi and Kepler GPUs. CUDA classifies different GPU generations using the compute-capability number [16]; the compute capability of a GPU device can be queried by a specific CUDA function call. Below, we detail the GPU support provided in GPU with different compute capabilities.

- Compute capability 1.2 and below only support single precision floating point arithmetic. Moreover, on these GPU devices not all single precision operations are IEEE compliant, possibly leading to high level of inaccuracy.

- Compute capability 1.3 supports both single and double precision arithmetic, and offers double-precision FMA operations. Single precision in these devices keeps unchanged from previous compute capabilities. Double precision in compute capability 1.3 devices is IEEE compliant. Double-precision FMA operations combine a multiply and an addition with only one rounding step; the resulting operation is faster and more accurate than separate multiply and addition. Compute capability 1.3 does not support single precision FMA.

- Compute capability 2.0 and above fully support IEEE compliant single and double precision arithmetic, and include both single and double FMA operations.

The experiments in this thesis are performed on Tesla C2050/C2070 (Fermi GPU with compute capability 2.0) and Tesla K40C (Kepler GPU with compute capability 3.5), both supporting IEEE-compliant single and double precision arithmetic. The newest NVIDIA

GPU architecture – called Maxwell – also supports 16-bit precision, but we will not focus on this device. Table 5 shows additional features related to floating-point support on Fermi and Kepler architectures; namely: the number of single/double precision units (SPs/DFUs) per SM (SPs/DFUs in Fermi is 32/16, in Kepler is 192/64), and the peak performance of floating-point operations.

Table 6 reports the latencies of 32-bit floating-point operations over Fermi and Kepler NVIDIA GPUs based on the research in [17].

Table 6: Latencies (clock cycles) of math data-path 32-bit floating-point operations over Fermi and Kepler NVIDIA GPUs

| Operation       | Fermi GF106 | Kepler GK104 |

|-----------------|-------------|--------------|

| ADD, SUB        | 16          | 9            |

| MAX, MIN        | 20          | 9            |

| MAD             | 18          | 9            |

| MUL             | 16          | 9            |

| DIV             | 1038        | 758          |

| fadd_*()        | 16          | 9            |

| fmul_*()        | 16          | 9            |

| fdivdef()       | 95          | 41           |

| sinf(),cosf()   | 42          | 18           |

| tanf()          | 124         | 58           |

| _exp2f()        | 98          | 49           |

| expf(),exp10f() | 114         | 58           |

| _log2f()        | 46          | 22           |

| logf(),log10f() | 94          | 49           |

| powf()          | 143         | 62           |

| sqrt()          | 216         | 181          |

## **Chapter 3 Research Questions and Methodology**

#### 3.1 Research questions

In this thesis, we focus on answering the following questions:

- How GPU multithreading affects the tradeoff between accuracy and performance?

- How the arithmetic intensity of a program affects the performance/accuracy tradeoff on GPU?

- How the kind of floating-point operation executed in a program affects the accuracy?

- Why and when one precision should be replaced by another precision?

- How the use of division in CUDA programming affects the accuracy and performance of the program?

## 3.2 Methodology

To answer the above questions, it is important to thoughtfully select appropriate benchmark applications. Naturally, the combination of these benchmarks should reflect all angles of our research. We selected the following benchmark applications.

• Global summation [1]: this numerical benchmark performs the summation of an array of values whose "accurate" sum is known to be equal to zero. Our goal is to observe the accuracy of different precisions, and this benchmark gives us a good reference — the zero "correct" sum. We modified the global summation benchmark described in [1] to use single precision, double precision, composite precision and GMP for both original single-block version and modified multi-

- block version. Overall, this benchmark allows answering most of the questions related to addition and subtraction operations.

- LU Decomposition (LUD) and Gaussian Elimination benchmarks from the Rodinia benchmark suite [2]: the Rodinia benchmark suite is very popular in high performance computing. LUD and Gaussian Elimination are two applications that use floating-point numbers. These applications use the combination of different operations (addition, subtraction, multiplication, division), and allow us to evaluate the general accuracy/performance tradeoff of the different floating-point precisions in consideration. These applications have multi-block configurations that we can directly use to analyze the performance of the programs at different degrees of multithreading. We modified these applications to use different floating-point precisions. Besides using the input matrices publicly available for these benchmarks, we generate random matrices that include elements with various orders of magnitude so as to study their effect on the accuracy of the results.

- *Do/undo* benchmark [1]: this application performs a combination of multiplication and division operations. Specifically, a reference x variable is repeatedly multiplied and divided by a sequence of y variables. The expected result of the computation is the original x. This do/undo benchmark enables us to analyze the effect of different types of division on accuracy.

After modifying the benchmark applications above to use the considered floating-point precisions and datasets, we analyze their register and memory requirements and, with the aid of the CUDA occupancy calculator, we determine degrees of multithreading that

should be considered in the analysis. In addition, we profile the applications and study their PTX assembly code to determine the arithmetic intensity of each application and the number and kind of instructions it performs.

For applications for which the accurate results are not known a priori, we use the result of the GMP library as a reference.

The benchmark applications above are only the starting point of our analysis. To be able to generalize our analysis and findings, and to better understand our observations, we constructed two micro-benchmarks:

- Micro-benchmark for analyzing the affect of arithmetic intensity on the performance/accuracy tradeoff on GPU.

- Micro-benchmark for explaining the behavior of composite precision multiplication and division.

## **Chapter 4 Related work**

We first explored the single floating-point composite precision library [1]. As explained in Chapter 2, a single floating-point composite number is composed of two single precision floating-point numbers, the *value* and the *error*. The composite number value, n, is the sum of two single floating-point numbers as in formula (1).

$$n = n_{value} + n_{error} (1)$$

The approximation error of the arithmetic operation such as the sum or the product of two numbers is stored in n<sub>error</sub>. Our thought was that we could monitor the change of n<sub>error</sub> and decided to increase the precision when the error reached a threshold level. The idea was more stable when we implemented a floating-point program using GNU multiple precision library (GMP). This arbitrary precision arithmetic library provided us an unlimited precision bits to represent a real number, and so gave the accurate results. In theory, GMP library should automatically change the precision when needed, but the truth was that GMP only supported the dynamic change precision bits for integer datatypes. For floating-point numbers, we had to declare the number of necessary precision bits. Because of that reason we thought about a library that could change the precision of floating-point numbers dynamically (the precision we chose included single floatingpoint (float), double floating-point (double), composite number (float2, double2)). We then began to study the necessary materials and tools to support our ideas. During this period of the research, we have learned and practiced the function of extracting floatingpoint numbers into three components: sign, exponent and mantissa; we have also learned the techniques to split a floating-point number into two floating-point numbers [3][4][5].

Beside of those papers mentioned in this section, the dynamic tool – PRECIMONIOUS [8] – is one of my motivations to think about the idea of dynamic library. This tool has four main components to assist users for tuning the precision of floating-point numbers. In the first component, the search file is created based on the input program in LLVM bitcode format and the number of floating-point types, and this search file contains all variables needed to be tuned. In the second component, all valid type configurations are found using the authors' LCCSearch algorithm. In the third component, all program versions corresponding to all valid configurations are generated in the LLVM bitcode format. In the last component, results produced by all new program versions are compared with the result of original version, and the running times of all versions are computed and compared with the running time of original version. After checking and comparing, the PRECIMONIOUS give proposed configuration that can give the correct answer with appropriated performance. However, this tool is only used on CPU, and has many limitations including modifying at source code level, lack of communication between variable etc. The idea about dynamically changing precision that can be used on GPUs is formed.

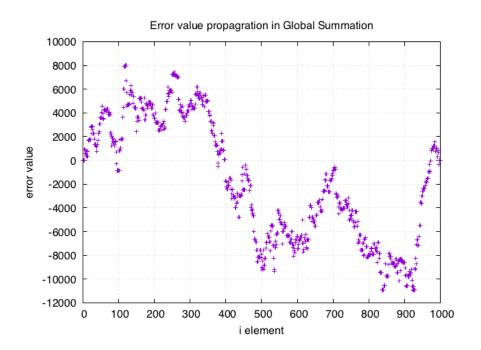

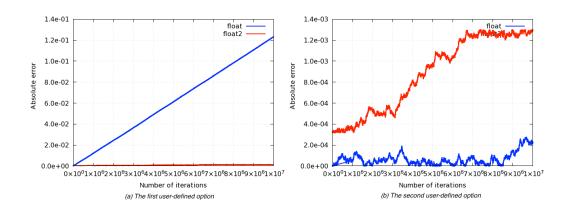

Unfortunately, from the basic functions we started to monitor the error and built our dynamic library, but we received unexpected results. Figure 4 show that the n<sub>error</sub> in composite library was unpredictable because it could be both negative and positive number, thus the error could not increase gradually. After a period of time trying many ways to have better control on n<sub>error</sub> and getting disappointed results, we had to change our direction and start our new idea that is to make a study considering accuracy and

runtime for multithreaded applications with different size of dataset. This is the basic idea for this thesis.

Figure 4: Error value propagation in Global summation

# **Chapter 5 Global Summation**

This chapter presents an analysis of numerical accuracy and performance issues found in the global summation benchmark described by Taufer *et al.* [1] due to the use of floating point arithmetic. We analyze the global summation benchmark not only using single precision floating-point (*float*) and single composite precision (*float2*) arithmetic as in [1], but also using multiple precision (GMP *mpf\_t*), double precision floating-point (*double*), and double composite precision (*double2*) arithmetic. First, we modify the global summation program to use multiple-precision arithmetic: namely, the GMP library on CPU, and the CUMP library on GPU. On GPU, we extend the single thread-block GPU kernel proposed in [1] so as to allow also experiments with multiple thread-blocks. Then, we extend the global summation kernel to use *double* and *double2* (beside *float* and *float2*) arithmetic. Our goal is to study the performance-accuracy tradeoff of global summation at different degrees of multithreading.

# 5.1 Global summation with GMP and CUMP

The global summation program was introduced to evaluate the composite precision library described in [1]. This program calculates the summation of an array of floating point values on CPU and GPU. The input array can be configured to contain numbers of various orders of magnitude; the content of the array is automatically generated so as to have a known accurate sum of zero. When using floating-point arithmetic, the sum of a very large and a very small number may lead to the small term to be neglected (cancellation). This, in turn, may lead to inaccuracy problems in the global summation of

sets of numbers with different orders of magnitude. The resulting inaccuracy depends on the arithmetic precision and the order of magnitude of the elements in the array.

Because of the two properties: (1) the array contains a subset of very small numbers and a subset of very large numbers, and the magnitude of small and large numbers can be configured; (2) the correct summation of the array is zero, we choose this program to start our study.

To learn how multiple precision numbers can improve the accuracy and study their effect on the performance, we first analyze the GMP – CUMP version of the global summation when increasing the number of precision bits, and for different gaps between the small and large numbers. Specifically, we observe the program on both CPU and GPU with four GMP configurations: 32-bit (2x64-bit limbs), 64-bit (2x64-bit limbs), 128-bit (3x64-bit limbs), and 256-bit (5x64-bit limbs). In addition an, we consider five ranges of input intervals as below:

- Range 1: Small number  $(10^{-01}, 10^{+00})$  and Large number  $(10^{+00}, 10^{+01})$

- Range 2: Small number  $(10^{-04}, 10^{-03})$  and Large number  $(10^{+03}, 10^{+04})$

- Range 3: Small number  $(10^{-13}, 10^{-12})$  and Large number  $(10^{+12}, 10^{+13})$

- Range 4: Small number  $(10^{-19}, 10^{-18})$  and Large number  $(10^{+18}, 10^{+19})$

- Range 5: Small number  $(10^{-37}, 10^{-36})$  and Large number  $(10^{+36}, 10^{+37})$

Table 7: Accuracy of global summation using GMP and CUMP. Device = Tesla C2075

| Array Size = 1024 element                                                                    |          |          |           |           |

|----------------------------------------------------------------------------------------------|----------|----------|-----------|-----------|

| Sequential (CPU)                                                                             |          |          |           |           |

| Format:                                                                                      | mpf_t 64 | mpf_t 32 | mpf_t 128 | mpf_t 256 |

| Range 1: (10 <sup>-01</sup> , 10 <sup>+00</sup> ) & (10 <sup>+00</sup> , 10 <sup>+01</sup> ) | 0.00E+00 | 0.00E+00 | 0.00E+00  | 0.00E+00  |

| Range 2: $(10^{-04}, 10^{-03}) & (10^{+03}, 10^{+04})$                                       | 4.07E-19 | 0.00E+00 | 0.00E+00  | 0.00E+00  |

| Range 3: $(10^{-13}, 10^{-12}) & (10^{+12}, 10^{+13})$                                       | 6.44E-18 | 2.01E-18 | 0.00E+00  | 0.00E+00  |

| Range 4: (10 <sup>-19</sup> , 10 <sup>-18</sup> ) & (10 <sup>+18</sup> , 10 <sup>+19</sup> ) | 9.60E+01 | 9.60E+01 | 6.51E-18  | 0.00E+00  |

| Range 5: (10 <sup>-37</sup> , 10 <sup>-36</sup> ) & (10 <sup>+36</sup> , 10 <sup>+37</sup> ) | 0.00E+00 | 0.00E+00 | 5.34E-18  | 0.00E+00  |

| Parallel (GPU)                                                                               |          |          |           |           |

| Format:                                                                                      | cump 64  | cump_32  | cump_128  | cump_256  |

| Range 1: (10 <sup>-01</sup> , 10 <sup>+00</sup> ) & (10 <sup>+00</sup> , 10 <sup>+01</sup> ) | 0.00E+00 | 0.00E+00 | 0.00E+00  | 0.00E+00  |

| Range 2: (10 <sup>-04</sup> , 10 <sup>-03</sup> ) & (10 <sup>+03</sup> , 10 <sup>+04</sup> ) | 2.67E-19 | 0.00E+00 | 0.00E+00  | 0.00E+00  |

| Range 3: (10 <sup>-13</sup> , 10 <sup>-12</sup> ) & (10 <sup>+12</sup> , 10 <sup>+13</sup> ) | 3.18E-18 | 1.06E-18 | 0.00E+00  | 0.00E+00  |

| Range 4: (10 <sup>-19</sup> , 10 <sup>-18</sup> ) & (10 <sup>+18</sup> , 10 <sup>+19</sup> ) | 5.98E+01 | 5.98E+01 | 3.77E-18  | 0.00E+00  |

| Range 5: (10 <sup>-37</sup> , 10 <sup>-36</sup> ) & (10 <sup>+36</sup> , 10 <sup>+37</sup> ) | 0.00E+00 | 0.00E+00 | 2.89E-18  | 0.00E+00  |

| Array Size = 1,048,576 elements                                                              |          |          |           |           |

| Sequential (CPU)                                                                             |          |          |           |           |

| Format:                                                                                      | mpf t 64 | mpf t 32 | mpf t 128 | mpf t 256 |

| Range 1: (10 <sup>-01</sup> , 10 <sup>+00</sup> ) & (10 <sup>+00</sup> , 10 <sup>+01</sup> ) | 0.00E+00 | 0.00E+00 | 0.00E+00  | 0.00E+00  |

| Range 2: (10 <sup>-04</sup> , 10 <sup>-03</sup> ) & (10 <sup>+03</sup> , 10 <sup>+04</sup> ) | 1.58E-16 | 0.00E+00 | 0.00E+00  | 0.00E+00  |

| Range 3: $(10^{-13}, 10^{-12}) & (10^{+12}, 10^{+13})$                                       | 2.62E-15 | 6.77E-16 | 0.00E+00  | 0.00E+00  |

| Range 4: (10 <sup>-19</sup> , 10 <sup>-18</sup> ) & (10 <sup>+18</sup> , 10 <sup>+19</sup> ) | 3.85E+04 | 3.85E+04 | 2.61E-15  | 0.00E+00  |

| Range 5: (10 <sup>-37</sup> , 10 <sup>-36</sup> ) & (10 <sup>+36</sup> , 10 <sup>+37</sup> ) | 0.00E+00 | 0.00E+00 | 7.95E+01  | 1.48E-34  |

| Parallel (GPU)                                                                               |          |          |           |           |

| Format:                                                                                      | cump 64  | cump 32  | cump 128  | cump 256  |

| Range 1: (10 <sup>-01</sup> , 10 <sup>+00</sup> ) & (10 <sup>+00</sup> , 10 <sup>+01</sup> ) | 0.00E+00 | 0.00E+00 | 0.00E+00  | 0.00E+00  |

| Range 2: (10 <sup>-04</sup> , 10 <sup>-03</sup> ) & (10 <sup>+03</sup> , 10 <sup>+04</sup> ) | 3.53E-17 | 0.00E+00 | 0.00E+00  | 0.00E+00  |

| Range 3: (10 <sup>-13</sup> , 10 <sup>-12</sup> ) & (10 <sup>+12</sup> , 10 <sup>+13</sup> ) | 5.61E-16 | 1.45E-16 | 0.00E+00  | 0.00E+00  |

| Range 4: (10 <sup>-19</sup> , 10 <sup>-18</sup> ) & (10 <sup>+18</sup> , 10 <sup>+19</sup> ) | 8.20E+03 | 8.20E+03 | 5.64E-16  | 0.00E+00  |

| Range 5: (10 <sup>-37</sup> , 10 <sup>-36</sup> ) & (10 <sup>+36</sup> , 10 <sup>+37</sup> ) | 0.00E+00 | 0.00E+00 | 6.94E+01  | 3.89E-35  |

From Table 7 we can observe that, on the 1024-element array in *Range 1*, the program gives accurate results in all cases. The global summation program starts to provide

inaccurate results when the input sequence is created in *Range 2*. While the *32-bit* and *64-bit GMP* precisions have the same number of *limbs* (2 *limbs*), we find that *64-bit* results are less accurate than *32-bit* results. This is explained as follow: in our program, we generate *32-bit GMP* arrays from *float* arrays, and *64-bit GMP* arrays from *double* arrays. A single precision number has fewer significant digits after the radix point than a double number; for example: compare 1.12340808090000000 *float* with 1.123408080808700800788652001 *double*. The non-zero digits after the radix point in the *64-bit GMP* array contribute to the inaccuracy of the result.

Next, we progressively increase the (positive and negative) order of magnitude of the intervals. Our data show that 32-bit GMP precision leads to inaccurate results when the input sequence is in Range 3, and 128-bit GMP precision causes error when the input sequence is in Range 4.

In the case of 1024-element arrays, when increasing the gap between the intervals from minimum value of *float* to maximum value of *float*, *256-bit GMP* precision still produces the correct sum. Therefore, to illustrate the inaccuracy problem when using *256-bit GMP*, we have to use larger inputs. For example, *256-bit GMP* produces inaccuracy when the array size is 1,048,576 elements (10<sup>20</sup> elements), and the values of elements are in *Range* 5.

All of the above results demonstrate that we can use GMP and CUMP libraries with appropriate precision bits to increase accuracy for applications involving floating-point numbers. However, we do not choose to use these libraries for all applications because of the trade-off between accuracy and performance. To learn more about this issue, we monitor the execution time of the program and report the results in Table 8.

Table 8: Execution time of GMP and CUMP vs. double precision.

| Array size = | 1024      |           |           |           |          |        |              |               |         |

|--------------|-----------|-----------|-----------|-----------|----------|--------|--------------|---------------|---------|

| Sequential ( | (CPU)     |           |           |           |          |        |              |               |         |

|              | mm f22    | mpf64     | mpf128    | mm £256   | double   | Exe    | ecution time | e of gmp / do | ouble   |

|              | mpf32     | mp164     | 111p1128  | mpf256    | double   | 32 bit | 64 bit       | 128 bit       | 256 bit |

|              | 0.0562    | 0.0563    | 0.0583    | 0.0623    | 0.0049   | 11.4   | 11.4         | 11.8          | 12.7    |

| Parallel (G  | PU)       |           |           |           |          |        |              |               |         |

| # of         | cump32    | cump64    | cump128   | cump256   | double   | Exe    | cution time  | of cump / d   | ouble   |

| threads      | cump32    | cump64    | cump128   | cump236   | double   | 32 bit | 64 bit       | 128 bit       | 256 bit |

| 1            | 4.7144    | 4.7408    | 5.3914    | 5.7841    | 0.1499   | 31.5   | 31.6         | 36.0          | 38.6    |

| 32           | 0.7185    | 0.7357    | 0.8867    | 0.9298    | 0.0740   | 9.7    | 9.9          | 12.0          | 12.6    |

| 512          | 0.0183    | 0.0305    | 0.0211    | 0.0226    | 0.0410   | 0.4    | 0.7          | 0.5           | 0.6     |

| Array size = | = 1048576 |           |           |           |          |        |              |               |         |

| Sequential ( | CPU)      |           |           |           |          |        |              |               |         |

|              | mpft32    | mpft64    | mpft128   | mpft256   | double   | Exe    | ecution time | e of gmp / do | ouble   |

|              | mpit32    | 111p1t04  | mp1t128   | mp1t236   | double   | 32 bit | 64 bit       | 128 bit       | 256 bit |

|              | 69.3969   | 69.8896   | 69.1415   | 70.2967   | 3.9748   | 17.5   | 17.6         | 17.4          | 17.7    |

| Parallel (G  | PU)       |           |           |           |          |        |              |               |         |

| # of         | cump32    | cump64    | cump128   | 256       | double   | Exe    | cution time  | of cump / d   | ouble   |

| threads      | cump32    | cump64    | cump128   | cump256   | double   | 32 bit | 64 bit       | 128 bit       | 256 bit |

| 1            | 4925.7116 | 4947.8438 | 5522.3788 | 6067.5971 | 130.1221 | 37.9   | 38.0         | 42.4          | 46.6    |

| 32           | 912.3816  | 915.9377  | 1054.0357 | 1150.5203 | 58.8911  | 15.5   | 15.6         | 17.9          | 19.5    |

| 512          | 99.7857   | 100.5909  | 117.0254  | 130.4637  | 7.4749   | 13.3   | 13.5         | 15.7          | 17.5    |

Table 8 shows that, for sequential summation, the performance of *GMP* is lower than that of *double* precision arithmetic by a factor *12-18x*. It also shows that, for parallel summation, the performance of *CUMP* is lower than that of double precision arithmetic by a factor *47x*. This proves that the use of *GMP* and *CUMP* is suitable only when an application really needs very high accuracy, and significant execution time degradations are not an important issue.

In addition, during the study of the *CUMP* library, we observed that *CUMP* kernels use many registers (Table 9). The maximum number of registers per block is 65,536 on the Kepler K40C GPU and 32,768 on the Fermi C2075 GPU used in this study. The register requirement limits the size of the thread-block that can be configured for the summation kernel to  $65,536/71 \sim 923$  for Kepler K40C and  $32,768/63 \sim 520$  for Fermi C2075.

Table 9: Number of registers using by kernels

|       | CUMP Kernel | Float2 Kernel | Double2 Kernel | Float kernel | Double kernel |

|-------|-------------|---------------|----------------|--------------|---------------|

| Sm_20 | 63          | 14            | 21             | 9            | 12            |

| Sm-35 | 71          | 15            | 28             | 10           | 12            |

Since the considered global summation kernel uses only a single thread-block, this block-size limitation does not allow fully utilizing the GPU hardware, leading to performance limitations. To solve this problem, we modify the global summation program to allow a multi-block kernel configuration. As shown in Table 10, the multi-block program can improve our performance by hiding latency, and we can get the best performance at grid-size = 64 and block-size = 32.

Table 10: Execution time (in seconds) of global summation using CUMP with various kernel configurations. Array size = 1,048,576. Device = Tesla C2075

| # of blocks | # of threads/block | cump 32   | cump 64   | cump 128  | cump 256  |

|-------------|--------------------|-----------|-----------|-----------|-----------|

| 1           | 1                  | 5583.4224 | 5571.0618 | 5898.5952 | 5900.0278 |

| 1           | 32                 | 1093.5682 | 1000.4324 | 1316.6489 | 1315.535  |

| 1           | 512                | 115.7171  | 112.3185  | 131.2939  | 131.3426  |

| 32          | 64                 | 24.0186   | 22.9559   | 28.7283   | 28.7056   |

| 64          | 32                 | 23.5261   | 22.6891   | 28.1209   | 28.0694   |

| 128         | 16                 | 32.6578   | 30.9646   | 38.4514   | 38.3379   |

| 256         | 8                  | 34.9698   | 33.3845   | 41.5386   | 41.2134   |

| 512         | 4                  | 37.9684   | 36.5593   | 43.0963   | 43.0193   |

# 5.2 Global summation with single/double floating point and composite precision numbers

In this section, we aim to evaluate global summation on GPU with floating-point representations that use lower number of precision bits than multiple-precision arithmetic, namely *float*, *double*, *float2*, and *double2*. As done for multiple-precision arithmetic, we study the effect of the arithmetic precision on accuracy and performance.

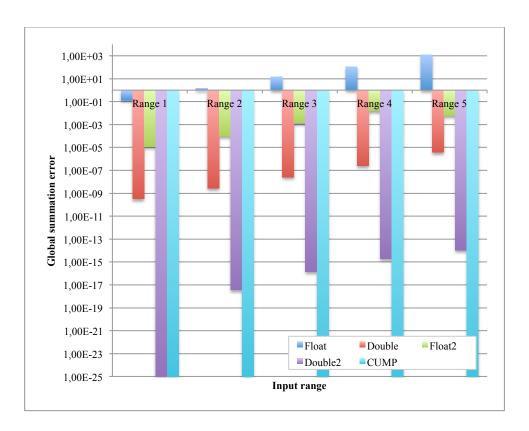

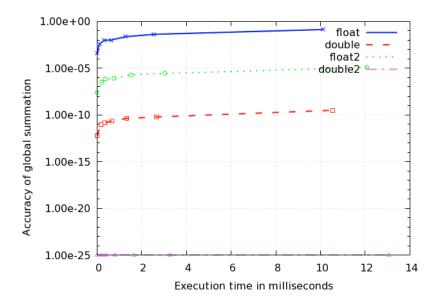

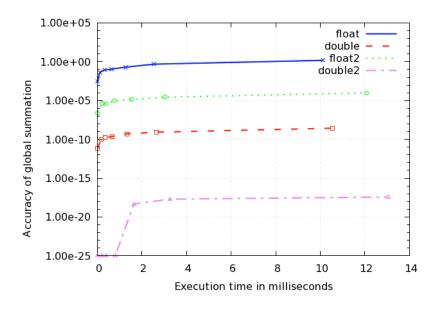

First, we observe the change in accuracy on 8M-element arrays when varying the absolute order of magnitude of the input intervals (Table 11). We recall that the expected result of the global summation is zero. However, all precisions but *256-bit CUMP* produce non-zero results. The results of the summation correspond to the cumulative error of the program, and these errors become larger when increasing the range of intervals. We can arrange precisions in ascending order of accuracy as follows: *float* (average error:  $10^{+01}$ ), *float2* (average error:  $10^{-03}$ ), *double* (average error:  $10^{-08}$ ), *double2* (average error:  $10^{-16}$ ), and *256-bit CUMP* (average error: 0).

Table 11: Accuracy of global summation using various precisions and five input ranges.

| Interval range                                                                           | Float    | Double   | Float2   | Double2  | 256 bit<br>CUMP |

|------------------------------------------------------------------------------------------|----------|----------|----------|----------|-----------------|

| Range 1: $(10^{-2}, 10^{-1}) & (10^{+1}, 10^{+2})$                                       | 1.38E-01 | 3.18E-10 | 1.17E-05 | 0.00E+00 | 0.00E+00        |

| Range 2: (10 <sup>-3</sup> , 10 <sup>-2</sup> ) & (10 <sup>+2</sup> , 10 <sup>+3</sup> ) | 1.51E+00 | 2.75E-09 | 9.84E-05 | 3.78E-18 | 0.00E+00        |

| Range 3: (10 <sup>-4</sup> , 10 <sup>-3</sup> ) & (10 <sup>+3</sup> , 10 <sup>+4</sup> ) | 1.43E+01 | 2.57E-08 | 1.38E-03 | 1.44E-16 | 0.00E+00        |

| Range 4: (10 <sup>-5</sup> , 10 <sup>-4</sup> ) & (10 <sup>+4</sup> , 10 <sup>+5</sup> ) | 1.10E+02 | 2.51E-07 | 1.53E-02 | 2.01E-15 | 0.00E+00        |

| Range 5: (10 <sup>-6</sup> , 10 <sup>-5</sup> ) & (10 <sup>+5</sup> , 10 <sup>+6</sup> ) | 1.21E+03 | 3.64E-06 | 6.06E-03 | 1.08E-14 | 0.00E+00        |

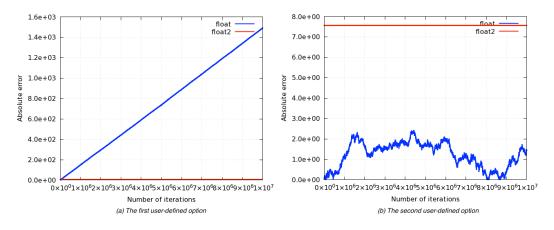

Figure 5 provides a graphical illustration of the error in logarithmic scale. In this and the other figures in this thesis, for the purpose of drawing the chart in logarithmic scale, the accurate sum (zero) is represented by  $10^{-25}$  rather than by  $10^{-\infty}$ . Each group of bars in Figure 5 represents the errors generated using the five considered arithmetic precisions in the same range of intervals. From the left to the right of Figure 5, the gap between the small and large input intervals increases. As can be seen, the accuracy of the results increases moving from *float*, to *float2*, to *double*, to *double2*, to *CUMP*. In addition, a large gap between the input intervals leads to worse accuracy for all precisions but *CUMP*, which always provides accurate results.

Figure 5: Accuracy of global summation

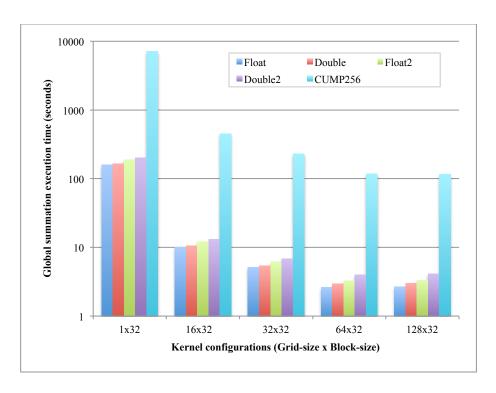

In order to evaluate performance, we start with the *one-block* kernel and increase the number of threads so as to determine the optimal *block-size*. Then, we fix the *block-size*, and increase the number of blocks (*grid-size*) so as to fully populate our GPUs. Table 12 shows the execution times reported on an 8M-element array (the order of magnitude of the elements in the array is irrelevant to performance). As can be seen, a *block-size* of 32 (equal to the *warp-size*) is in all cases optimal for performance. In addition, increasing the number of blocks up to 64 leads to performance improvements. However, since 64 blocks allow good GPU utilization and memory latency hiding, no performance improvements are observed when further increasing the number of blocks.

Table 12: Execution time of 8M-array global summation using various precisions and different kernel configuration, intervals:  $(10^{-6}, 10^{-5})$  &  $(10^{+5}, 10^{+6})$ , device = Tesla C2070.

| # of blocks | # of<br>threads<br>/block | float     | double   | float2    | double2   | (D-F)/F | (F2-F)/F | (D2-F)/F |

|-------------|---------------------------|-----------|----------|-----------|-----------|---------|----------|----------|

| 1           | 1                         | 1518.6588 | 1721.518 | 2479.5372 | 2946.7413 | 0.13    | 0.63     | 0.94     |

| 1           | 32                        | 160.0303  | 165.8942 | 189.0708  | 200.9911  | 0.04    | 0.18     | 0.26     |