# GUI FOR DEBUGGING AND DEVELOPMENT OF RECONFIGURABLE, EVOLVING SYSTEMS ENABLED BY EMBEDDED HARDWARE BLOCKS

-\_\_\_\_

A Thesis

presented to

the Faculty of the Graduate School

at the University of Missouri

\_\_\_\_\_

In Partial Fulfillment

of the Requirements for the Degree

Master of Science

by

KITTISAK SAJJAPONGSE

Dr. Tina Smilkstein, Advisor

MAY 2010

The undersigned, appointed by the Dean of the Graduate School, have examined the thesis entitled

# GUI FOR DEBUGGING AND DEVELOPMENT OF RECONFIGURABLE, EVOLVING SYSTEMS ENABLED BY EMBEDDED HARDWARE BLOCKS

| presented by                        | Kittisak Sajjapongse                              |

|-------------------------------------|---------------------------------------------------|

| a candidate for the degree of       |                                                   |

|                                     | Master of Science                                 |

| and hereby certify that in their op | inion it is worthy of acceptance.                 |

|                                     |                                                   |

|                                     |                                                   |

| Dr. Tina Smilkstein, Assistant      | Professor, Department of Electrical and Computer  |

| Engineering                         |                                                   |

|                                     |                                                   |

| Dr. James M. Keller, Professor, D   | Department of Electrical and Computer Engineering |

|                                     |                                                   |

| Dr. Yunxin Zhao, Professor, Depa    | artment of Computer Science                       |

# **ACKNOWLEDGEMENTS**

I would like to thank Dr. Tina Smilkstein for her assistance and guidance through out my research. I would also like to thank Dr. James Keller and Dr. Yunxin Zhao for therir valuable suggestions and for serving on my committee.

I wish to thank my research mates, Kiran Kumar Tati and Parashar Barve, for their comments, help preparing this paper and friendship.

I would especially thank to my parents, Dr. Adisak Sajjapongse and Tommarat Sajjapongse, and my elder sisters, Nok Jurairat Sajjapongse and Mam Naovarat Sajjapongse, for their love, care and support.

I am in deep gratitude and admiration to Parn Sasiwimon Yoo-eam who has always kept me optimistic and stayed beside me all the time.

I take this opportunity to thank my friends, Rocky Surachat Pumipuntu, Frank Surachai Pumipuntu, Prite Chaowalit Thamsonglar, Ju Kanchana Songkittiphong and all my friends who stood by my side for their suggestions and friendship.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                          | ii   |

|-------------------------------------------|------|

| LIST OF TABLES                            | viii |

| LIST OF FIGURES                           | x    |

| ABSTRACT                                  | xiv  |

| CHAPTER                                   |      |

| 1. INTRODUCTION                           | 1    |

| 1.1. Introduction                         | 1    |

| 1.2. Review of Evolutionary Computation   | 3    |

| 1.2.1. Chromosome and Gene Representation | 4    |

| 1.2.2. Reproduction                       | 6    |

| 1.2.2.1. Crossover                        | 6    |

| 1.2.2.2. Mutation                         | 7    |

| 1.2.3. Selection                          | 8    |

| 1.2.4. Evaluation                         | 10   |

| 1.2.5. Termination Criteria               | 10   |

| 1.2.6. The General flow for algorithm     | 12   |

| 1.3. Evolutionary Computation on Hardware | 13   |

| 1.3.1. Implementation Problems            | 13   |

| 1.3.2. Debugging Problems                 | 16   |

| 1 3 3 Hardwara Platforms                  | 17   |

|    | 1.4. Repor  | rt organization                              | 22 |

|----|-------------|----------------------------------------------|----|

| 2. | REVIEW      | OF THE EVOLUTIONARY HARDWARE TESTBED (GPEAT) | 23 |

|    | 2.1. Introd | luction                                      | 23 |

|    | 2.2. GPE    | AT User Interface and Parameters mapping     | 25 |

|    | 2.3. Struct | tures for the hardware framework             | 27 |

|    | 2.3.1.      | Initial Population Generation blocks         | 28 |

|    | 2.3.2.      | Crossover and Mutation Control blocks        | 29 |

|    | 2.3.3.      | Central Control blocks                       | 30 |

|    | 2.3.4.      | Output Control blocks                        | 31 |

|    | 2.3.5.      | Fitness Function blocks                      | 32 |

|    | 2.3.6.      | Sensors blocks                               | 33 |

|    | 2.4. Debug  | gging GPEAT system                           | 33 |

| 3. | GRAPHIC     | CAL USER INTERFACE DESIGN                    | 36 |

|    | 3.1. Paran  | neters Entry GUI                             | 36 |

|    | 3.1.1.      | Workspace                                    | 37 |

|    | 3.1         | 1.1.1. Creating/Loading/Saving Project       | 38 |

|    | 3.1         | 1.1.2. Creating/Loading/Saving Source        | 38 |

|    | 3.1.2.      | System                                       | 38 |

|    | 3.1.3.      | Input (Sensors)                              | 42 |

|    | 3.1.4.      | Default Output                               | 43 |

|    | 3.1.5.      | Initial Population                           | 44 |

|    | 3.1.6.      | Fitness Rules                                | 47 |

|    | 3.1.7.      | Debugger                                     | 49 |

|    | 3.1.8.      | Generating GPEAT core                                |

|----|-------------|------------------------------------------------------|

|    | 3.2.Binary  | Data File Encoder (.dat Encoder)                     |

| 4. | DEBUGG      | ING HARDWARE FOR EVOLUTIONARY HARDWARE TESTBED       |

|    |             | 53                                                   |

|    | 4.1. Introd | uction                                               |

|    | 4.2.Essent  | ials for Debugging Interface54                       |

|    | 4.3. The R  | S-232 Connection                                     |

|    | 4.3.1.      | RS-232 Connector                                     |

|    | 4.3.2.      | RS-232 Protocol                                      |

|    | 4.3.3.      | USB-to-RS232 Converter                               |

|    | 4.4.Hardw   | rare Architecture 60                                 |

|    | 4.4.1.      | Overall Hardware Design                              |

|    | 4.4.2.      | The Debugger Controller (DC)                         |

|    | 4.4.3.      | Memory (RAM)                                         |

|    | 4.4.4.      | The TX Controller (TXC)                              |

|    | 4.4.5.      | The TX Interface (TXI)                               |

|    | 4.4.6.      | The RX Controller (RXC)                              |

|    | 4.4.7.      | The RX Interface (RXI)81                             |

|    | 4.5.Interac | etion between Debugging Hardware and Debugging GUI84 |

|    | 4.5.1.      | Identification Package                               |

|    | 4.5.2.      | GPEAT System Information Package                     |

|    | 4.5.3.      | Chromosome Package                                   |

| 5. | DEBUGG      | ING GRAPHICAL USER INTERFACE                         |

|    | 5.1. Introd | luction                               | 88  |

|----|-------------|---------------------------------------|-----|

|    | 5.2. Debug  | gging Graphical User Interface (DGUI) | 88  |

|    | 5.2.1.      | Workspace                             | 88  |

|    | 5.2         | 2.1.1. Loading debugging data         | 89  |

|    | 5.2         | 2.1.2. Saving debugging data          | 90  |

|    | 5.2.2.      | Working with GPEAT hardware           | 90  |

|    | 5.2         | 2.2.1. Connecting to GPEAT hardware   | 90  |

|    | 5.2         | 2.2.2. Obtaining data from hardware   | 92  |

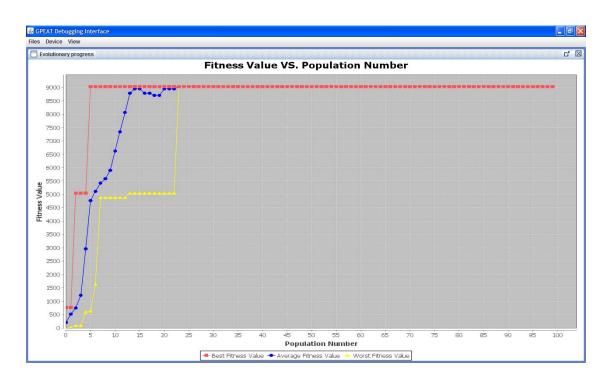

|    | 5.2.3.      | Evolutionary Progress Graph           | 94  |

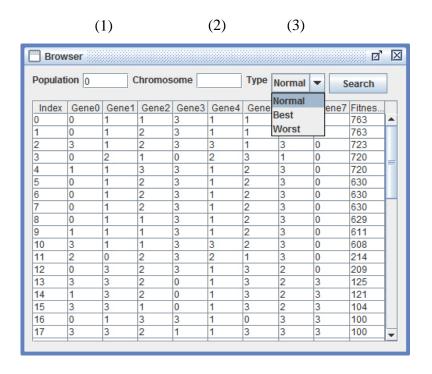

|    | 5.2.4.      | Browser                               | 95  |

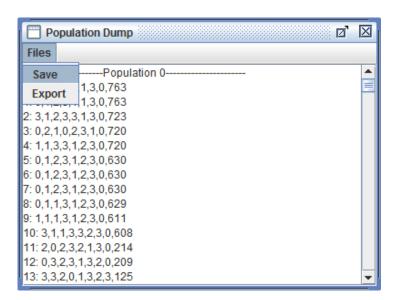

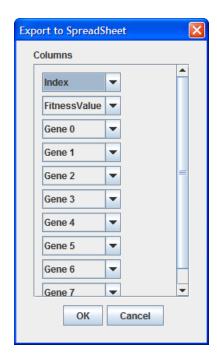

|    | 5.2.5.      | Population Dump                       | 97  |

| 6. | SIMULA      | ΓΙΟΝ AND DATA                         | 99  |

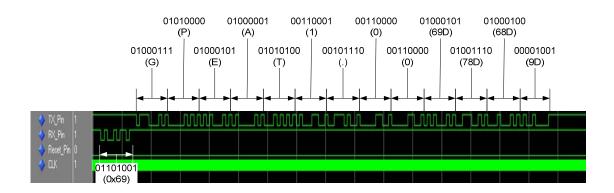

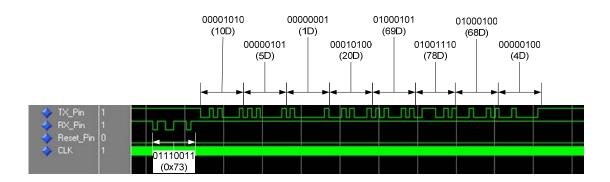

|    | 6.1. Hardy  | ware simulation                       | 99  |

|    | 6.1.1.      | The Debugger Controller               | 99  |

|    | 6.1.2.      | The TX Controller (TXC)               | 103 |

|    | 6.1.3.      | The TX Interface (TXI)                | 106 |

|    | 6.1.4.      | The RX Controller (RXC)               | 107 |

|    | 6.1.5.      | The RX Interface (RXI)                | 109 |

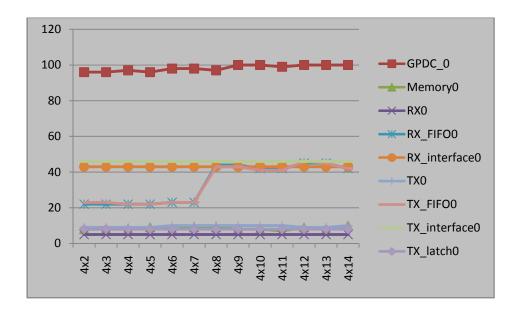

|    | 6.2.Hardw   | are usage                             | 111 |

| 7. | CONCLU      | SION AND FUTURE WORK                  | 118 |

|    | 7.1.Conclu  | usion                                 | 118 |

|    | 7.2.Future  | work                                  | 119 |

| 8  | REFEREN     | NCF                                   | 123 |

| 9.  | APPENDIX    | 126          |

|-----|-------------|--------------|

|     |             |              |

| 10. | SOURCE CODE | Media Folder |

# LIST OF TABLES

| Table | Pag                                           | zе |

|-------|-----------------------------------------------|----|

| 1.1   | SPLD Characteristic1                          | 8  |

| 1.2   | CPLD Characteristic                           | 9  |

| 1.3   | FPGA Characteristic                           | 9  |

| 1.4   | Design analysis table2                        | .1 |

| 3.1   | System Parameter descriptions                 | 0  |

| 3.2   | System Parameters                             | -1 |

| 3.3   | Input parameters description                  | -2 |

| 3.4   | Parameters for sensor                         | .3 |

| 4.1   | Signal-Pin mapping in RS-232 connection       | 6  |

| 4.2   | Parameters for RS-232 protocol                | 8  |

| 4.3   | Command recognized by the DC6                 | 6  |

| 4.4   | Parameters for RS-232 protocol in TXI         | 6  |

| 4.5   | Parameters for RS-232 protocol in RXI         | 1  |

| 4.6   | Commands recognized by Debugging Hardware     | 5  |

| 6.1   | Simulation Setup for Debugger Controller (DC) | 0  |

| 6.2        | Simulation Setup for TX Controller (TXC) | . 104 |

|------------|------------------------------------------|-------|

| 6.3        | Simulation Setup for TX Interface (TXI)  | 106   |

| 6.4        | Simulation Setup for RX Controller (RXC) | 108   |

| 6.5        | Simulation Setup for RX Interface (RXI)  | 109   |

| 6.6        | Basic Macros recognized                  | 112   |

| <b>6.7</b> | Design summary for debugging hardware    | .116  |

# LIST OF FIGURES

| Fig | ures                                                      | Page |

|-----|-----------------------------------------------------------|------|

| 1.1 | An example of Search space                                | 4    |

| 1.2 | An example of Search space                                | 5    |

| 1.3 | A Roulette-wheel selection                                | 9    |

| 1.4 | The general flow for EC                                   | 12   |

| 2.1 | Simplified EC hardware flow                               | 24   |

| 2.2 | GPEAT configuration flow                                  | 26   |

| 2.3 | Hardware Block Diagram                                    | 28   |

| 2.4 | Debugging connection diagram                              | 35   |

| 3.1 | Workspace                                                 | 37   |

| 3.2 | System parameters window                                  | 39   |

| 3.3 | Default output examples for two types of gene             | 44   |

| 3.4 | An example of initial population for binary type of gene  | 45   |

| 3.5 | An example of initial population for integer type of gene | 46   |

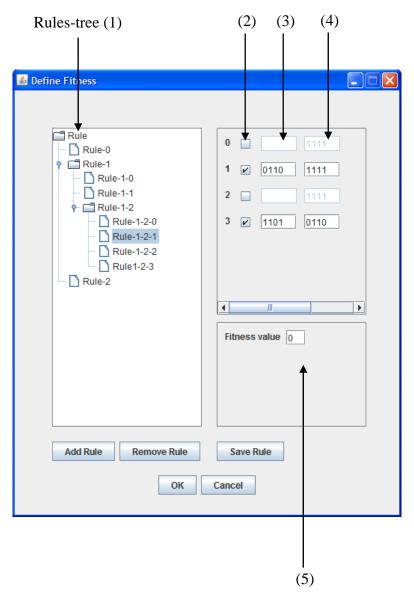

| 3.6 | The Fitness Rules window                                  | 47   |

| 3.7 | The window for specifying name for a rule                 | 49   |

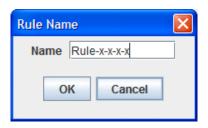

| 3.8  | Debugger window                                             | 50 |

|------|-------------------------------------------------------------|----|

| 3.9  | Workspace containing VHDL codes generated                   | 51 |

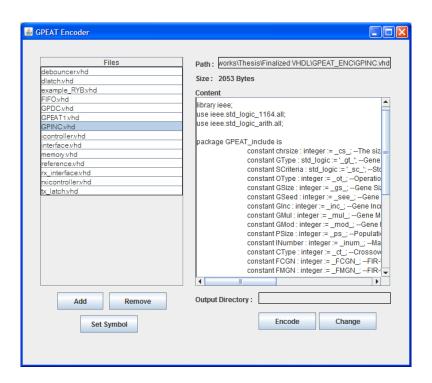

| 3.10 | GPEAT binary file encoder                                   | 52 |

| 4.1  | Communication topology                                      | 55 |

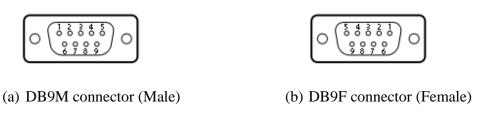

| 4.2  | Front view of DB9 connector                                 | 56 |

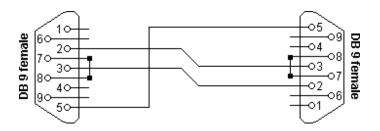

| 4.3  | Null-Modem cable wiring                                     | 57 |

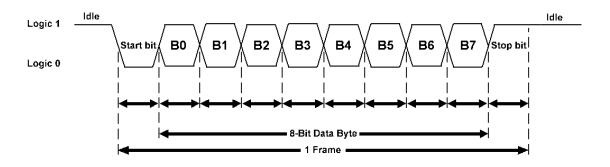

| 4.4  | Timing diagram for a frame transferred in RS-232 connection | 58 |

| 4.5  | A USB-to-RS232 converter                                    | 59 |

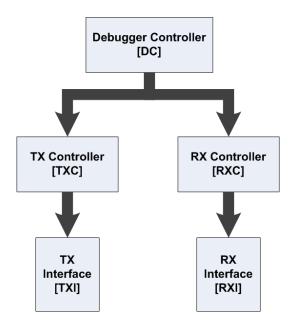

| 4.6  | Hierarchical diagram for modules                            | 61 |

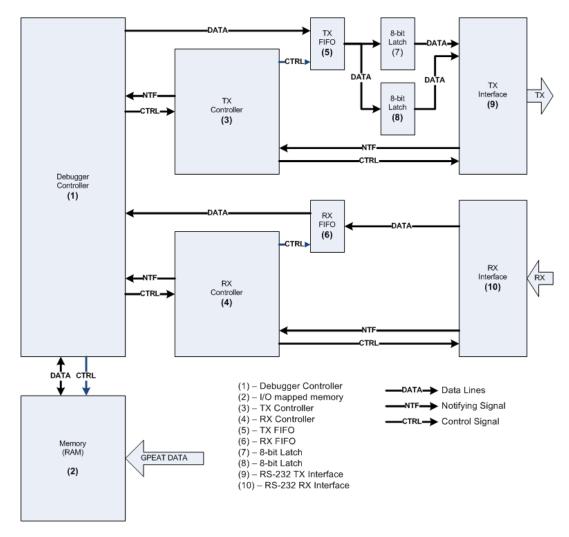

| 4.7  | Overall architecture for debugging hardware                 | 62 |

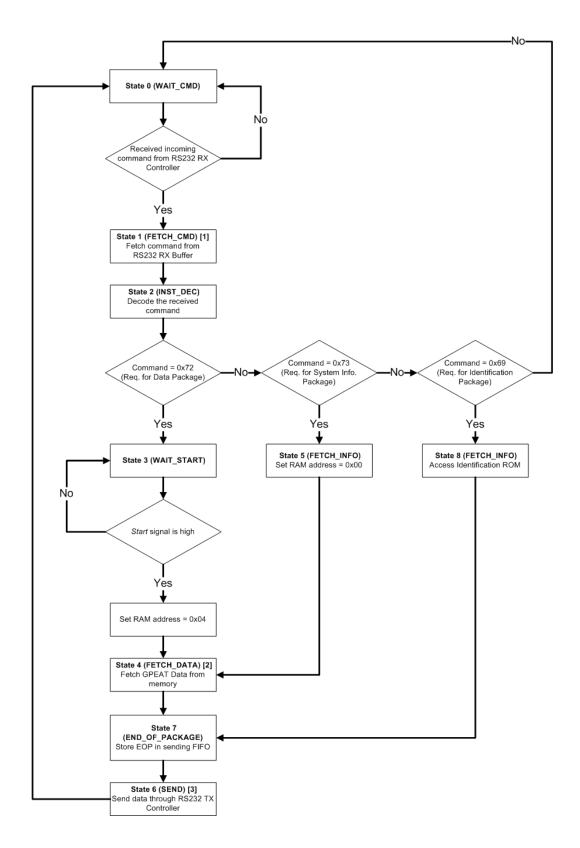

| 4.8  | The ASM chart for the DC unit                               | 65 |

| 4.9  | Data mapped in the RAM module                               | 68 |

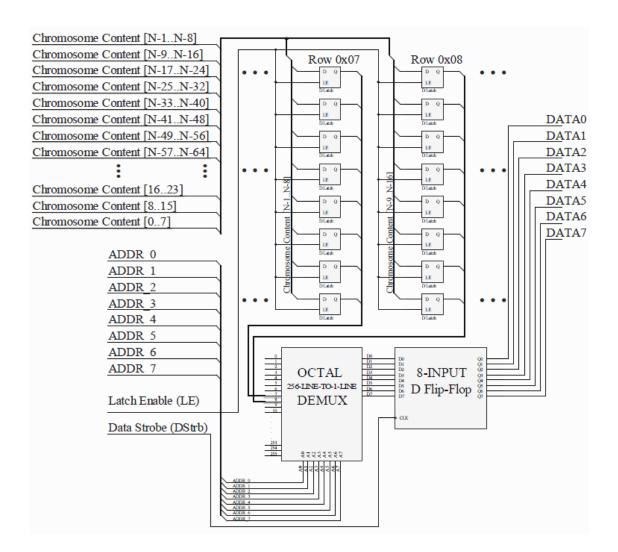

| 4.10 | RAM architecture for the DC                                 | 69 |

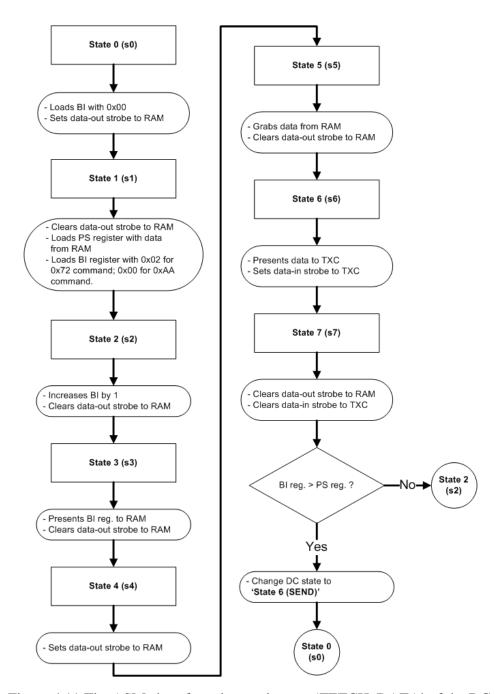

| 4.11 | The ASM chart for sub-state in state 'FETCH_DATA' of the DC | 72 |

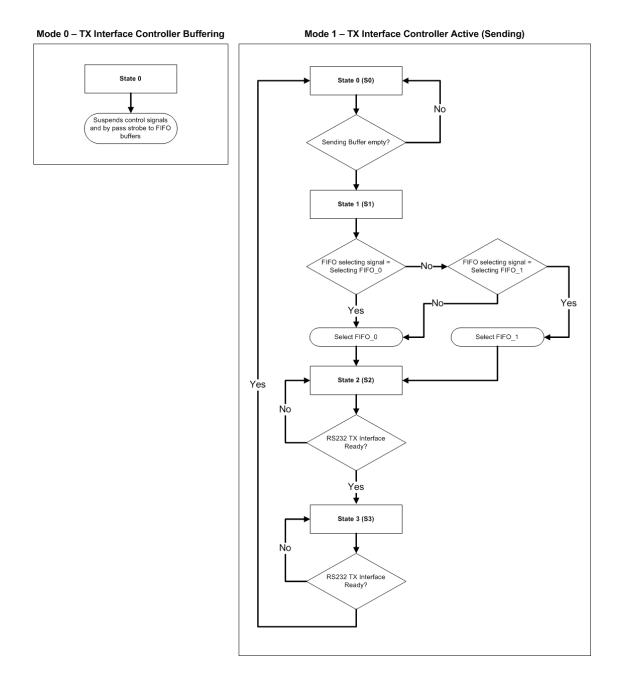

| 4.12 | The ASM charts for TXC in mode-0 and mode-1                 | 74 |

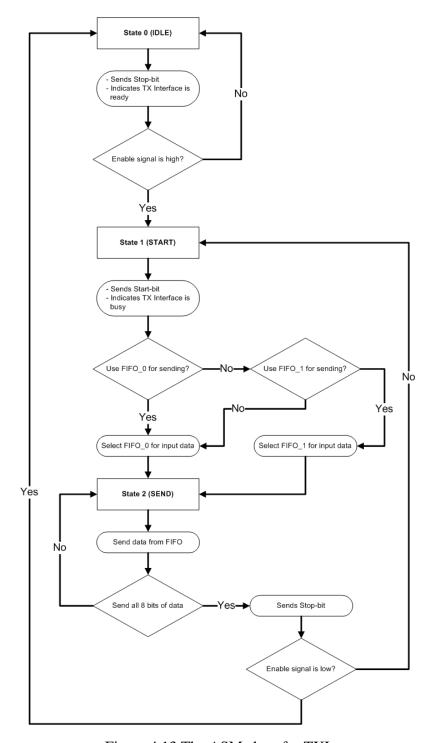

| 4.13 | The ASM chart for TXI                                       | 78 |

| 4.14 | The ASM charts for RXC                                      | 80 |

| 4.15 | The ASM charts for BRG (left) and RXI (right)   | 83  |

|------|-------------------------------------------------|-----|

| 4.16 | Structure of EOP                                | 85  |

| 4.17 | Identification Package                          | 86  |

| 4.18 | GPEAT System Information Package                | 87  |

| 5.1  | DGUI workspace                                  | 89  |

| 5.2  | RS-232 Setup                                    | 91  |

| 5.3  | A dialog showing hardware signature and version | 92  |

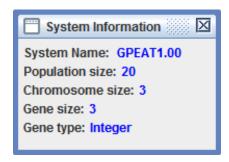

| 5.4  | A window showing GPEAT parameters               | 92  |

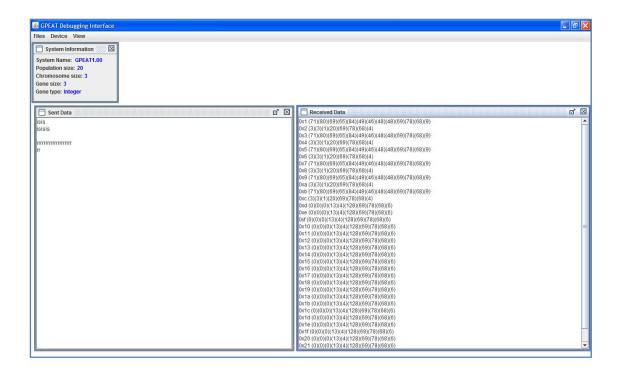

| 5.5  | Interfacing windows in a workspace              | 94  |

| 5.6  | Evolutionary Progress Graph                     | 95  |

| 5.7  | A Browser window                                | 96  |

| 5.8  | Population Dump window                          | 97  |

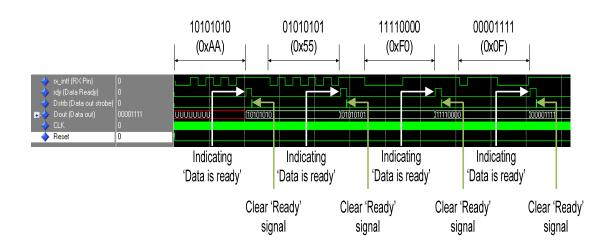

| 5.9  | Export to SpreadSheet dialog                    | 98  |

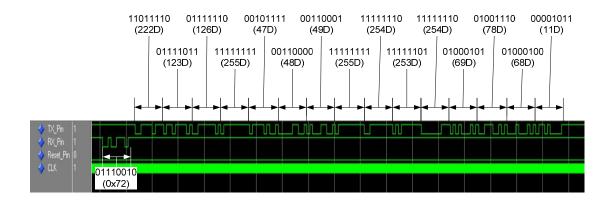

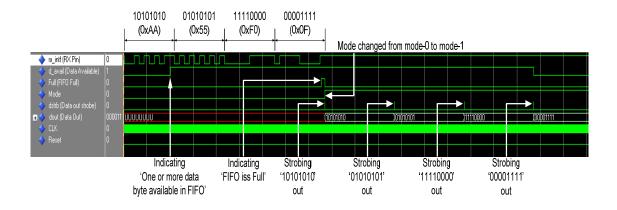

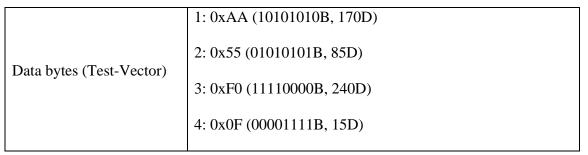

| 6.1  | Timing diagram for response of 0x69 command     | 102 |

| 6.2  | Timing diagram for response of 0x73 command     | 102 |

| 6.3  | Timing diagram for response of 0x72 command     | 103 |

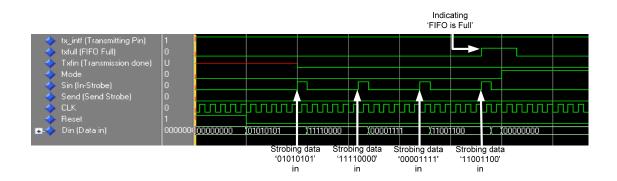

| 6.4  | Timing diagram for TXC mode-0                   | 105 |

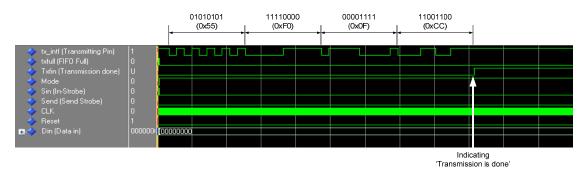

| 6.5 | Timing diagram for TXC mode-1                          | 105 |

|-----|--------------------------------------------------------|-----|

| 6.6 | Timing diagram for TXI                                 | 107 |

| 6.7 | Timing diagram for RXC                                 | 108 |

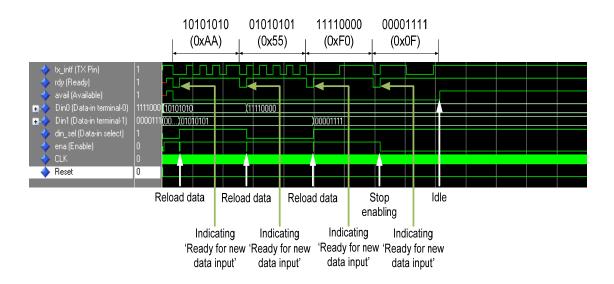

| 6.8 | Timing diagram for RXI                                 | 110 |

| 6.9 | FPGA slices used for debugging hardware implementation | 115 |

# GENERAL PURPOSE EVOLUTIONARY ALGORITHM TESTBED

Kittisak Sajjapongse

Dr. Tina Smilkstein, Advisor

## **ABSTRACT**

A flexible hardware testbed for Evolutionary Computation is developed in our research. The purpose is to realize a system with an ability to implement a wide variety of Evolutionary Computation applications. In this literature, General Purpose Evolutionary Algorithm Testbed (GPEAT) is described. GPEAT provides a flexible substrate for Evolutionary Computation applications on hardware platform using reconfigurable device such as FPGA. GPEAT consists of GPEAT core, debugging hardware, configuring GUI (Parameter-entry GUI) and debugging GUI. Parameter-entry GUI enables users to construct an Evolutionary Computation system on hardware with minimal knowledge on hardware designing. The GPEAT core obtains system parameters through the GUI and operates accordingly as users specify to find appropriate solutions from search space. Debugging interface is also provided through debugging hardware and debugging GUI to assist users in evaluating implemented system.

GPEAT provides users friendly environment to instantiate and debug Evolutionary Computation application on hardware. VHDL code is generated according to the system description parameters by the GUI. The design, then, be programmed into reconfigurable device. Xilinx ISE and ModelSim XE-III (MXE-III) simulator are used as tools for implementing the GPEAT system on Xilinx® Spartan 3E<sup>TM</sup> starter kit.

Chromosomes, fitness values and other information of the implemented system is pulled out from the device through debugging hardware, which is attached to the GPEAT core, and is visualized by debugging GUI. With this system we tried to decrease the barrier of evolutionary algorithm designers to implement their designs in hardware and allow for easier debugging, revision and research on evolutionary hardware systems.

# **CHAPTER 1**

# INTRODUCTION

#### 1.1 Introduction

Evolutionary Computation (EC) is a method for finding a set of appropriate solutions to optimization problems. It is a heuristic search process which imitates the process of gradual development found in natural habitats. Living organisms evolve through the interaction of competition, selection, reproduction and mutation processes. EC has been used to solve many kinds of real world problems. It provides efficient search and optimization tools for very large dataset and does not require mathematical modeling. The effectiveness of ECs include their high suitability for parallel computer implementation, particular success in large search and optimization problems and an their ability to learn complex relationships in incomplete datasets [1]. Mathematicians and computer scientists have been exploring the possibilities of ECs for many years [2-4].

Running ECs on software have a number of disadvantages over running them on hardware. These include slower execution speed when emulated by software on a conventional computer and the need to build a dedicated platform for mobile device or embedded system which may not be able to provide sufficient mobility or memory to execute programs that require a large dataset. Also, for mathematicians and computer

scientists, the idea of moving EC into hardware may be too much of a challenge due to the required need of hardware knowledge. Implementing an EC system on hardware seems to be painful since each building block in the system must be customized for one set of parameters in a particular optimization problem. Changing parameters could mean changing the hardware structure of a building block which requires many design considerations including debugging the hardware block, design time and how it interfaces with other blocks. Once the hardware is built, debugging and performance analysis tools are needed. Each time a new system is built a new way to debug and evaluate must also be developed. To enable mathematicians and scientists who need to yield the benefits of hardware parallelism, we have designed a reconfigurable EC testbed (General Purpose Evolutionary Algorithm Testbed, GPEAT) to provide an easy platform to design and debug hardware EC systems.

GPEAT is a hardware framework generalized for EC application. Common hardware structures for EC are used to enable efficient execution. Field-Programmable-Gate-Array (FPGA) is used as a substrate for these hardware structures. In the design of GPEAT, not only was design effort put into the development of hardware structures, much effort was also put into making the user interface specific to the development of EC systems. GPEAT can be reconfigured and debugged through Graphical-User-Interface (GUI) provided as a configuring and debugging tool. In this way we developed GPEAT which can be used to design and run a wide variety of EC application as well as allowing a person with minimal hardware knowledge to design EC systems in hardware.

## 1.2 Review of Evolutionary Computation

Evolutionary Computations are search techniques that are biologically inspired. The techniques search for qualified solutions, or *candidates*, in a search space for particular problems. The search space is an abstract surface which can have as many dimensions as required by the problem. EC search for a region or a point in the search space in which local-minima (-maxima) or global-minima (-maxima) is located. A set of candidates, namely a *population*, represents a specific region of the search space. *Fitness value* is introduced to evaluate and categorize candidates and used to represent attribute for a point in the search space. Fitness value can be calculated by a function which is defined by the problem to be solved or optimized. Each candidate can be represented in a bio-inspired form called *chromosome*; and each chromosome consists of a number of *genes*.

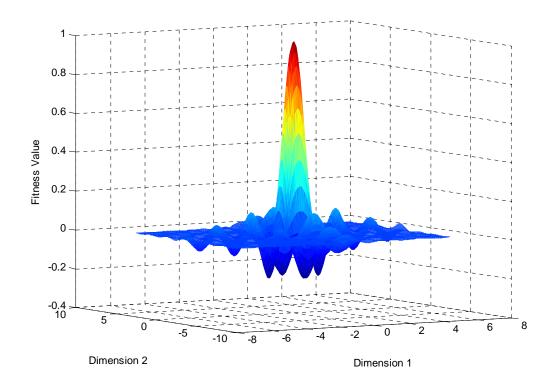

An example of search space is shown in Figure 1.1, the entire search space for 2-dimension (2-gene) problem is presented with many local-minima (-maxima) and one global-maxima. A population can represents any specific region of the surface; and if the population is large enough, it virtually represents the entire search space. If this is the case, the technique search for a peak point which can be any local-maxima or the global-maxima for optimizing the problem. The search space in Figure 2.1 can be depicted because it is generated from a deterministic sinc function. In real world application, search space might be unable to be depicted due to non-deterministic characteristic of the problem. A problem can have more than two dimensions which can make the

solutionspace harder to describe. Sometimes, we only know how to evaluate each individual candidate so it is impossible to construct the entire search space but, because a number of candidates representing the entire search space can be uncounted, the problem becomes tractable.

Figure 1.1 an example of Search space

## 1.2.1 Chromosome and Gene Representation

In a population, each candidate has some information encoded in it in some fashion. This information must be appropriate in order to solve or optimize a problem. A group of blocks containing numeric or symbolic data are combined to form a single candidate which can be interpreted as a single possible solution to a particular problem. This resembles to biological chromosome which contains sequences of genes. For this

reason, we call a single block containing data as a *gene* and a candidate a *chromosome* in EC. A Basic Structure for a chromosome is shown in Figure 1.2.

| Gene 1 | Gene 2 | Gene 3 | <br>Gene N |

|--------|--------|--------|------------|

|        |        |        |            |

Figure 1.2 Chromosome structure

The commonly used encoding or value of each block include binary strings, integer numbers, fixed-point numbers, floating-point numbers, graphs and hybrid values. This means each gene can contain a binary bit-string, a number, or some combination of symbols. Genes in a chromosome are considered as a unit and are evaluated as a solution as such. The quality or fitness of a chromosome as a solution to a problem is evaluated by looking at how, when the gene values are used as a group as the input values to a problem, how well the problem is solved. This evaluation of how good a solution a chromosome is can be donr by using a set of rules or by comparing performance from a test run in an actual environment or simulation. Chromosome evaluation will be described in section 1.1.4.

A popular example for EC will be used here to illustrate. Suppose that there is a salesman who wants to travel to all 50 states in the U.S. but also wants to minimize the cost of travelling given a starting state. A chromosome presented here contains 50 genes where a single gene is recognized as node or state being visited at a time and the order of genes represents the sequence of states to be visited. A symbol or a number representing the states can be filled into genes depends on how the chromosome will be evaluated. Rules or functions for evaluating each chromosome (solution) are defined accordingly to

the requirements and constrains of the problem. In this case, the requirement is minimizing the cost as much as possible. The conformity of a chromosome to the requirement can be evaluated by using rule set or a single function, multiple functions, attest in an actual environment or using the results of a simulator. The mechanism that used to determine the fitness of a chromosome as a solution is called a *Fitness function*.

## 1.2.2 Reproduction

Reproduction plays an important role for the search techniques because it produces off-springs (new chromosomes or solutions) from existing parents. Off-springs produced in each generation can have as more, less or same quality as a solution as their parents are. This can be visualized as moving from a specific region, represented by previous population, on search space to other specific location, represented by current population. This is one of the processes that move the algorithms toward convergence. Two commonly used genetic operators are *crossover* and *mutation*. These two operators have different role in producing off-springs and will be described in the following section (1.1.2.1 and 1.1.2.2). There are probabilities associated with the operators. These probabilities describe chances for these two operators to take place during evolution.

#### **1.2.2.1 Crossover**

Crossover is a genetic operator which uses two parents to produce one or more off-springs. Two parents are selected from a population to exchange their genes and form a complete, new off-spring. By exchanging the genes of parents to create off-spring, the off-springs inherit some properties of their parents. It is not necessarily true that selecting better parents will form better off-spring. It is an assumption that selecting better parents

might produce off-spring that inherit some preferred properties and exhibit more conformity to the requirement of the problem. Better parents mean having higher chromosome quality and the population tends to move ascending a peak region. According to the assumption, this would move the population toward the local or global-minima (-maxima) moving the search toward convergence. A problem occurs when some of chromosomes start moving toward local-minima (-maxima). The population may converge on this peak point which sometimes is unacceptable by the termination criteria defined by the problem.

#### **1.2.2.2 Mutation**

Mutation is another genetic operator which is commonly used. In this operation, one parent chromosome is selected to produce one or more off-spring. New off-spring is produced by applying some modification to one or more genes in the selected parent. This kind of reproduction would assist in exploring search space by introducing randomness and the ability to not get caught in a local-minima (-maxima). An example of a place that mutation might be potentially useful is when the search starts to converge towards a local-minima (-maxima) and almost all individuals have like content. Since the genes of each individual are alike, crossover might not move then away from the local-minima (-maxima) by randomly altering one gene of a selected individual it might help get the search out of that specific region and jump to others which might be better or worse. In this way, increases the probability not getting stuck in a local minima or maxima and give a more complete search of the search space.

#### 1.2.3 Selection

Selection is one important mechanism for EC. It is the process of selecting individuals in current population to form a new population. Commonly, selection helps to propagate good chromosomes to the next generation while it also preserves diversity in population by selecting other kind of chromosome as well. There is a large number of selection methods used in ECs. Some commonly used selection methods are elitism, roulette-wheel, tournament and generational selection. Sometimes, using only one method of selection may not provide the required number of selected individuals to form a new population. Absent chromosomes can be filled by combining one method of selection with others or generating chromosomes randomly or according to some set of rules. These would help in exploring a larger search space and prevent the population from being concentrated around a local solution when there may be a better, global solution available. Increasing randomness by reducing the number of individuals selected by selection methods also increases diversity in a population increases the ability of the search to discover more solutions from a search space. If the randomness is increased too much, the system may be unlikely to find reasonable solutions. In other words, the system is likely to guess for solutions more than evolving towards a solution. This is a trade-off in forming new populations that designers should take into account.

Elitism selection selects a number of individuals according to a specified number or the percentage of the total number of individuals in the population. Mostly, elitism selection selects only the best solutions available in the population to propagate to the next. This ensures that while the search explores the search space, best solutions found are reserved.

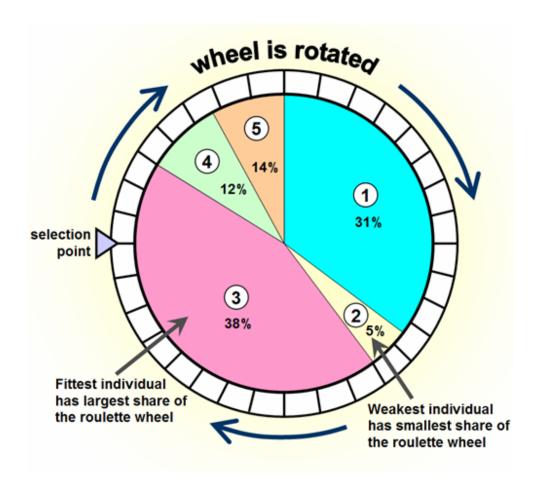

Roulette-wheel selection derives its concept from the roulette game where the entire space of the wheel is divided based on individuals' fitness values. The selection is virtually done by randomly spinning the wheel. The chance of picking an individual is proportional to its fitness value. There are some variations of this kind of selection which perform better in some applications. Figures 1.3 illustrates Roulette-wheel selection.

Figure 1.3 A Roulette-wheel selection

In tournament selection, each population is sub-divided into groups and a single best individual is taken from each group to form the new population.

In generational selection, all the individuals from previous generation are taken to be the next generation.

#### 1.2.4 Evaluation

Evaluation is a process of measuring quality of a chromosome as a solution to a particular problem. In the evaluation process, fitness values, which can be considered as scores for individuals, will be assigned to all chromosomes in the population. An *Objective Function* is used to define the method for calculating fitness values so that particular chromosome may be ranked against all the other chromosomes. Selection process makes use of fitness value for selecting chromosomes for future generation. Generally, fitness values are mapped onto a real-number scale. Sometimes, the range for fitness values for some applications cannot be determined; only relative magnitudes of the values are take into account to judge individuals in the population. In this case, the fitness values may be turned into percentages of the sum of all fitness values.

#### 1.2.5 Termination Criteria

Termination criteria define how many generations the EC should run before supplying final solutions. Commonly, a search stops when a specified number of generations have been processed (generations based termination criteria) or when the fitness values are high enough for a particular application (fitness based termination criteria). These two termination criteria can also be combined together.

In generations based termination criteria, the search always runs for a certain specified number of generations. The advantage of this type of termination criteria is that we can limit the number of iterations. In some applications, the search process can

converge very fast compared to the specified number of generations. Even if an individual that would satisfy the needs of the application, the search still continues the run until it reaches the n-th generation specified in the termination criteria. This results in the wasting of time, power and effort to run the search. Usually, this type of termination criteria is used to find optimal point where search starts to be convergent and we are satisfied with individuals in current population. We can do the tune-up for the number of generations to that optimal point.

In fitness based termination criteria, a minimum value for the fitness value is specified. The search runs until it finds one or more individuals meeting that fitness criteria irrespective of the number of generations that has been processed [27]. If the specified fitness value is too high the search can take a very long time to run even individuals found are applicable for application. If no satisfactory solution is found the system may run indefinitely. We can do a trial-and-error experiment with this type of termination criteria to observe the range of fitness values that will be appropriate for this type of termination criteria.

We can mix the two termination criteria described above to form an intermediate termination criteria. By mixing the termination criteria, the search runs until one or more individuals with fitness values satisfy the minimum fitness value specified, or the number of generation specified is reached. The problems of generations based termination criteria and fitness based termination criteria, which are time wasting and infinite loops respectively, are solved but satisfactory individual is not always guaranteed.

#### 1.2.6 The General flow for algorithm

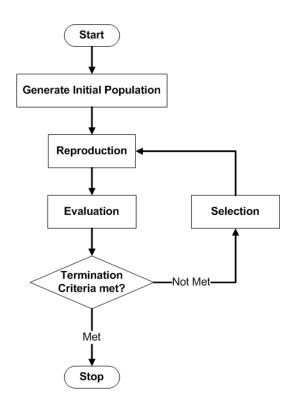

The processes described in section 1.1.1 - 1.1.5 are the basic processes that are used in general EC applications. Figure 1.4 shows the flow-chart describing the basic flow for EC.

Figure 1.4 The general flow for EC

First, an EC starts by generating initial population. Generating initial population is required and important because it places the search in a specific region on search space which can either be near or far from the optimal solution. Sometimes, placing the search near local-minima (-maxima) can result in the search convergencing quickly to a local-minima (-maxima). Locating the initial population too far from a solution might mean

many generations will be needed for convergence. Generating initial population can be done randomly or some knowledge can be applied to the process.

Then next step is reproduction in which crossover and mutation are performed in order to produce off-spring. Both parents and off-spring are evaluated in the evaluation step to obtain fitness values for every chromosome. The termination criteria, previously described in section 1.1.5, are applied to the population after the evaluation to see if an appropriate chromosome has been found. If the termination criteria are not met, the selection process performs individuals' selection to reduce the number of chromosomes that can propagate to the next generation. Without this reproduction the number of chromosomes will be accumulated resulting in processing time and memory problems. After the selection process is completed, the reproduction step is re-visited and crossovers and mutations are performed on the new population. This cycle is repeated until the termination criteria are met.

## 1.3 Evolutionary Computation on Hardware

#### 1.3.1 Implementation Problems

Evolutionary Computation (EC) has been used to solve many kinds of problems in the real world. The effectiveness of EC consists of its high suitability for parallel computer implementation; particular success in large search and optimization problems and in an ability to learn complex relationships in incomplete datasets [1]. There are many efforts to try to speed-up the process of solution evolution by implementing EC on a reconfigurable hardware platform such as FPGAs [21-24]. An application shown in [1] claims that a hardware-based EC with 1MHz clock-speed operates 2,200 times faster than

EC written in C and running on 100MHz workstation. This can be achieved by implementing the function of parent selection, crossover, mutation and survival in hardware in such a manner that each function can be executed in a single machine cycle.

Implementing an EC system in hardware is a hardship for those without hardware knowledge. To design an EC system knowledge, on low-level hardware interactions and debugging is required. In addition, different EC applications require different EC hardware architectures [24]. This makes changing an EC system in hardware much more difficult when the specifications of the application are changed.

Normally, changing parameters or methodologies used in a software-based EC system such as chromosome size, gene size and population size (or even crossover and mutation methods) requires a good framework and well designed system. Debugging can be done by inserting debugging statements and observe the probed variables through Graphical User Interface (GUI). Changing parameters and methodologies in a hardware-based EC system can be difficult because the user is not only required to have some knowledge on the EC system itself; but is also required to have some knowledge on hardware structure implementation and much forethought is needed to determine debugging channels for a particular hardware structure. Many EC systems have been implemented on a dedicated system designed for a specific application [5-7]. There is also a flexible hardware core for EC system which supports a number of applications [24]. Some of these are implemented on reconfigurable hardware in a Hardware Description Language (HDL). Changing parameters and methodologies can be done relatively easily by altering some parts of modules described by HDL. But this, too, requires knowledge on the particular hardware structure and HDL. A debugger is

convenient to have during development of an EC system but the debuggers that are used in HDL development platforms do not offer functionality to easily evaluate characteristics of EC systems. Getting information on the volutionary progress of a system is inconvenient at best with these HDL development tools and the amount of data needed to evaluate. And, even if a debugging system is developed for a particular EC application it will, most likely, not be appropriate for a different EC application.

The purpose of developing the GPEAT system for EC application is to obtain a General Purpose Evolutionary Algorithm Testbed which is flexible and reconfigurable for many EC applications. GPEAT is a substrate for implementing EC applications in hardware. GPEAT also facilitates the implementation of EC applications by providing a Graphical User Interface (GUI) which is used to quickly enter a description of a particular EC system that the user would like to put into hardware. This GUI is called *Parameter entry GUI* which will be described in chapter 3.

Our ultimate goal is to create a substrate for EC application in hardware that requires the user to only have minimal hardware skills to develop EC systems on and is flexible enough that it can be used for any number of applications. The structure for the substrate would be similar to FPGA which has Logic Elements (LE) and Memory Blocks. Some functional elements that could be reconfigured according to user specification would be derived to enable efficient EC implementation. A Graphical User Interface (GUI) for configuring this flexible substrate for EC application would greatly ease the implementation of EC application on hardware and reduce implementation time.

#### 1.3.2 Debugging Problems

Debugging an EC system in hardware is similar to debugging an SoC (System-on-a-Chip). One major problem for debugging SoCs is visibility. Normally, an EC system takes input from users (initial population, parameters for Random Number Generator etc.) and produces outputs which are possible solutions to the problem. If something goes wrong and the system does not produce appropriate outputs, debugging is needed to correct the problem. Since we have no access to components of EC system on silicon, some methodologies such as signal tapping (routing internal nodes to external pins to see what is happening) [28] are needed. To facilitate the debugging process, a debugging platform has to be defined for the GPEAT.

An example of low-cost debugging platform for SoC is proposed in [29] where a dedicated TAM (Test Access Mechanism) controller controls communication between CUDs (Core-Under-Test) and IEEE 1500 modules. "IEEE 1500 standard is a scalable standard architecture for enabling test reuse and integration for embedded cores and associated circuitry" [30]. The CUD in our case is the GPEAT core and the IEEE 1500 modules would be the debugging modules. This is an example which suggests to us how to build a reusable debugging platform for GPEAT system that can be used for any system developed to run on GPEAT.

One may argue that a simulator can also be used for debugging a hardware model before being downloaded to a reconfigurable device. One major problem for using simulator is that the user has to have a great deal of knowledge or experience with the GPEAT system architecture. Users would be required to understand signals integrity in

the system. A simulator shows the circuit responses for a fixed time period and, since we cannot determine how long the algorithm would take to converge, it would require a tremendous amount of data logging on a simulator to make sure we have the necessary data for analysis after a run. Users would have a lot of work to get the stored numerical data into a form that would give them useful data.

In this version of GPEAT, a hardware platform for debugging EC systems and debugging software are described. They will assist the user in debugging of the system and to perform performance checks on the implemented EC system. The software only provides simple visualization and data tracking for evolutionary process but makes a complete set of the data from the run available to the user for specific evaluations. One of our goals is to distribute GPEAT core and associated software as an open-source package in research communities. Further improvement can be achieve by distributing the debugging software to groups of users and obtain feedback and additional requirements from users. Different applications may need different requirements and visualizations for observing their evolutionary process, but we believe that some of them share commonality for building a generalized debugging software. Because complete data is made available to the user, building customized debugging software for a particular application is also possible.

#### 1.3.3 Hardware Platforms

The development of EC applications on artificial systems has been investigated for many years. Currently, there are no programmable substrates available made specifically for EC systems though flexible reconfigurable devices are most commonly

used as substrates for EC systems in publications. Since most applications for EC are combinatorial optimization problems, (function optimization problems) these problems can be implemented using chromosome representation in binary-string, integer and real-valued form. For example in [24], it is presented that "binary encoding is the most probable form for many of the problem in the industrial engineering world. Real-valued encoding is best used for function optimization problems. Integer encoding is best for combinatorial optimization problem." These three representations can be implemented on platforms for reconfigurable digital devices and, therefore, we limit our discussion to these platforms. There are three categories of programmable platforms available and they are SPLDs (Simple Programmable Logic Devices), CPLDs(Complex Programmable Logic Devices) and FPGAs (Field Programmable Gate Arrays). The description and characteristic of these three platforms are shown in Table 1.1 to Table 1.3.

| SPLD Characteristic        | Range                                  |

|----------------------------|----------------------------------------|

| Number of pins             | 16 to 28 pins                          |

| Number of macro cells      | 8 to 24 logic cells                    |

| Number of flip-flops (FFs) | 8 to 24 FFs                            |

| Configuration technology   | EPROM, EEPROM                          |

| Power-up status            | Nonvolatile                            |

| Programmability            | Can be reprogrammed after being erased |

| Programming mechanism      | Generally programmed off-board         |

| Size                       | Small                                  |

Table 1.1 SPLD Characteristic [25]

| CPLD Characteristic        | Range                           |

|----------------------------|---------------------------------|

| Number of pins             | 44 to 300+ pins                 |

| Number of macro cells      | 32 to 500+ logic cells          |

| Number of flip-flops (FFs) | 32 to 500+ FFs                  |

| Configuration technology   | EEPROM, EPROM, FLASH            |

| Power-up status            | Nonvolatile                     |

| Programmability            | Can be reprogrammed             |

| Programming mechanism      | Can be programmed in-circuit    |

| Size                       | Medium                          |

| Equivalent Gate Count      | 900 to 20,000+ equivalent gates |

Table 1.2 CPLD Characteristic [25]

| FPGA Characteristic        | Range                              |

|----------------------------|------------------------------------|

| Number of pins             | 50+                                |

| Number of macro cells      | 5,000+                             |

| Number of flip-flops (FFs) | 5,000+                             |

| Configuration technology   | Flash, EEPROM                      |

| Power-up status            | SRAM: volatile, OTP: nonvolatile   |

| Programmability            | SRAM: can be reprogrammed, OTP: no |

| Programming mechanism      | SRAM: can be programmed in-circuit |

| Size                       | Medium to Large                    |

| Equivalent Gate Count | 10,000+ equivalent gates |

|-----------------------|--------------------------|

|                       |                          |

Table 1.3 FPGA Characteristic [25]

Hardware Description Language (HDL) to describe hardware architecture such as VHDL (VHSIC Hardware Description Language) or Verilog can be used to program these reconfigurable digital platforms. Hardware architecture designed with VHDL or Verilog is synthesized by a Synthesis Tool which compiles and maps HDL codes into an implementation technology for reconfigurable devices of ASIC (Application Specific Integrated-Circuit). Examples for synthesis tools are Xilinx® XST, Synopsis Synplify and Sonata. Then, this synthesized design will be used to generate a configuration bitstream by tools provided by reconfigurable device manufacturers such as Xilinx®, Altera®, Aldec® and Actel®. In this literature, we use a reconfigurable device provided by Xilinx®; Xilinx® XST and Xilinx® ISE for synthesis process and generating configuration bitstream.

The reconfigurable device platform most commonly used in this literature is an FPGA which has a high-density of logic cells. The GPEAT design includes a core which performs general tasks for EC application and an embedded-debugger providing interfaces with host-PC for debugging purpose. The sizes of these two components of GPEAT system vary according to size of the chromosomes and the population size of the system. The component which utilizes the most resources in FPGA is the GPEAT core. As suggested in [26], experiments were conducted on the GPEAT system and the resource usage is shown in Table 1.4. The equivalent numbers of gates used in these particular applications vary from 10,000 to 30,000 gates which suggest that a high-density reconfigurable device must be used.

Table 1.4 Design analysis table [26]

|                    |                                                                      | Actual |                | Old            | New            |                |

|--------------------|----------------------------------------------------------------------|--------|----------------|----------------|----------------|----------------|

|                    |                                                                      | number | Exp 1          | Exp 3          | Exp 1          | Exp 3          |

| Logic utilization  | Total Number Slice registers                                         | 9,312  | 889<br>(9%)    | 1264<br>(13%)  | 1,498<br>(16%) | 753<br>(8%)    |

|                    | <ul><li>used as Flip<br/>Flops</li><li>used as<br/>Latches</li></ul> |        | 856<br>33      | 1,250<br>14    | 1,464<br>34    | 739<br>14      |

|                    | Number of 4 input<br>LUTs                                            | 9,312  | 1,343<br>(14%) | 1,559<br>(16%) | 1,927<br>(20%) | 1,186<br>(12%) |

|                    | Number of occupied Slices                                            | 4,656  | 1,114<br>(23%) | 1,416<br>(30%) | 1,734          | 977<br>(20%)   |

|                    | <ul><li>only related logic</li><li>unrelated</li></ul>               |        | 1,114          | 1,416          | 1,734          | 977            |

|                    | logic                                                                |        | 0              | 0              | 0              | 0              |

|                    | Total Number of 4 input LUTs                                         | 9,312  | 1,628<br>(17%) | 1,799<br>(19%) | 2,212<br>(23%) | 1,426<br>(15%) |

|                    | <ul><li>used as logic</li><li>used as a</li></ul>                    |        | 1,343          | 1,559          | 1,927          | 1,186          |

| ution              | route-thru  used for                                                 |        | 253            | 218            | 253            | 218            |

| Logic Distribution | Dual Port<br>RAMs                                                    |        | 32             | 22             | 32             | 22             |

| ogic l             | Number of bonded IOBs                                                | 232    | 81 (34%)       | 81(34%)        | 81(34%)        | 81(34%)        |

| I                  | • IOB Flip<br>Flops                                                  |        | 48             | 11             | 50             | 9              |

|                    | Number of GCLKs                                                      | 24     | 4 (16%)        | 3(12%)         | 4(16%)         | 3(12%)         |

|                    | Number of<br>MULT18X18SIOs                                           | 20     | 1 (5%)         | 1(5%)          | 1(5%)          | 1(5%)          |

|                    | Total equivalent gate count for design                               |        | 21,070         | 24,091         | 30,098         | 17,731         |

|                    | Additional JTAG gate count for IOBs                                  |        | 3,888          | 3,888          | 3,888          | 3,888          |

# 1.4 Report organization

In Chapter 1, we presented the basic theory for Evolutionary Computation along with the hardware implementation and issues for EC. Chapters 2 present the background for GPEAT and prior works. Specification and functionality of GPEAT is also described. The GUI which is used to configure GPEAT is described in Chapter 3 along with the tool for designers to integrate design of GPEAT into the GUI. Chapter 4 describes the architecture and ASM charts of debugging hardware which is attached to GPEAT core. The Debugging GUI which is the associating software used with debugging hardware is presented in Chapter 5. The results for hardware simulation for debugging hardware and hardware usage in FPGA are reported in Chapter 6. Conclusion and Future work is described in Chapter 7.

# **CHAPTER 2**

# REVIEW OF THE EVOLUTIONARY HARDWARE TESTBED (GPEAT)

#### 2.1 Introduction

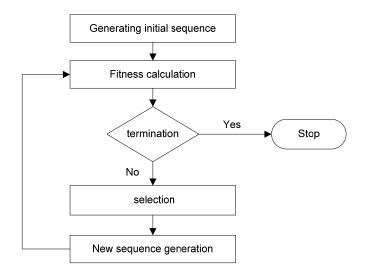

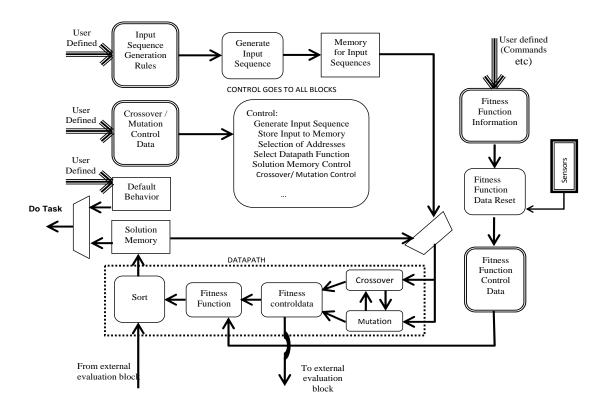

The GPEAT system is a testbed which implements its hardware framework on a Field-Programmable-Gate-Array (FPGA). GPEAT is a general purpose evolutionary algorithm testbed which allows users to create and run EC systems without hardware knowledge. This claim is supported by analysis of the patterns found in 40 to 50 published papers on EC hardware systems and the information from books and experts. The paper [8-18] were some of the more important papers used in this analysis. The pattern found through the analysis of these references allowed us to find a general framework which all of the systems we examined could be reproduced. This EC flow can be generalized as shown in Figure 2.1.

Figure 2.1 Simplified EC hardware flow

Each block of Figure 2.1 [19] has a specified function that was found to be necessary in satisfying at least one of the applications and/or references examined. The initial data is generated by the initial sequence generation block, and is either generated randomly or according to some set of rules. The fitness calculation block supports only intrinsic or extrinsic evaluation on this version of GPEAT but will support internal evaluation according to a user specified rule set by GPEAT in future versions. If the termination criteria is met the system stops. Termination criteria may be a maximum number of cycles through the flow or when the system finds a solution with a suitable fitness. The selection block picks which members of the present iteration through the flow should go on to the next iteration of the flow. The new sequence generation block uses fixed types of genetic operators to create the next set of possible solutions to the problem. To extend this system for flexibility and to give it the ability to be programmed easily to implement a different EC system each and every block shown in Fig 2.1 must be generalized. This generalization is achieved by hardware constructs specific to

implementing each EC system block that are reconfigurable through a simple set of parameters and created to specifically carry out the block's job efficiently in time and hardware resources. For example, the new sequence generation block is easily reconfigured to use a variety of genetic operators as specified by the user. The system as a whole must also be flexible. For example, the fitness block should support both intrinsic and extrinsic evaluations. Our system provides all the necessary features needed for reconfiguring to a variety of EC systems.

# 2.2 GPEAT User Interface and Parameters mapping

The hardware framework is functionally divided into multiple sections. A section will be configured by parameters to be provided by the user. The user needs to be given the ability to enter these parameters by some means which is flexible, user-friendly and no hardware knowledge required. A good user interface is needed for general purpose system in order to hide the details of the hardware and make design and fine tuning of a system easy. These requirements lead to the creation for a Graphical-User-Interface which is called GPEAT user interface (GUI) in this thesis. Our system provides a friendly graphical interface through which the user can communicate easily with the system.

The GUI provides six sets of parameters which are used to configure the hardware framework for a particular EC application. These six groups contain information regarding initial population generation, crossover and mutation control, system control, output control, fitness function information and sensors interface information. Some of

these parameters are mandatory while others are optional. This will be discussed in detail in Chapter 3.

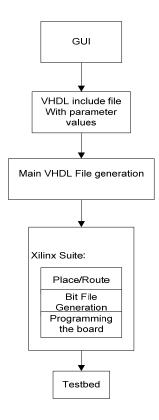

As mentioned, the parameters are entered through the GUI. The GUI maps the parameters into a VHDL include file which is accessible by the GPEAT main VHDL code. The Main VHDL, the include file and other essential files are generated by the GUI accordingly to the settings that user has specified. These VHDL sources are then configured using the Xilinx® Design Tools Suit (ISE) for upload to the FPGA. Xilinx® tools are used to partition and place and route design, generate bit files and, finally, downloading designs to the Xilinx® Spartan 3E<sup>TM</sup> board. This flow is shown in Figure 2.2.

Figure 2.2 GPEAT configuration flow

#### 2.3 Structures for the hardware framework

Based on the EC parameters set through the GPEAT user interface, the FPGA is programmed. The blocks shown in Fig. 2.2 can be divided into the six parameter groups mentioned in the previous section. The initial population generation parameters, crossover and mutation control parameters, central control parameters, output control parameters, fitness function parameters and sensors parameters. The thicker arrows in Figure 2.3 specify blocks whose function is determined by user input through the GUI. The function of the central control block is to control all the other blocks and is sequential logic. The other blocks are memory or largely combinational blocks and depend on the instructions from the central control block. The functions of these blocks are explained in the following sections.

Figure 2.3 Hardware Block Diagram

#### 2.3.1 Initial Population Generation blocks

The initial population generation section of GPEAT is made up of the input sequence generation rule database block, input sequence generation block and the memory for storing the generated chromosomes (Figure 2.3 [19]). In the input chromosome rules generation block, rules provided by the user through the GUI are framed to generate initial chromosomes. The input sequence generation block will generate chromosomes based on the input chromosome rules generation block's information. Here, one option is to use a random number generator to generate those chromosomes. The user may also specify a single value for all chromosomes or exact values for each chromosome. As an example of a case where all initial population

individuals are all set to be equal (of population size 3) could be 1111, 1111, 1111 but, after a random flip bit mutation, they might become 1011, 1110 and 0111. These generated or user specified chromosomes form the initial population. The initial population size is given by the input parameter "population size". As the initial population is sent for reproduction a new set of chromosomes is produced for the subsequent generation. This is one example of where hardware has an advantage over software: As the present population is being evaluated and reproduced, the next, new population members can be generated in parallel. In software the processing would be done in series and one process would not be able to start until previous one was done. The user has the option of setting rules to check the eligibility of the chromosomes generated. In that case, if a check is run, the initial population will be a set of legal chromosomes. If the system does not find a legal chromosomes after a specified number of iterations, the system will show an error message. Memory for the input sequence block stores initial population for that run, as all the chromosomes of initial population are not sent to the next block at once, the remainder must be held until needed. The size of the memory is determined by the size of the population.

#### 2.3.2 Crossover and Mutation Control blocks

In this part of GPEAT, there are three blocks: The crossover/mutation control information database block, crossover/mutation control block and crossover-and-mutation block. The crossover/mutation control information database block stores all information from the GUI regarding the reproduction operations to be performed upon generation of new chromosomes. It also determines the crossover type or mutation type to perform if the user opts for an exclusive reproduction type. The crossover/mutation

control block internally controls the two blocks in this group which are crossover and mutation blocks. In the crossover and mutation blocks, user specified crossover and mutations are carried out.

#### 2.3.3 Central Control blocks

The central control database block and central control block are included in this group. Mainly, this group of blocks holds the GPEAT system parameters that have been entered by the user through the GUI and then controls each and every block of the system shown in Figure 2.3. The central control database block specifically holds the GPEAT system parameters which describe the flow of the system and how the central control block should operate the system. The central control block connects to every building block of the GPEAT system. It sends control signals to blocks to activate or disable each block depending on the information stored in the central control data block. The central control block also controls the sequence of operations and data flow between blocks. In the initialization step, the control signal is sent to initial population generation blocks to generate an initial population. After having an initial population, crossover and mutation blocks are activated to perform the reproduction operations. The fitness evaluation blocks are then activated next. Fitness evaluation can be done internally or externally depending on the options that have been chosen by the user. The control signals activate the internal evaluation block if internal evaluation is chosen. Otherwise, the same control signals disables the internal evaluation block and operate the external evaluation part of GPEAT. After finishing the fitness evaluation process, the sorting block and the output block are

activated respectively. Again, because this is in hardware, processing is run in parallel as often as possible when there is no conflict.

#### 2.3.4 Output Control blocks

The sorting block, solution memory block and default output block comes under this group. This group's work is to sort all the solutions based on their fitness value and decide whether the default output or the best of the sorted solutions should be outputted. Chromosomes are also stored here for use in future generations. The sorting block carries out the sorting and the solution memory block stores the sorted chromosomes. The default output block holds the user specified default output and will output that until a solution is found that satisfies the threshold criteria set by the user.

Sorting is the slowest procedure in many systems. The best of the sorting techniques works at O(n log n) [20]. For example, the random number generator, crossover and mutation works at O(n). According to "Amdahl's law" to speed up the GPEAT system, the sorting block must be improved. For that, we have replaced the sort hardware with three bins labeled 80%-100% solutions (bin1), 60%-80% solutions (bin2) and 0%-60% solutions (bin3). Solutions are stored in respective bins depending on their fitness percentage. For example, solutions with fitness percentage between 90-100 goes to 90%-100% bin in no special order. The bins only need to be the size of the number of individuals that might be carried over to the next population (elitism rate x population size). In this way, sorting becomes on the order of O(constant) and the memory needed is only

$SortMemorySize = 3bins \times (ElitismRate \times Population)s$

The best solution by fitness value is always stored separately and will not be lost by overflow of bin 1.

#### 2.3.5 Fitness Function blocks

The fitness function blocks consist of the fitness function information block, fitness function data reset block, fitness function control data block and fitness function calculation block. These blocks are used to determine fitness value for chromosome based on specified parameters by user. Fitness values calculation can either be done internally or externally as explained in the previous sections (section 2.3.3.). In an internal evaluation, a set of rules defined by the user is stored in the fitness function information block. These rules are used by the fitness function data reset block and fitness function control data block to realize an objective function. Information from sensors can be used as input to objective function to make a dynamic objective function which evaluates chromosomes according the present operating environment. The fitness function block performs calculation described by the realized objective function. In an external evaluation, chromosomes stored in GPEAT system are sent out to some external evaluating environment. These external components then return the fitness values of chromosomes back to GPEAT system in system-usable format. When a chromosome is being sent out from the GPEAT system, it is sent out along with a start signal to the external evaluating component. The start signal synchronizes chromosome switching with chromosome acquisition process of the external component. When fitness value is completely calculated by the external component, the external component will send the fitness value back to the GPEAT system along with a done signal so that GPEAT knows

that a fitness value has been found for the chromosome under test and that fitness value should be stored.

#### 2.3.6 Sensors blocks

The use of sensor block is not available in this version of GPEAT. The GPEAT system breaks the barrier between the EC hardware system and real-life events by providing a bread board area to connect sensors to provide information about the environment. Sensors which are connected through the sensor block collect the raw data from operating environment and that information can be used for fitness values calculation. The objective function created for the fitness values calculation can be set up to change accordingly to the operating environment to find appropriate chromosomes at a particular time. Data from the sensors need to be converted into a system-usable format by some means such as using an analog-to-digital converter (ADC), a decoding block or some type of amplification. This conversion is needed because of the wide variety of sensors. For example, if a thermal sensor was used for a particular application, the output from those sensors would be analog and so must be converted to binary through an analog to digital converter. Once converted to a binary form the data can be used for processing.

# 2.4 Debugging GPEAT system

When a GPEAT system is configured for a particular application, the user provides configuration information to the system. Sometimes the user might never have envisioned the problems that would come with their settings. For an application, the configuration and development of the system may involve a trial-and-error process which

may require many iterations of setting parameters and then watching the results. Besides providing inputs and obtaining outputs from the system, the user might want to see the intermediate states and how the internal mechanisms are working in order to explain why a particular output resulted, or to tune up the system for optimal performance.

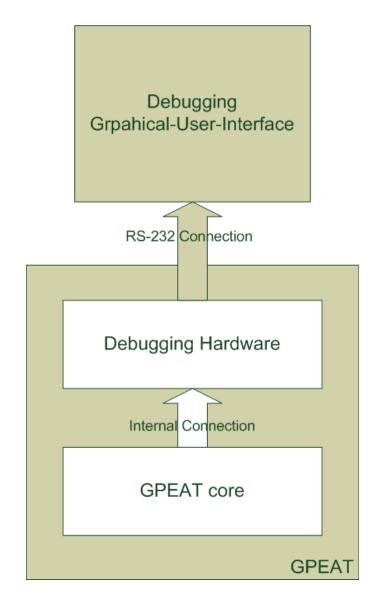

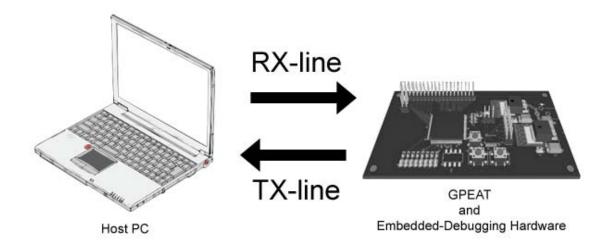

GPEAT configuration flow in Figure 2.2 but, in addition to the basic EC system, GPEAT also provides a debugging interface for the user to obtain information and trends of the system during runs. GPEAT has a built-in debugging hardware interface used for obtaining and verifying the system parameter information and all population- and chromosome-data. The debugging hardware sends information back to host PC where a debugging Graphical-User-Interface runs. Information is sent back from the system through an RS-232 connection and where it is displayed in graphical form. Figure 2.4 shows the connection diagram for GPEAT debugging interface.

Figure 2.4 Debugging connection diagram

# **CHAPTER 3**

# GRAPHICAL USER INTERFACE DESIGN

# 3.1 Parameters Entry GUI

The Parameters Entry GUI is used to configure the GPEAT system. It provides a graphical interface for user to enter the parameters to configure GPEAT system for a particular application. Some of these parameters are required and some are optional but they all are used to generate VHDL codes which are used to construct the GPEAT core and built-in debugging hardware. As shown in Figure 2.2, the GUI generates GPEAT core accordingly to the parameters that a user has specified by mapping the parameters into a VHDL include file. Then, these VHDL files are joined in an FPGA project file using Xilinx® Design Tools Suit (ISE) to generate a FPGA configuration file (.bit file).

The GUI stores the information for the VHDL codes and parameter mapping into a single binary file (GPEAT.dat). When the GUI generates the VHDL codes for the GPEAT core and debugging hardware, it reads this binary file to obtain information regarding the codes generation such as the amount of file required to construct GPEAT, the content of the codes and information for parameter mapping. The binary file can be generated by a GPEAT developer using *GPEAT binary data-file encoder* which is another GUI used together with the parameter entry GUI. The binary data-file encoder will be described in section 3.2.

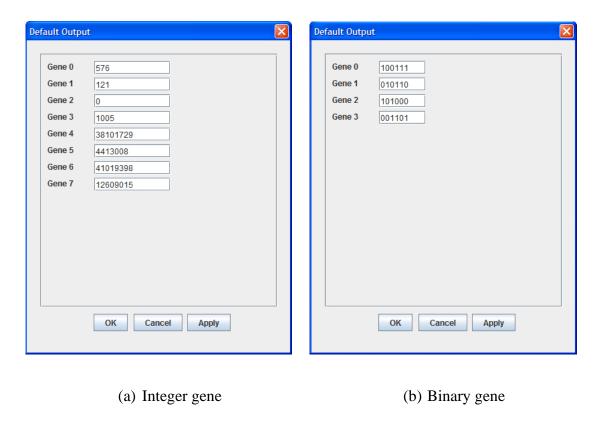

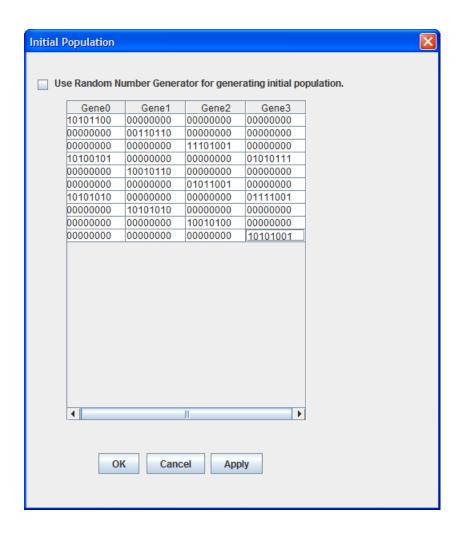

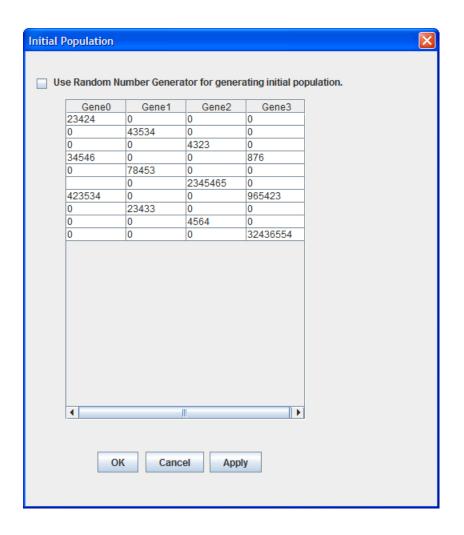

The parameter entry GUI separates parameters into five categories which are Input (Sensors), Default Output, Initial Population, Fitness Rules and Debugger. Each of these categories is described in following section (section 3.1.2-3.1.7). First, the workspace of the GUI will be described in section 3.1.1.

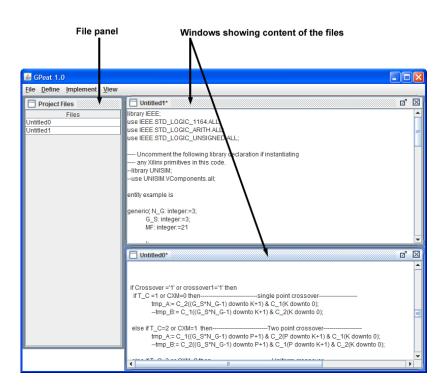

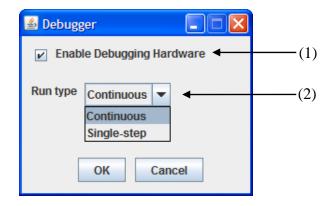

### 3.1.1 Workspace

The workspace shows the files which contain VHDL codes for the GPEAT core and debugging hardware. It contains a file panel, which summarizes the files required for constructing system and separate windows showing content of the files. These windows will be visible only when the user chooses to view the contents of the files. If user wants to view the contents of a file but the window showing the contents of the file does not appear, the user can recall the window by doing double-click on the file listed in file panel and then the window of the file will appear. Figure 3.1 shows workspace of the GUI.

Figure 3.1 Workspace

#### 3.1.1.1 Creating/Loading/Saving Project

Before working with the parameter entry GUI, the user has to create or load a project. A project file is named with the extension ".gpt" and stores values for the GPEAT parameters. Creating a new project initializes all GPEAT parameters to default values and then the user has to specify the parameter values they want to override those default values manually. This will be discussed in section 3.1.2 to 3.1.7. Saving a project will allow the user to continue work later or save the values of the parameters in a file. The user can create, load and save project by clicking  $Files \rightarrow Project \rightarrow New$  Project,  $Files \rightarrow Project \rightarrow Open$  Project and  $Files \rightarrow Project \rightarrow Save$  Project respectively.

#### 3.1.1.2 Creating/Loading/Saving a Source

User can also add additional sources as required in addition to the GPEAT core codes. The added code can be used to work with GPEAT as, for example, an intrinsic testing block would need to do. The GUI does not help the user create these additional blocks and the user would have to have hardware design skills in order to create them. The user can create, load and save added source by clicking  $Files \rightarrow New$  Source,  $Files \rightarrow Open Source$  and  $Files \rightarrow Save Source/Save Source$  as respectively.

#### **3.1.2 System**

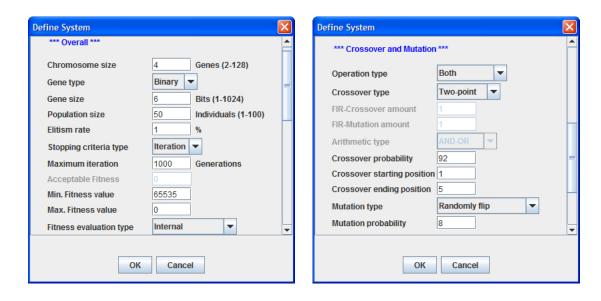

The system parameters window can be access by clicking  $Define \rightarrow System$  from the menu bar of the GUI. The system parameters are used to define the input/output of the system, operations during runs and the behavior of the GPEAT system. Some of these parameters are essential for VHDL generation because they are used to define the structure of GPEAT system for a particular application. In the

Define System window, the window is divided into three sections grouped by the functions of the parameters. Figure 3.2(a), Figure 3.2(b) and Figure 3.2(c) show three sections of Define System window which are the overall section, the crossover and mutation section and the random number generator section.

(a) Overall section

(b) Crossover and mutation section

(c) Random number generator section

Figure 3.2 System parameters window

In the overall section, the parameters which define the structure of the GPEAT system are set. For example: the chromosome size, gene size, gene type and population size are grouped in this section. These parameters are the same parameters shown in Figure 3.2(a) and are described and summarized below in Table 3.1 and Table 3.2 respectively.

| Parameter              | Description                                                                                               |  |

|------------------------|-----------------------------------------------------------------------------------------------------------|--|

| Chromosome size        | The length of chromosome (number of genes contained a chromosome).                                        |  |

| Gene type              | Specify data type contained in each gene. This can be a binary number or integer number (32-bit).         |  |

| Gene size              | Specify number of bits contained in a gene for binary                                                     |  |

| Population size        | typed gene.  Specify number of chromosomes in a population (each                                          |  |

| Elitism rate           | iteration)  Specify number of best chromosomes in percent that will                                       |  |

| Stopping criteria type | propagate to next generations.  Specify condition for system to stop run. It can based on                 |  |

| Maximum iteration      | number of iteration or fitness-value based.                                                               |  |

| Acceptable Fitness     | The maximum number of generations processed.  The acceptable fitness value (for termination), if Fitness- |  |

| -                      | based termination criteria are chosen.                                                                    |  |

| Min. Fitness Value     | Minimum Fitness Value that will possibly be found in the                                                  |  |

|                         | system. Maps to 0% fitness value                                                             |

|-------------------------|----------------------------------------------------------------------------------------------|

| Max. Fitness Value      | Maximum Fitness Value that will possibly be found in the system. Maps to 100% fitness value. |

| Fitness Evaluation type | Selects module for fitness evaluation. The type can be internal module or external module.   |

Table 3.1 System Parameter descriptions

| Parameter               | Values                             | Default Value | Unit        |

|-------------------------|------------------------------------|---------------|-------------|

| Chromosome size         | 2 to 128                           | 8             | Genes       |

| Gene type               | Binary / Integer                   | Binary        |             |

| Gene size               | 1 to 1024                          | 1             | Bits        |

| Population size         | 1 to 100                           | 20            | Chromosomes |

| Elitism rate            | 1 to 100                           | 10            | Percent     |

| Stopping criteria type  | Iteration / Fitness                | Iteration     |             |

| Maximum iteration       | User specified                     | 0             |             |

| Acceptable Fitness      | User specified                     | 0             |             |

| Min. Fitness Value      | User specified                     | 0             |             |

| Max. Fitness Value      | User specified                     | 0             |             |

| Fitness Evaluation type | Internal / Intrinsic-<br>Extrinsic | Internal      |             |

Table 3.2 System Parameters

# 3.1.3 Input (Sensors)

This category of parameter has not been implemented in the GUI because the sensors blocks (previously explained in chapter 2) have not been completed but will be completed for the next version of GPEAT. This category of parameters is for configuring sensors inputs to the GPEAT system and is used as a part for fitness evaluation process. Users can add sensors to the system through the GUI. The user must specify the type of sensors and its type of input. The parameters for each sensor are summarized in Table 3.4.

| Parameter                       | Description                                                |  |  |

|---------------------------------|------------------------------------------------------------|--|--|

| Sensor Name                     | The name for sensor which will be used as                  |  |  |

|                                 | signal name in VHDL code.                                  |  |  |

| Туре                            | Output type of sensor (analog or digital).                 |  |  |

| Number of Bits (Digital)        | Number of bits from output of sensor.                      |  |  |

| Supply Voltage                  | Supply voltage to the sensor.                              |  |  |

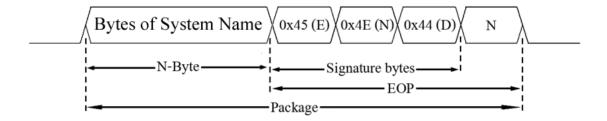

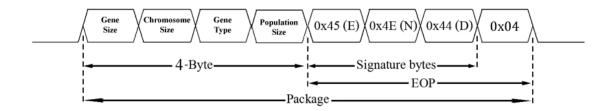

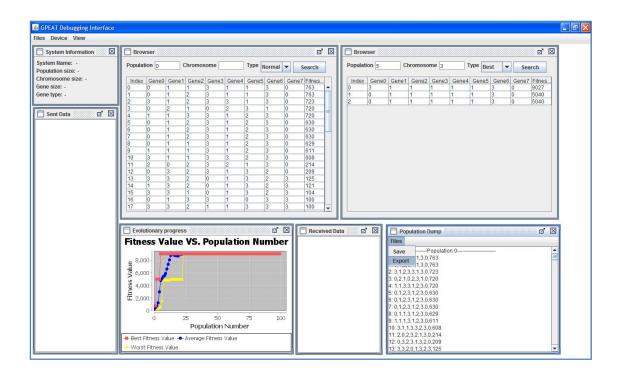

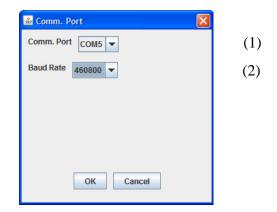

| Upper Limit for sensor (Analog) | Maximum voltage or current from output of analog sensor.   |  |  |