# DEVELOPMENT OF PULSED POWER SOURCES USING SELF-SUSTAINING NONLINEAR TRANSMISSION LINES AND HIGH-VOLTAGE SOLID-STATE SWITCHES

# A DISSERTATION IN

Electrical and Computer Engineering & Mathematics

Presented to the Faculty of the University of Missouri-Kansas City in partial fulfillment of the requirements for the degree

# DOCTOR OF PHILOSOPHY

# by A N M WASEKUL AZAD

B.S., Electrical and Electronic Engineering, Bangladesh University of Engineering and Technology, 2012

> Kansas City, Missouri 2021

© 2021

# A N M WASEKUL AZAD

# ALL RIGHTS RESERVED

# DEVELOPMENT OF PULSED POWER SOURCES USING SELF-SUSTAINING NONLINEAR TRANSMISSION LINES AND HIGH-VOLTAGE SOLID-STATE SWITCHES

A N M Wasekul Azad, Candidate for the Doctor of Philosophy Degree University of Missouri-Kansas City, 2021

## ABSTRACT

The demand for short pulses capable of delivering high peak power is increasing by leaps and bounds over the last few decades. These pulses are garnering attraction from a wide variety of end-users associated with the military, medical, industry, etc. The diverse nature of the potential application spaces asks for agility and customization capability of the pulses in terms of frequency, voltage level, and current level to fit varying degrees of requirements. Several pulsed power approaches can generate high-power pulses including direct switchbased pulsers, pulse forming lines (PFLs), Marx generators, nonlinear transmission lines (NLTLs), pulse transformers, etc. Among these pulsed power approaches, NLTL showcases frequency-agility in output pulses that distinguishes it from the rest of the competition. NLTLs either sharpen the input pulse or break down the input pulse into a finite number of pulses with decaying amplitudes, known as solitons. This research work combines the uniqueness of the NLTL in terms of frequency agility and the robustness of the laterally-diffused metal-oxidesemiconductor (LDMOS) devices to produce self-sustaining oscillations from a single input pulse. To date, this research work is one-of-a-kind in the field of NLTLs used for generating medium-power RF signals. Multiple NLTLs have been fabricated to identify the best available candidate showcasing excellent nonlinearity. The NLTL, coupled with a custom high voltage pulse generator, an LDMOS based amplifier, and RF matching networks constitute a closed-loop setup that produces solitons with a peak power close to 2.1 kW. The experimental results are verified by LTSpice simulations as well.

Direct high-voltage (HV) switch-based pulser is another intriguing option to produce pulsed power in a compact footprint. This approach can be easily streamlined compared to other pulsed power approaches thanks to the reduced number of required components. Traditionally, spark gap switches have been predominantly utilized in direct HV switch-based pulser. High voltage withstanding capability and high current carrying capability of the spark gap switches solidified their position during the early stages of pulsed power system development. That being said, the brilliance of the spark gap switches is overshadowed by the long jitter, limited lifetime, and inability to operate at higher switching frequencies which are some of the critical modern-day pulsed power requirements. To that end, the quest for an alternative switching candidate has led the researchers to solid-state semiconductor switches (e.g., MOSFETs, IGBTs, etc.) that can be employed in pulsed power systems. The solid-state semiconductor switches are inherently faster compared to the spark gap switches, thereby enabling operation at higher switching frequency as opposed to the spark gap switches. The lifetime of these switches is also much longer compared to the spark gap switches, and they offer mostly jitter-less operation. That being said, the voltage withstanding ability of the commercial-off-the-shelf (COTS) MOSFETs is limited to 3.3 kV which is inadequate for many pulsed power applications. Connecting multiple COTS MOSFETs in series is an intriguing way to increase the volage withstanding ability of the entire switch stack. However, ensuring voltage balancing among the series-connected MOSFETs during the OFF state as well as the switching transition is a major design challenge for the researchers working in this field. The capacitive coupling method is one of the mechanisms that ensure voltage balancing among the series-connected switches while occupying a smaller area compared to other competing methods. However, literature pertaining to capacitive coupling-based series-connected switches illustrates experimental results using a HV switch with a maximum stage count of two. This research work outlines the design and development process of a capacitively coupled 6.8 kV rated four-stage SiC switch. Simulation results exhibit excellent voltage balancing traits which are reinforced by the experimental results. Modularity has been introduced in the HV switch design to facilitate the scalability of the switch in terms of voltage withstanding capability. This feature allows the user to tailor the switch in accordance with the voltage requirement of a potential pulsed power application by connecting multiple modules in series. A 10 kV rated modular SiC switch has been designed and fabricated based on the capacitive coupling method. At a high voltage level (>5.7 kV), custom gate drivers are required to provide adequate galvanic isolation. To drive the 10 kV rated switch, a 10 kV rated custom isolated gate driver has been designed and developed. The design procedure of this custom gate driver is detailed in this dissertation. The modular SiC switch coupled with the custom isolated gate driver has been tested up to a supply voltage of 6 kV exhibiting excellent voltage balancing, thereby validating the modularity concept of the HV switch.

## APPROVAL PAGE

The faculty listed below, appointed by the Dean of the School of Graduate Studies have examined a dissertation titled "Development of Pulsed Power Sources Using Self-Sustaining Nonlinear Transmission Lines and High-Voltage Solid-State Switches" presented by A N M Wasekul Azad, candidate for the Doctor of Philosophy degree, and certify that in their opinion it is worthy of acceptance.

# Supervisory Committee

Faisal Khan, Ph.D., Committee Chair Department of Computer Science and Electrical Engineering

Majid Bani-Yaghoub, Ph.D., Co-discipline Advisor Department of Mathematics and Statistics

Masud Chowdhury, Ph.D. Department of Computer Science and Electrical Engineering

Ahmed Hassan, Ph.D. Department of Computer Science and Electrical Engineering

> Anthony Caruso, Ph.D. Department of Physics and Astronomy

| ABSTRACTiii                                                          |

|----------------------------------------------------------------------|

| LIST OF ILLUSTRATIONS xii                                            |

| ACKNOWLEDGEMENTS xvii                                                |

| CHAPTER 1 1                                                          |

| INTRODUCTION 1                                                       |

| 1.1 Motivation1                                                      |

| 1.2 Research Objective                                               |

| 1.3 Dissertation Outline                                             |

| CHAPTER 2                                                            |

| LITERATURE REVIEW OF PULSED POWER TECHNOLOGIES                       |

| 2.1 High-Voltage Switch Based Pulser7                                |

| 2.2 Pulse Forming Line                                               |

| 2.3 Nonlinear Transmission Lines 11                                  |

| 2.4 Marx Generator                                                   |

| 2.5 Pulse Transformer 15                                             |

| CHAPTER 3 19                                                         |

| FUNDAMENTALS OF NONLINEAR TRANSMISSION LINES (NLTLS) AND SOLITON     |

| GENERATION USING NLTL                                                |

| 3.1 Lumped Element Nonlinear Transmission Lines                      |

| 3.2 Gyromagnetic Nonlinear Transmission Lines                        |

| 3.3 Theory of Soliton Generation in Lumped Element Transmission Line |

| CHAPTER 4                                                              | 29 |

|------------------------------------------------------------------------|----|

| DESIGN OF A MEDIUM-POWER, SELF-SUSTAINING CONFIGURABLE SOLITON         |    |

| GENERATION CIRCUIT USING NLTL IN OPEN AND CLOSED LOOP                  |    |

| CONFIGURATIONS                                                         | 29 |

| 4.1 Design Procedure of the Self-Sustaining Soliton Generator          | 29 |

| 4.1.1 Capacitive NLTL                                                  | 30 |

| 4.1.2 LDMOS Based RF Power Amplifier and RF Transformer Based Matching |    |

| Networks                                                               | 33 |

| 4.1.3 High-Voltage Pulse Generator                                     | 37 |

| 4.2 Simulation Results                                                 | 41 |

| 4.3 Experimental Setup and Results                                     | 44 |

| 4.3.1 Experimental Setup                                               | 44 |

| 4.3.2 Experimental Results                                             | 47 |

| 4.4 Discussion and Future Research Direction                           | 50 |

| 4.4.1 Dual-diode NLTL Configuration                                    | 50 |

| 4.4.2 Increasing Peak Power and Center Frequency of Solitons           | 51 |

| 4.5 Conclusion                                                         | 53 |

| CHAPTER 5                                                              | 54 |

| SERIES-CONNECTED MOSFET BASED HIGH-VOLTAGE, HIGH-SPEED SOLID-          |    |

| STATE SWITCH                                                           | 54 |

| 5.1 Motivation                                                         | 54 |

| 5.2                                                                    | 59 |

| Fundamental Design Challenges of Series-Connected Solid-State Switch              | 59 |

|-----------------------------------------------------------------------------------|----|

| 5.3 Existing Techniques to Mitigate Fundamental Design Challenges Associated with |    |

| Series-Connected Solid-State Switch                                               | 60 |

| CHAPTER 6                                                                         | 68 |

| A SINGLE GATE DRIVER BASED FOUR-STAGE HIGH-VOLTAGE SIC SWITCH (                   | 68 |

| 6.1 Proposed Series-Connected Four-Stage High-Voltage Switch Architecture         | 68 |

| 6.2 Operating Principle of the Proposed Switch                                    | 69 |

| 6.2.1 Steady-State                                                                | 69 |

| 6.2.2 Turn-ON Transition                                                          | 70 |

| 6.2.3 Turn-OFF Transition                                                         | 71 |

| 6.3 Key Parameter Selection                                                       | 72 |

| 6.3.1 Gate Resistor Selection                                                     | 72 |

| 6.3.2 Coupling Capacitor Selection                                                | 73 |

| 6.3.3 Snubber Capacitor Selection                                                 | 74 |

| 6.3.4 Ferrite Bead Selection                                                      | 74 |

| 6.4 Simulation Results                                                            | 75 |

| 6.5 Experimental Setup and Results                                                | 76 |

| 6.5.1 Experimental Setup                                                          | 76 |

| 6.5.2 Experimental Results                                                        | 77 |

| 6.6 Conclusion                                                                    | 81 |

| CHAPTER 7                                                                         | 82 |

| A MULTILE VEL-MODULAR HIGH-VOLTAGE SIC SWITCH MODULE USING                             |

|----------------------------------------------------------------------------------------|

| CUSTOM HIGH-VOLTAGE ISOLATED GATE DRIVER                                               |

| 7.1 Proposed Modular Series-Connected Four-Stage High-Voltage Switch Architecture . 82 |

| 7.2 Operating Principle of the Proposed Modular Switch                                 |

| 7.2.1 Turn-ON Transition                                                               |

| 7.2.2 Turn-OFF Transition                                                              |

| 7.3 Key Parameter Selection                                                            |

| 7.3.1 Balancing Resistor                                                               |

| 7.3.2 Coupling Capacitors                                                              |

| 7.3.3 Gate Resistors                                                                   |

| 7.3.4 Snubber Capacitors                                                               |

| 7.3.5 Ferrite Beads                                                                    |

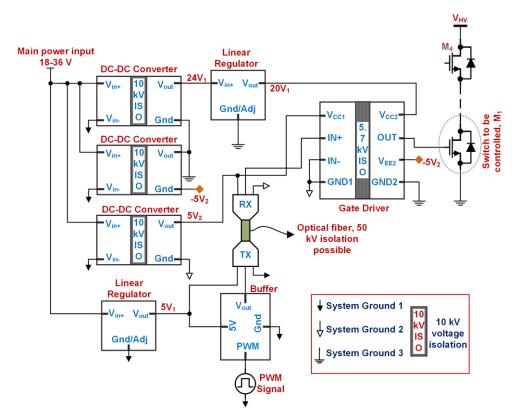

| 7.4 Design Details of a Custom High-Voltage Isolated Gate Driver                       |

| 7.4.1 Design Criteria of a Custom High-Voltage Isolated Gate Driver                    |

| 7.4.2 Isolation Transformer Based High-Voltage Isolated Gate Driver                    |

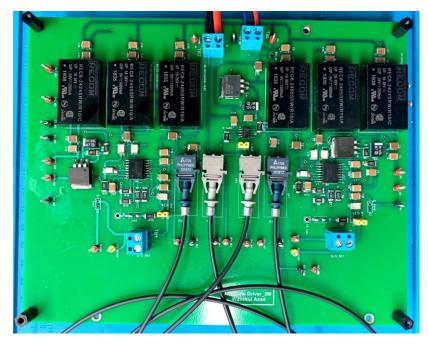

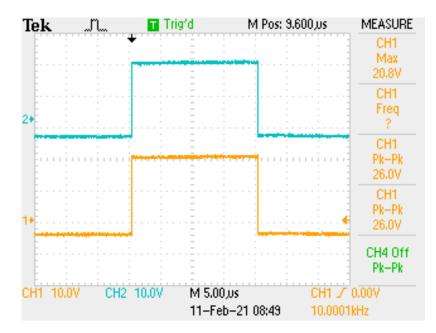

| 7.4.3 Commercial DC-DC Converter Based High-Voltage Isolated Gate driver 104           |

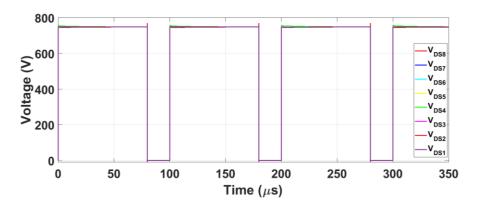

| 7.5 Simulation Results of the Modular High-Voltage Switch 110                          |

| 7.6 Experimental Setup and Results                                                     |

| 7.6.1 Experimental Setup111                                                            |

| 7.6.2 Experimental Results                                                             |

| CHAPTER 8                                                                              |

| CONCLUSIONS AND FUTURE WORK                                                            |

# A MULTILEVEL-MODULAR HIGH-VOLTAGE SIC SWITCH MODULE USING

| 8.1 Summary     |  |

|-----------------|--|

| 8.2 Future Work |  |

| REFERENCES      |  |

| VITA            |  |

# LIST OF ILLUSTRATIONS

| Fig. 1: Direct HV switch based pulser topology (b) Direct HV switch topology with active       |

|------------------------------------------------------------------------------------------------|

| droop compensation, snubber circuit and voltage signals at different points of interest [17],  |

| [18]                                                                                           |

| Fig. 2: Basic configuration of a single pulse forming line [26]                                |

| Fig. 3: Schematic of a basic Blumlein line configuration with one closing switch (solid line), |

| and a modification involving a second closing switch at the end of the pulse forming line      |

| (dotted line) [24] 11                                                                          |

| Fig. 4: Modular solid-state Marx modulator schematic [40] 14                                   |

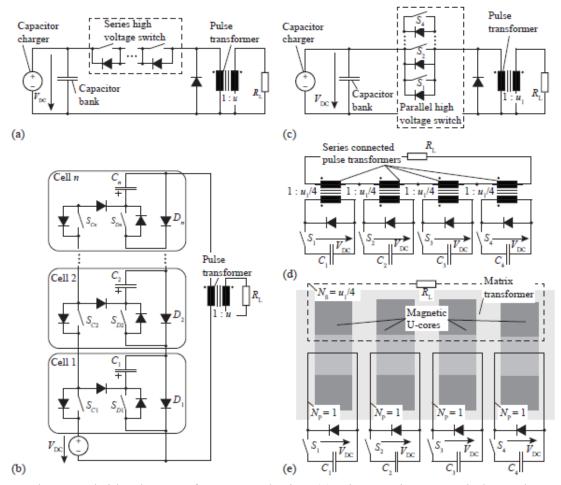

| Fig. 5: Hybrid pulse transformer topologies: (a) Direct series HV switch + pulse transformer,  |

| (b) Marx generator + pulse transformer. (c) Direct parallel HV-switch + pulse transformer (d)  |

| Series connection of four single pulse transformers with the same output behavior as in (c).   |

| (e) Matrix transformer solution with the same output behavior as in (c) and (d), which results |

| in lower transformer parasitic than in (c) and (d) [43]17                                      |

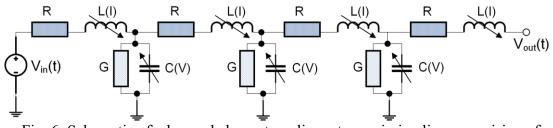

| Fig. 6: Schematic of a lumped element nonlinear transmission line comprising of nonlinear      |

| inductor and nonlinear capacitor [64]                                                          |

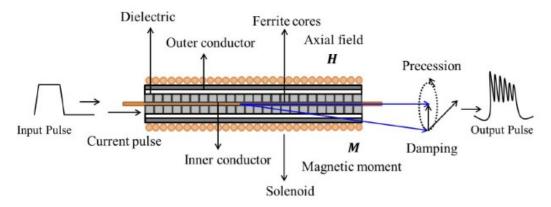

| Fig. 7: Precession of magnetic moment <i>M</i> in gyromagnetic line [72]                       |

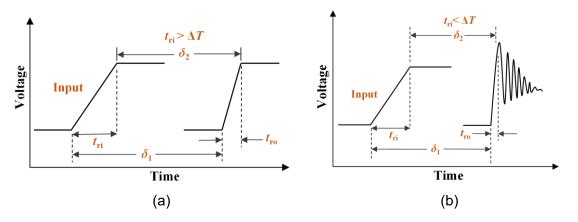

| Fig. 8: (a) Pulse compression (b) Soliton formation                                            |

| Fig. 9: (a) Schottky diode based 9-section NLTL (b) Varactor based 9-section NLTL 31           |

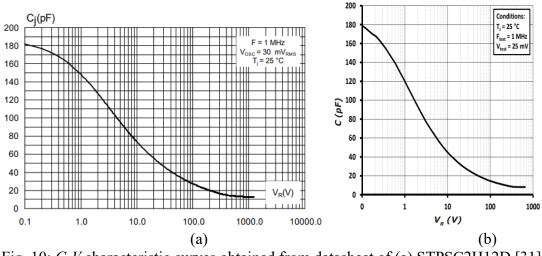

| Fig. 10: <i>C-V</i> characteristic curves obtained from datasheet of (a) STPSC2H12D [31] (b)   |

| C3D02060F [85],                                                                                |

|                                                                                                |

| [00] |

|------|

|------|

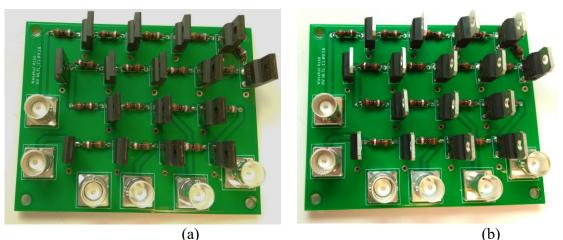

| Fig. 11: (a) 600 V rated Schottky diode based NLTL (b) 1200 V rated Schottky diode based                        |

|-----------------------------------------------------------------------------------------------------------------|

| NLTL                                                                                                            |

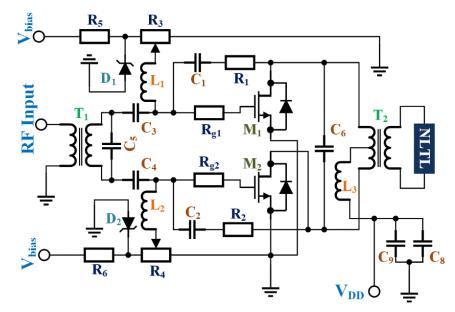

| Fig. 12: Schematic of the power amplifier with matching networks                                                |

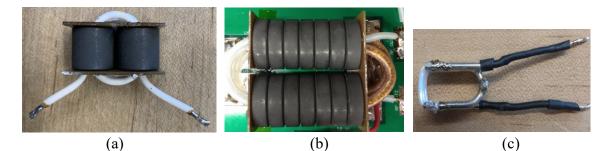

| Fig. 13: (a) Teflon insulated wire based RF transformer $(T_1)$ (b) RG-328 coaxial cable based                  |

| RF transformer $(T_2)$ (c) Semi rigid coaxial cable based RF transformer $(T_2)$                                |

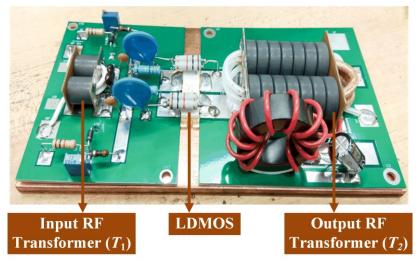

| Fig. 14: LDMOS based power amplifier (PA) with matching networks                                                |

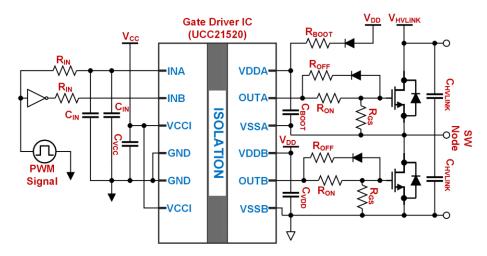

| Fig. 15: Schematic of the GaNFET based in-house pulse generator                                                 |

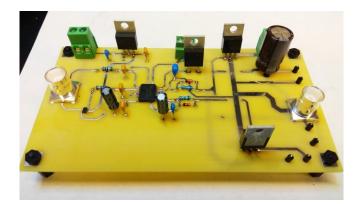

| Fig. 16: Fabricated prototype of the UCC21520 based in-house pulse generator 40                                 |

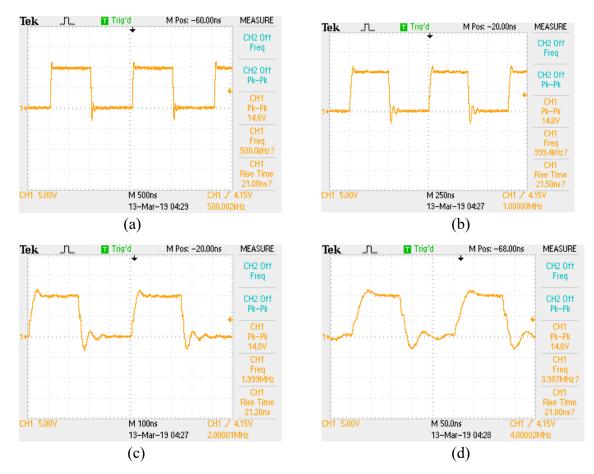

| Fig. 17: Output pulses from the in-house pulse generator with (a) 1000 ns pulse width (b) 500                   |

| ns pulse width (c) 250 ns pulse width (d) 100 ns pulse width 40                                                 |

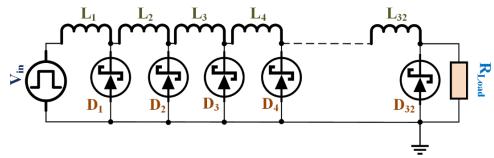

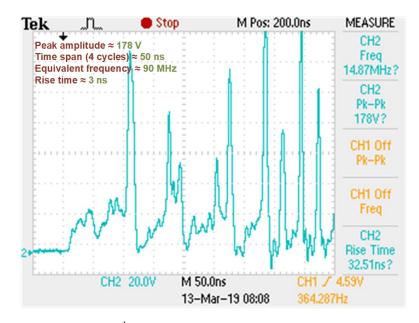

| Fig. 18: Schematic of the 32-section NLTL                                                                       |

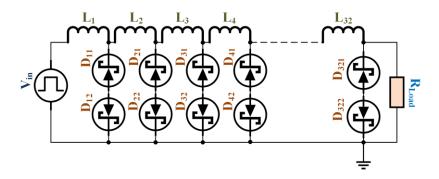

| Fig. 19: Solitons generated at different sections of the single-diode NLTL                                      |

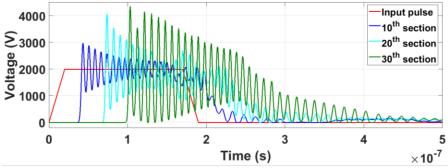

| Fig. 20: Simulated output from (a) 600 V rated Schottky diode based NLTL ( $V_{DD} = 10 \text{ V}$ ) (b)        |

| 1200 V rated Schottky diode based NLTL ( $V_{DD} = 10 \text{ V}$ )                                              |

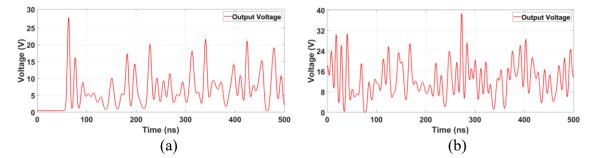

| Fig. 21: Simulated output across (a) 14 <sup>th</sup> section of the 1200 V rated Schottky diode based          |

| NLTL ( $V_{DD}$ = 10 V) (b) 14 <sup>th</sup> section of the 1200 V Schottky diode based NLTL ( $V_{DD}$ = 30 V) |

|                                                                                                                 |

| Fig. 22: Simulated output across the 11 <sup>th</sup> section of the 1200 V rated Schottky diode based          |

| NLTL (fourth phase)                                                                                             |

| Fig. 23: (a) Simplified block diagram of the closed-loop setup of the NLTL and PA with                          |

| excitation (b) Experimental setup of an NLTL-PA closed loop configuration                                       |

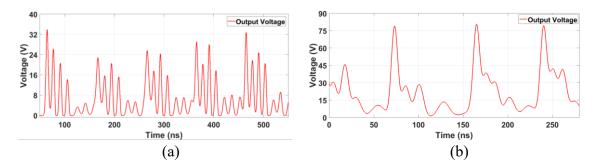

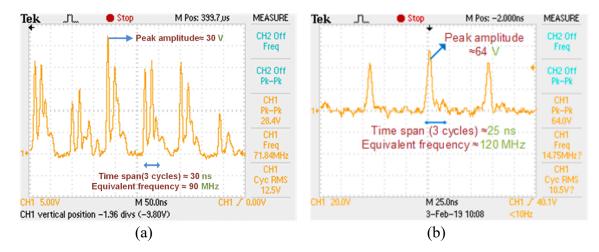

| Fig. 24: Output from (a) 600 V rated Schottky diode based NLTL ( $V_{DD} = 10 \text{ V}$ ) (b) 1200 V       |

|-------------------------------------------------------------------------------------------------------------|

| rated Schottky diode based NLTL ( $V_{DD} = 10 \text{ V}$ )                                                 |

| Fig. 25: Output across (a) $14^{th}$ section of the 1200 V rated Schottky diode based NLTL (V <sub>DD</sub> |

| = 10 V) (b) $14^{\text{th}}$ section of the 1200 V Schottky diode based NLTL (V <sub>DD</sub> = 30 V)49     |

| Fig. 26: Output across the 11 <sup>th</sup> section of the 1200 V rated Schottky diode based NLTL           |

| coupled with UCC21520 based in-house pulse generator ( $V_{HVLINK}$ = 40 V, $V_{DD}$ = 40 V, f = 2          |

| MHz)                                                                                                        |

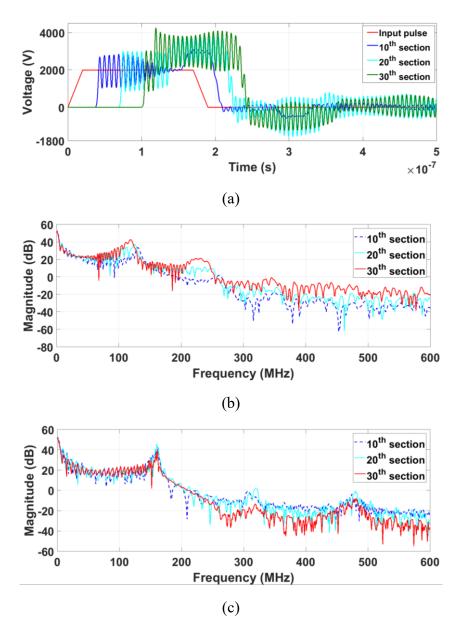

| Fig. 27: Schematic of the 32-section dual-diode NLTL                                                        |

| Fig. 28: (a) Solitons generated at different sections of the dual-diode NLTL (b) FFT of                     |

| solitons generated from single-diode NLTL (c) FFT of solitons generated from dual-diode                     |

| NLTL                                                                                                        |

| Fig. 29: A high-voltage solid-state switch from BEHLKE                                                      |

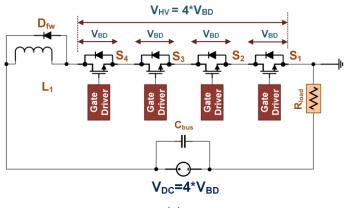

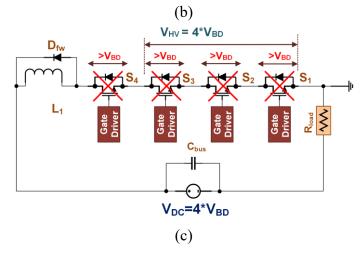

| Fig. 30: Series-connected switch failure mechanism due to voltage imbalance (a) Ideal                       |

| scenario (b) Beginning of the failure (c) Cascaded failure of the entire switch                             |

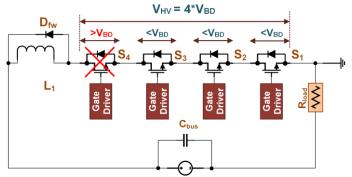

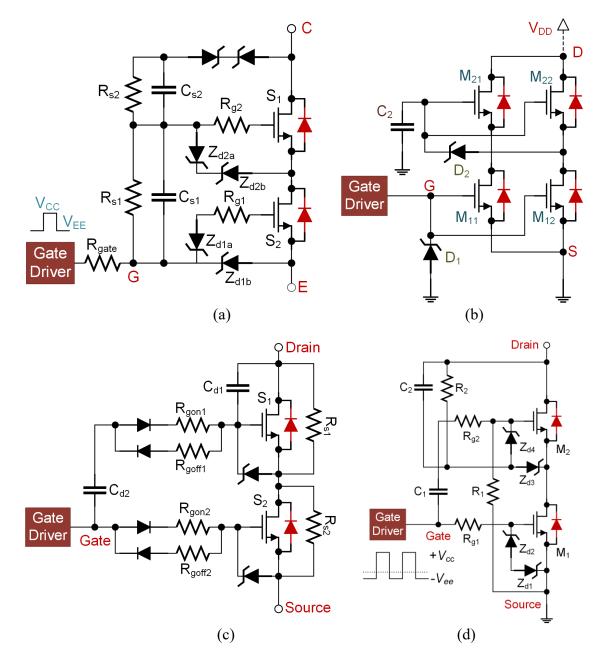

| Fig. 31: Two-stage capacitive coupling based HV switch designs proposed in (a) [103] (b)                    |

| [124] (c) [145] (d) [146]                                                                                   |

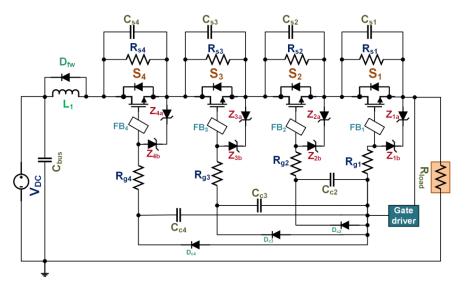

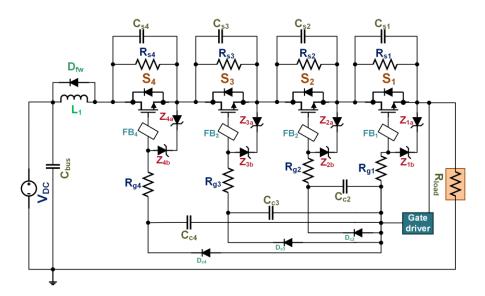

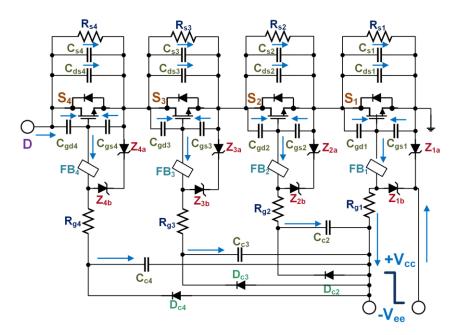

| Fig. 32: Schematic of the four-stage 4.8 kV rated HV switch                                                 |

| Fig. 33: Main current paths during turn-ON transition70                                                     |

| Fig. 34: Main current paths during turn-OFF transition72                                                    |

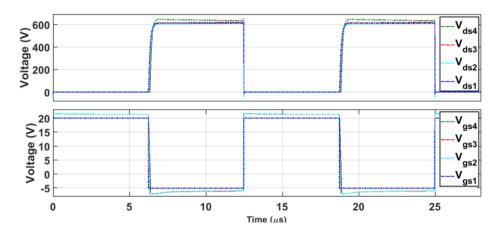

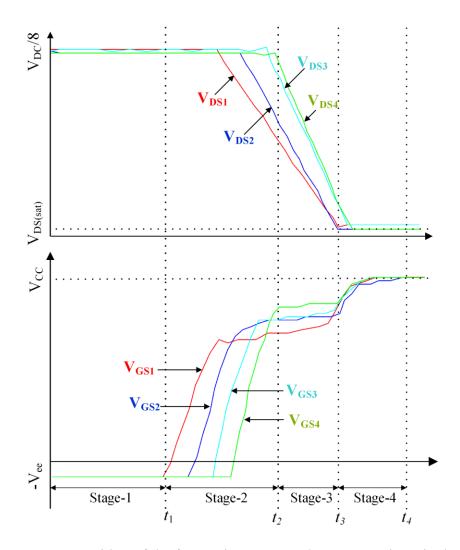

| Fig. 35: Simulated (a) drain-source voltages (b) gate-source voltages across the four                       |

| individual MOSFETs ( $V_{DC} = 2.5 \text{ kV}, f_{sw} = 40 \text{ kHz}, D = 50\%$ )                         |

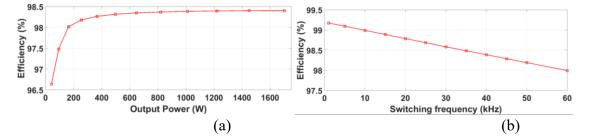

| Fig. 36: Effciency of the HV switch at (a) different power outputs ( $f_{sw}$ =40kHz, $D$ =50%) (b)        |

|------------------------------------------------------------------------------------------------------------|

| different switching frequency (D=50%)                                                                      |

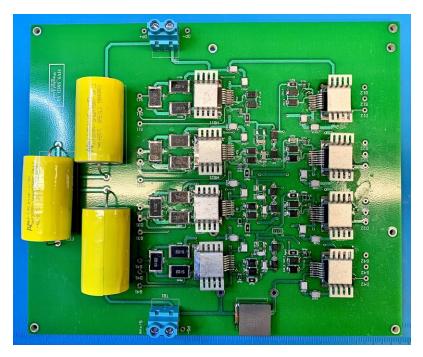

| Fig. 37: The 6.8 kV rated HV switch prototype                                                              |

| Fig. 38: Experimental setup of the HV switch with a 3.2 k $\Omega$ resistive load                          |

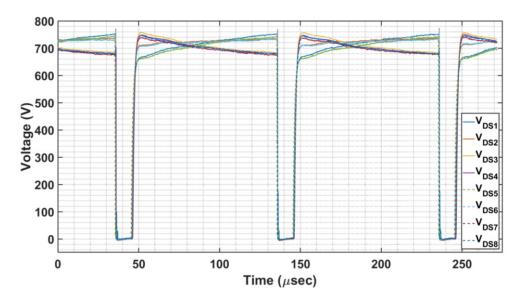

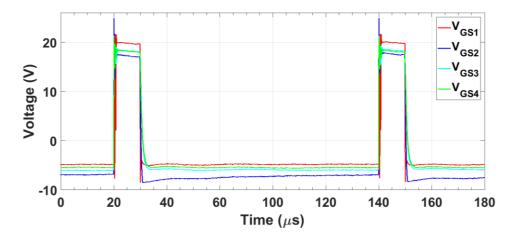

| Fig. 39: (a) Experimental drain-source voltages across the four individual MOSFETs ( $V_{DC}$ =            |

| 2.5 kV) (b) experimental gate-source voltages across the four individual MOSFETs 79                        |

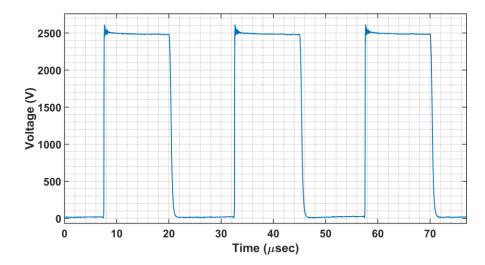

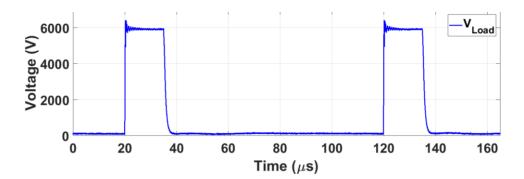

| Fig. 40: Voltage measured across 3.2 k $\Omega$ resistive load at 2.5 kV ( $f_{sw}$ =40 kHz, $D$ =50%) 80  |

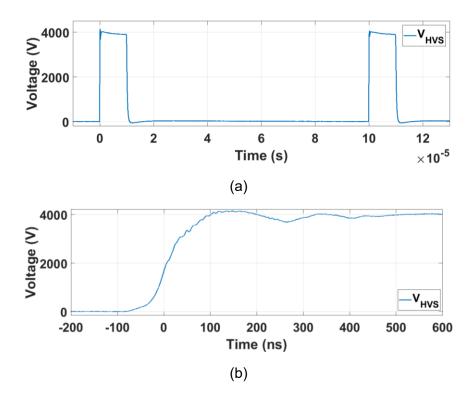

| Fig. 41: (a) Voltage measured across 3.2 k $\Omega$ resistive load at 4 kV ( $f_{sw}$ =10 kHz) (b) zoomed- |

| in version of the load voltage during turn-on transient                                                    |

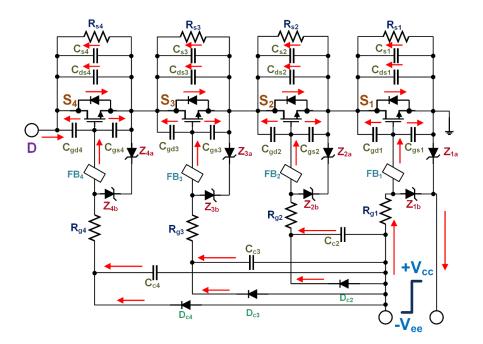

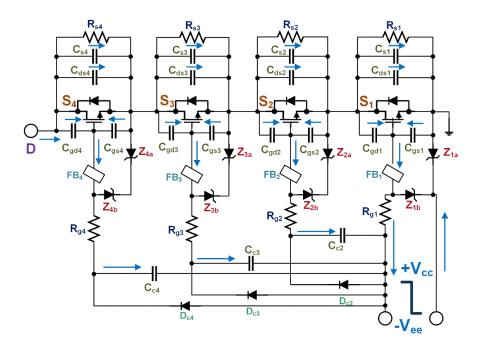

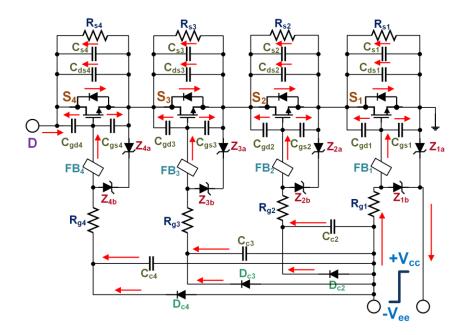

| Fig. 42: Schematic of the proposed modular HV switch                                                       |

| Fig. 43: Detailed schematic of a single module of the modular HV switch                                    |

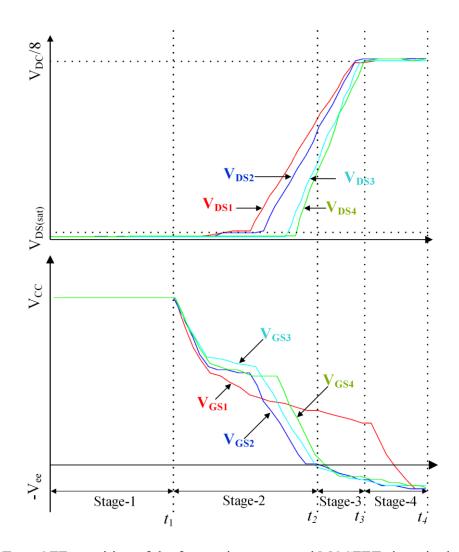

| Fig. 44: Turn-ON transition of the four series-connected MOSFETs in a single module of the                 |

| proposed HV switch                                                                                         |

| Fig. 45: Main current paths in a single module during turn-ON transition                                   |

| Fig. 46: Turn-OFF transition of the four series-connected MOSFETs in a single module of                    |

| the proposed HV switch                                                                                     |

| Fig. 47: Main current paths in a single module during turn-OFF transition                                  |

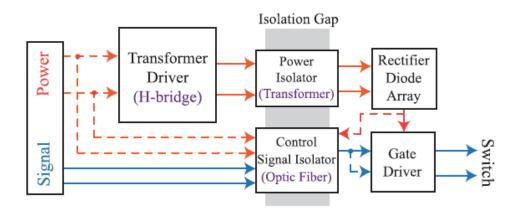

| Fig. 48: Basic schematic of an isolated gate driver circuit. Power isolation stage and control             |

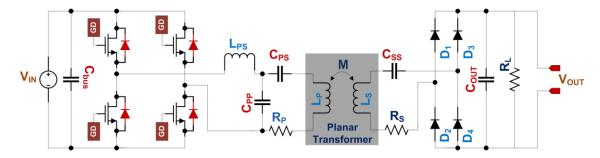

| signal isolation stage are incorporated in the gate driver [149]                                           |

| Fig. 49: Schematic of the resonant converter-based DC-DC converter for the isolated gate                   |

| driver                                                                                                     |

| Fig. 50: Custom isolation transformers for the isolated gate driver                                        |

| Fig. 51: Prototype of the custom isolation transformer based isolated gate driver 104                    |

|----------------------------------------------------------------------------------------------------------|

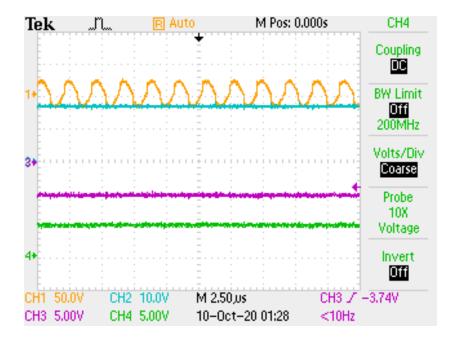

| Fig. 52: Voltage waveforms (yellow-transformer primary side voltage, cyan- 20V bus, green-               |

| +5V bus, purple5V bus)                                                                                   |

| Fig. 53: Schematic of a single module of the proposed gate driver                                        |

| Fig. 54: Fabricated prototype of the in-house modular HV (10 kV rated) gate driver 109                   |

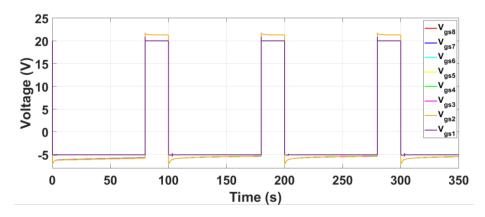

| Fig. 55: Identical gate drive signals originated from the modular gate driver 109                        |

| Fig. 56: Simulated drain-source voltages across the eight individual MOSFETs ( $V_{DC} = 6 \text{ kV}$ , |

| $f_{\rm sw} = 20 \text{ kHz}$ )                                                                          |

| Fig. 57: Simulated gate-source voltages across the eight individual MOSFETs ( $V_{DC} = 6 \text{ kV}$ ,  |

| $f_{\rm sw} = 20 \text{ kHz}$ )                                                                          |

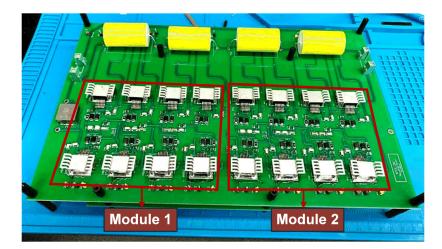

| Fig. 58: Fabricated prototype of the proposed HV modular switch 114                                      |

| Fig. 59: Integrated prototype of the HV switch with the HV isolated gate driver 114                      |

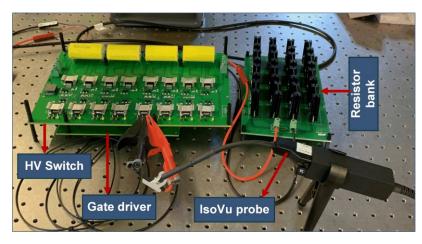

| Fig. 60: Experimental setup including the HV switch, the HV isolated gate driver and the                 |

| resistor bank                                                                                            |

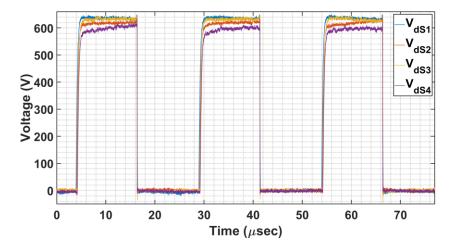

| Fig. 61: Experimental drain-source voltages measured across the individual MOSFETs in a                  |

| single module ( $V_{DC}$ = 5 kV)                                                                         |

| Fig. 62: Voltage measured across the 9.6 k $\Omega$ resistive load ( $V_{DC}$ = 6 kV) to test the 10 kV  |

| switch                                                                                                   |

| Fig. 63: Experimental drain-source voltages measured across the individual MOSFETs in the                |

| entire HV switch ( $V_{DC}$ = 5 kV)                                                                      |

| Fig. 64: Experimental gate-source voltages measured across the individual MOSFETs in a                   |

| single module ( $V_{DC}$ = 6 kV)                                                                         |

#### ACKNOWLEDGEMENTS

This research work was partially supported by the Office of Naval Research under award no. N00014-17-1-3016, and University of Missouri-Kansas City (UMKC).

I would first like to express my sincere gratitude to my committee chair and supervisor Dr. Faisal Khan who has been instrumental in honing my critical thinking ability and improving my engineering intuition over the course of my Ph.D. journey. I wholeheartedly believe, each conversation I have had with Dr. Khan during my time at Missouri Center for Advanced Power (MCAP) has contributed to my growth as a researcher and a person. His outstanding ability to meticulously dissect an engineering problem and come up with ingenious solutions has instilled a sense of fortitude in me to embrace any engineering problem and come up with solutions. Dr. Khan has motivated me to continuously work on my skill as an independent researcher which has tremendously helped me to navigate through a lot of technical challenges. I could not have wished for a better supervisor and mentor for my Ph.D. study. I will treasure the wisdom I have gathered by picking his brain during my Ph.D. journey and will try my best to put them to use moving forward.

Apart from my Ph.D. supervisor, I am indebted to the rest of my Ph.D. committee members, Dr. Majid Bani-Yaghoub, Dr. Ahmed Hassan, Dr. Anthony Caruso, and Dr. Masud Chowdhury for their invaluable suggestion, feedback, and interdisciplinary expertise throughout my degree. I would like to acknowledge and appreciate the magnificent opportunity extended by Dr. Caruso to collaborate with fellow researchers from multiple disciplines to work on cutting-edge technologies at the Missouri Institute of Defense and Energy (MIDE). This interdisciplinary collaboration has granted me a unique opportunity to enhance my skills related to teamwork and project management.

I would like to thank my fellow lab mates Sourov Roy and Abu Hanif for the enlightening discussions and fun activities we have had that used to give me a breather when I needed it most. I am thankful to be a part of a lab where the positivity of all the lab members acted as a conduit of stimulating ideas.

Finally, I would like to express my earnest gratitude to my parents who were my biggest cheerleaders throughout my Ph.D. journey. Their unconditional love and inspiration have galvanized me to stay my course under all circumstances. I would also like to thank my elder sister Saima for supporting me during my Ph.D. years. My beloved wife, Farhana Taher Sumya, has always been there for me through thick and thin. She has sacrificed a lot to see me succeed in my Ph.D. journey and helped me to be a better version of myself in every facet of life. I am indebted to her for all the contributions she has made to make my journey towards Ph.D. degree a smooth one.

# DEDICATION

To my parents, Abul Kalam Azad and Shefali Begum, and my wife, Farhana Taher Sumya for their unconditional love and sacrifice have made me who I am today.

#### CHAPTER 1

## INTRODUCTION

# **1.1 Motivation**

Pulsed power technology alludes to the technique that entails accumulating charge over a relatively long period ( $\mu$ s-min) and releasing that charge within a short period (ps- $\mu$ s), thereby delivering a tremendous amount of power to the output load.

The origin of the pulsed power technology can be traced back to the 1960s when J.C. Martin and his colleagues of the British Atomic Energy Research Center (AI) combined a Blumlein line with a previously developed Marx generator to compress the width of an input pulse from microseconds to a few tens of nanoseconds [1]. During that era, the capabilities of the pulsed power sources were primarily leveraged in gigantic systems such as particle accelerators, fusion research, laser system, electromagnetic launchers, etc [2]-[7]. During its early age, the growth and development of pulsed power technology were primarily governed by the military or nuclear requirements, rendering it more of a specialized branch of research. United States, China, former Soviet Union, Japan, and many advanced countries in Europe were the pioneers in establishing pulsed power facilities leading to the development of pulsed power sources. For instance, AHrapa-5 was the first pulsed power source made in the Soviet Union in 1985 using a combination of Marx-Blumlein technologies with spectacular parameters of 2 MV, 40 MA, 90 ns. United States soon followed suit by developing its pulsed power source in the form of the PBFA-II (12MV, 8.4ma, 40ns) developed by Sandia laboratories in 1986 [8]. For historical and political reasons, Japan refrained from developing pulsed power sources for military purposes. Instead, pulsed power devices such as Etigo-II

were developed at the Nagaoka University of Technology in 1986 with a peak voltage of 3 MV, a peak current of 400 kA, and a pulse width of 60 ns for inertial confinement fusion research [9].

Over the last few decades, considerable development has taken place in the field of pulsed power technology embellishing this technology with promising features tailored for a wide range of applications with diverse backgrounds, biomedical, industry, environment, to name a few. Pulsed power sources are being used in environmental spaces, for instance, pulsed corona, and other ion purification methods of waste gas technology, high-pressure pulse discharge wastewater outlet, pulse electrostatic dust removal, microbial sterilization, and disinfection, production of ozone, etc [10]–[12]. In the biomedical field, pulsed power sources have been successfully employed to offer a potential non-intrusive treatment mechanism for cancer, malignant tumor, etc. Programmed cell death (apoptosis), electroporation are among some of the premeditated clinical phenomena induced by the application of pulsed power sources [13], [14]. Pulsed power sources have penetrated several other fields including but not limited to geophysical and underwater target detection, rock drilling, high-speed X-ray underwater photography, and rapid heating and quenching, etc [15], [16].

In light of the ever-increasing demand for pulsed power sources in a diverse array of applications, the research interest in this field has also heightened manyfold. In keeping with the widening application space of pulsed power, the importance of flexibility in the parameter space of the high-power pulses is growing. Long gone the days when a single long pulse with high peak power was primarily asked of a pulsed power source. Nowadays, frequency agility, waveform shape variation, high repetition frequency, compactness are some of the advanced characteristics that end users yearn for from pulsed power sources. For example, the rise time of the output pulse waveform governs the efficacy of the pulsed power system in some of the applications where the impact of the pulse rise time is pronounced. Majority of the industrial applications that employ pulsed power sources as a key enabler require pulsing at a high repetition frequency. Therefore, researchers have delved deep into this field to devise unique schemes to meet the versatile demand stemming from a wide range of applications resulting in a number of pulsed power techniques, including pulse forming lines (PFLs), Marx generator, nonlinear transmission lines (NLTLs), semiconductor opening switch-based pulser, highvoltage switch-based pulser, etc.

The majority of the aforementioned pulsed power sources typically include a DC power supply, an energy storage unit, a pulse forming line, a switching device, and an output load. The simplest form of operation entails charging the energy storage unit up to the level of supply voltage over a relatively long period. The sored energy is then modulated into a pulse with a shorter width in the quasi-square or exponentially decayed wave shape. The output pulse waveform and repetition frequency are heavily influenced by the switching devices of these pulsed power sources. Unlike other methods of producing high-power pulse, NLTLs do not require a switching device to modulate an input pulse into a pulse with higher peak power with reduced rise time. On top of that, the constituting dielectric or magnetic material of an NLTL governs the center frequency of the output RF pulses and this frequency can be adjusted by changing the length of the NLTL as well. This frequency agility coupled with the absence of switching devices makes NLTL an intriguing pulsed power source. That being said, an NLTL can only generate a finite number of RF pulses from a single input pulse, therefore requiring a continuous supply of input pulse stream to produce continuous output. Conversely, the HV switching devices are indispensable parts of the other pulsed power sources. Conventional switching devices used in these pulsed power sources typically come in the form of spark gap, vacuum tube, thyratron, etc. These magnetic and gas-based switches have high voltage withstanding capability and high current carrying capability that set them apart from other competing switches. However, these switches are plagued by high jitter, short life span, low operational frequency, etc. To make it worse, these switches are bulky and expensive as well, thereby compromising their compatibility in a high-speed application that emphasizes the portability and compactness of the overall pulsed power source as well.

Recent ongoing development in the fabrication process of semiconductor devices, especially wide bandgap (WBG) devices, have ushered in a new wave of fast, low-jitter, and reliable semiconductor switches (e.g., MOSFETs, IGBTs, etc.). These switches have paved the way for a new generation of pulsed power sources that are capable of switching at a higher rate with low jitter and extended lifetime. That being said, commercial solid-state semiconductor switches still trail the traditional magnetic and gas-based switches in terms of sheer voltage withstanding and current-carrying capability. To retain the high-speed advantage offered by the solid-state semiconductor switches while hitting the required voltage and current levels in pulsed power applications, researchers have come up with a technique where multiple semiconductor switches can be connected in series and parallel to increase the voltage withstanding ability and current-carrying capability. One of the most intriguing methods to accomplish this objective is the capacitive coupling method which entails driving seriesconnected switches using coupling capacitors, and a single gate driver is used for the entire stack of the series-connected switches. The tangible advantages offered by the capacitive coupling method notwithstanding, experimental validation of the functionality of this method for multiple stages in terms of voltage balancing during steady-state and switching transients is lacking from the literature.

#### **1.2 Research Objective**

In this research, the lack of a working high-voltage switch prototype based on the capacitive coupling method has been addressed. A four-stage high-voltage switch using the capacitive coupling method based on SiC MOSFETs (WBG MOSFET) has been proposed and developed. The developed prototype has showcased excellent voltage balancing property during both steady-state and switching transients. Taking the capacitive coupling-based HV switch design one step further, modularity has been introduced in the HV switch design. This unique feature allows customization of the HV switch in terms of voltage rating by connecting multiple modules in series eliminating the need for a complete design overhaul. As the voltage rating of the modular custom HV switch is increased, a new design challenge springs in terms of the isolation rating of the gate driver. Commercial gate drivers with a high isolation rating (>5.7 kV) are not readily available till now. Therefore, a custom gate driver with sufficient isolation is needed to be designed to drive the modular HV switch. Within the scope of this research, a 10 kV rated isolated gate driver has been designed to drive a 10 kV rated modular HV switch.

As a pulsed power source, an NLTL separates itself from the rest of the class thanks to the absence of switching devices. However, the limited availability of nonlinear components in commercial space, and the requirement of continuous input supply, hinder the growth of this pulsed power source in pulsed power applications. In this research, a novel design involving an NLTL, a power amplifier, and RF matching networks has been proposed that is capable of generating a continuous stream of solitons from a single input pulse. This unique feature can pave the way for the portability of the NLTL based pulsed power source.

#### **1.3 Dissertation Outline**

This dissertation is organized into eight (8) chapters. Chapter 2 gives a brief overview of the existing pulsed power techniques underscoring the relative advantages and disadvantages pertaining to each technique. Chapter 3 explains the broad categories of NLTLs as well as the fundamentals of soliton generation in a lumped element NLTL to set the stage for what comes in the next chapter. The detailed design procedure of a self-sustaining soliton generator is outlined in Chapter 4. The major components of the proposed self-sustaining soliton generator are discussed at length and simulation and experimental results are presented validating the proposed concept. Chapter 5 highlights the present need for a high-voltage solidstate switch in the field of pulsed power and challenges associated with the development of a high-voltage solid-state switch. Potential solutions to overcome the development challenges of HV switch are also elaborately discussed. Chapter 7 presents the design details of a seriesconnected four-stage HV SiC switch based on the capacitive coupling method along with ample simulation and experimental results. Chapter 8 highlights the introduction of modularity in the series-connected HV switch topology. The operating principle of the switch is articulated in detail in this chapter. The design concept is validated by simulation and experimental results and documented in this chapter. Finally, conclusions and future works are discussed in Chapter 8.

#### **CHAPTER 2**

## LITERATURE REVIEW OF PULSED POWER TECHNOLOGIES

### 2.1 High-Voltage Switch Based Pulser

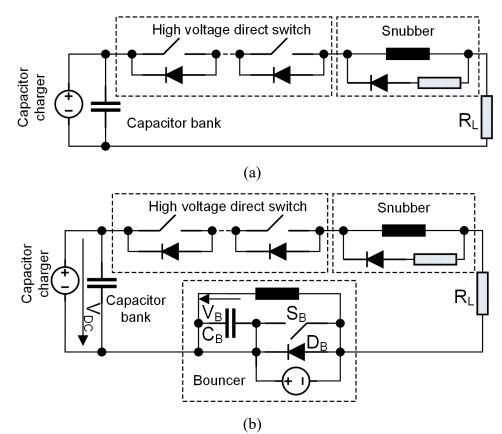

A high-voltage (HV) switch-based pulser represents one of the simplest ways to generate high voltage pulses. The basic configuration of an HV switch-based pulser includes a HV DC power supply, a capacitor bank to store charge, and a stack of switches to form a HV switch as shown in Fig. 1(a) [17], [18]. The primary design consideration in this approach is to ensure that the HV switch is able to withstand the entire DC supply voltage during the turn-OFF period. Spark gap switches are traditionally furnished with high voltage withstanding capability and high current carrying capabilities. However, limited lifetime and incompatibility with higher repetition frequency have driven the researchers towards solid-state switches (e.g., MOSFETs, IGBTs, etc.) that are capable of switching at a much faster rate as opposed to the spark gap switches. The tradeoff lies in the fact that these solid-state switches have limited capabilities with regards to voltage withstanding and current carrying. Therefore, an array of switches configured in series and parallel connections is required to satisfy the high-voltage and high-current requirements of pulsed power applications. The configuration shown in Fig. 1(a) includes a snubber circuit as well to limit the current in the case of an arcing phenomenon and facilitate abrupt interruption of circuit operation to avoid a destructive accumulation of arc energy. During high-power consumption, the output voltage across the load might experience considerable droop. A mitigation scheme is illustrated in Fig. 1(b) entailing a bouncer capacitor  $C_{\rm B}$ , and an inductor forming a resonant circuit and termed as L-C bouncer [19]. The bouncer circuit is activated before the HV switch is triggered to compensate for the droop.

Fig. 1: Direct HV switch based pulser topology (b) Direct HV switch topology with active droop compensation, snubber circuit and voltage signals at different points of interest [17], [18]

The primary advantage of this pulse modulator topology is its simple construction, scalability that helps to discard pulse transformer from the design, thereby attaining a smaller footprint. That being said, series-connection of multiple switches requires a special scheme for voltage balancing during OFF state and during switching transitions which renders the approach sophisticated in case of very high voltage levels. On top of that, the capacitor charger, capacitor bank, and the HV switch is needed to be isolated from the output and therefore submerged in oil to reduce the modulator size.

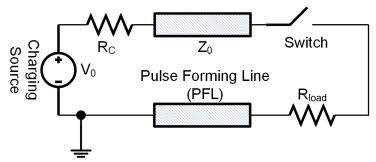

## 2.2 Pulse Forming Line

A lot of pulsed power applications have exclusive requirements of short flat-top pulses with high peak power. One of the simplest yet most effective ways to generate short flat-top rectangular or square pulse at an extremely high-power level for numerous pulsed power applications is using pulse forming lines (PFLs) or their pulse forming network (PFN) analogs [20]–[24]. There exists a number of variants of pulse forming lines to cater to a variety of applications. The simplest form of PFL can be fabricated using a transmission line, a fast switch, and a DC supply [25]. This configuration can be coined as a single pulse forming line alluding to the use of a single transmission line in the configuration. The basic schematic of a single pulse forming line is shown in Fig. 2 [26].

Fig. 2: Basic configuration of a single pulse forming line [26]

The transmission line is charged to the supply voltage level through a resistor with high impedance to minimize the level of the charging current to avoid overloading the DC power supply and/or to safeguard the switch from excessive current. The impedance of the charging resistor is required to be substantially larger than the characteristic impedance of the transmission line to ensure proper formation of the output voltage across the load. Once the transmission line is charged, the switch is closed, and the transmission line is discharged through the switch across the load. A rectangular-shaped output pulse is formed across the load

with a width twice the transit time that a voltage step would require to traverse the line from one end to the other end. If the load impedance is matched to the characteristic impedance of the transmission line, the theoretical value of the peak amplitude of the output pulse would be half of the peak amplitude of the input pulse. Coaxial cables or parallel-plate-type microstrip lines can be used as the transmission line depending on the impedance of the output load. Coaxial cables are typically manufactured with a fixed set of impedances (e.g.,  $50\Omega$ ,  $75\Omega$ , etc.), thereby suitable for use with output loads with similar values. However, for a diverse range of output impedances, parallel-plate transmission lines are more suitable as they can be fabricated to attain a dynamic range of impedances.

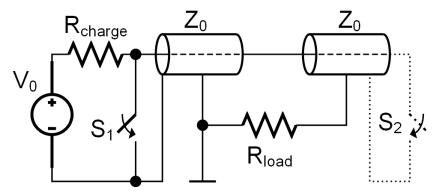

One of the major drawbacks associated with the single pulse forming line is that the maximum attainable output voltage is half of the input voltage provided by a DC power supply. At an extremely high power level requiring high peak voltages, the aforementioned issue can mount a serious practical challenge in terms of the availability of an extremely high-voltage power supply. Blumlein pulse forming line, invented by A. D. Blumlein offers a potential solution to this problem. The output voltage that can be obtained using the Blumlein line is equal to the input voltage if the impedance of the output load is twice the characteristic impedance of the transmission line. A basic Blumlein line can be constructed using two transmission lines of equal length and a closing switch as shown in Fig. 3 [24]. However, the width of the output pulse can only be varied by changing the length of the transmission line, or for PFNs, changing constituting components. This physical constraint makes it difficult to tune the parameter of the output pulse required by different applications. On top of that, the nonzero ON-resistance of the closing switch contributes to considerable distortion in the output

pulse. These aforementioned problems pertaining to the basic Blumlein line configuration can be mitigated using two independently controllable closing switches at either end of the transmission lines as shown by the dotted line in Fig. 3 [24]. This assembly allows for a modification of pulse polarity, pulse width without changing the physical dimensions of the transmission lines.

Fig. 3: Schematic of a basic Blumlein line configuration with one closing switch (solid line), and a modification involving a second closing switch at the end of the pulse forming line (dotted line) [24]

## 2.3 Nonlinear Transmission Lines

The width of a pulse generated from a single pulse forming line is typically proportionally related to the length of the transmission line. Coaxial cables and stripline type pulse forming lines are most commonly used to fabricate transmission lines pertaining to a pulse forming line. Coaxial cables, however, are manufactured with a limited number of impedance values (e.g.,  $50\Omega$ ,  $75\Omega$ , etc.), thereby rendering them incompatible in many pulsed power applications where output loads assume a wide range of impedance values. Fabrication of striplines can be customized to assume a wide range of impedance values. That being said, the dielectric constants of the dielectric materials (e.g., polymer plastic such as polypropylene) that are typically used to isolate the two constituting conductors of the stripline tend to be on the lower side ( $\varepsilon_r = 2-3$ ) [25]. The wave propagation velocity ( $v_p$ ) through a stripline is related to the relative permittivity ( $\varepsilon_r$ ) of the dielectric material through the following equation.

$$v_p = \frac{c}{\sqrt{\varepsilon_r}} \tag{1}$$

Where c represents the velocity of light and  $\varepsilon_r$  represents the relative permittivity of the dielectric constant of the insulating material of the stripline. To produce a pulse having a width in the range of microseconds using stripline, long transmission lines are required which may be impractical in many cases. An alternative method tailored for pulsed power applications is using pulse-forming networks. Pulse forming networks features ladder networks constructed from inductors and capacitors. One of the prominent pulse forming networks used for generating high-power pulses is the nonlinear transmission line (NLTL). NLTLs have been successfully put into use in pulsed power applications over the last few decades thanks to their unique offerings in the form of frequency-agility, relatively high power, etc. The key contributing component in an NLTL is the nonlinear material either in the form of nonlinear dielectric material or magnetic material. This nonlinear material is periodically arranged in an NLTL, leading to pulse sharpening and/or a stream of high-frequency oscillation in the RF or microwave regime, known as solitons. The nonlinearity sharpens the input pulse and the dispersion pertaining to an NLTL leads to the breakup of the input pulse into a stream of highfrequency oscillations. A combination of nonlinear capacitors and nonlinear inductors can be used to fabricate an NLTL. Lumped element NLTL and gyromagnetic NLTLs are the two major NLTL types suitable for high power RF signal generation. Gyromagnetic transmission lines have demonstrated their capability of generating RF signals in the GHz range [27]. On top of that, as a compact RF source, NLTLs have showcased their capability to operate at a

repetition frequency greater than 1 kHz [28], [29]. That being said, sourcing a diverse array of materials with nonlinear dielectric or magnetic characteristics has been a field of interest for researchers.

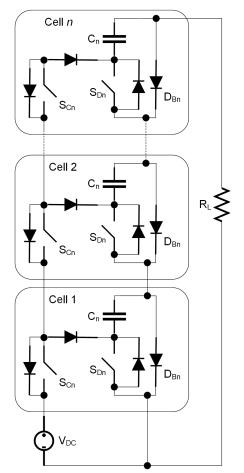

## 2.4 Marx Generator

Marx generator is a kind of pulsed power modulator that relies on the charging of the capacitors in parallel and discharging in series into a load to obtain a high-voltage, high peakpower pulse. It is one of the most widely studied and used power modulator schemes thanks to its modularity and ease of design [30]–[37]. The Marx generator extends its versatility in the fields of high power systems such as kicker magnets [38], a critical component in particle accelerators; in plasm generation and control [39], and the medical field for tissue welding and cancer treatment [14]. Traditionally, spark gap switches have been used extensively in Marx generators to produce high-power pulses due to their high-voltage withstanding ability and high current carrying capability. That being said, compatibility issue at high repetition rate has inspired researchers to replace the bulky spark gap switches with more potent alternatives. With the recent advancement in semiconductor switch technologies, the spark gap switches are being replaced by all-solid-state semiconductor switches enabling a higher repetition rate and more compact footprint of the new-generation Marx generators. In an ideal Marx generator, the *n* number of capacitors are charged in parallel to produce a high-voltage pulse with a peak magnitude of  $nV_{DC}$ , where  $V_{DC}$  is the input voltage magnitude and n is the number of stages in a Marx generator circuit configuration as showcased in Fig. 4 [40].

Fig. 4: Modular solid-state Marx modulator schematic [40]

A single module of a Marx generator consists of a charging switch  $S_{\rm C}$ , a capacitor C, a discharging switch  $S_{\rm D}$ , bypass diode  $D_{\rm B}$ , and high-voltage switches, typically implemented using MOSFETs or IGBTs. During the charging phase, charging switches ( $S_{\rm C1}$ ---- $S_{\rm Cn}$ ) are triggered, thereby charging the capacitors ( $C_1$ ,  $C_2$ ---- $C_n$ ) in parallel to a voltage level equaling to the level of the input voltage  $V_{\rm DC}$  through the bypass diodes. The high-voltage output is delivered to the load during the discharging period. During this period, the charging switches ( $S_{\rm C1}$ ---- $S_{\rm Cn}$ ) remain turned-OFF, and the switches denoted by  $S_{\rm D1}$ --- $S_{\rm Dn}$  are triggered ON, thereby connecting the capacitors in series and discharging the high-voltage across the load. The charging switches can be replaced by high-valued resistors to fulfill the requirements including but not limited to reduced complexity, more compact footprint, reduced cost, shorter pulse length [32]. However, owing to the large values of the charging resistors, the charging and the discharging paths remain decoupled from each other.

The advantage of the Marx generator is underscored by the ease of output voltage scalability by adding more modules, and the requirement of providing galvanic isolation up to the charging voltage level ( $V_{DC}$ ). However, the output voltage level does not linearly scale up keeping in line with the increasing number of stages.

## 2.5 Pulse Transformer

Pulse modulators based on solid-state technology offer superior performance compared to the traditional spark-gap switch-based modulators in terms of switching frequency, lifetime, etc. That being said, solid-state technologies still lag behind the spark-gap switches from voltage withstanding ability and current-carrying capability standpoint. Pulse transformers are often combined with the solid-state switch-based pulse modulators to overcome this issue by facilitating the required voltage or current step up by virtue of flexible turns ratio [41]–[43]. The introduction of pulse transformers in a pulse modulator simplifies the design of the pulse modulator itself as a result of the lessened requirement of series or parallel connected switches to meet the application requirement. However, in practical pulsed power applications, such as radar systems, particle accelerators, and klystron modulators, a flat top pulse is required. Parasitic parameters (e.g., leakage inductance, distributed capacitance, etc.) pertaining to the pulse transformers influence the output pulse shape obtained from the pulse transformer to a great extent. Some crucial output pulse parameters such as rise time, overshoot, voltage droop are significantly impacted by the parasitic parameters of the pulse transformers [42], [44]–[46]. Therefore, the meticulous design of pulsed transformers is of paramount importance to exert control over the parasitic parameters of the pulse transformers. Pulsed transformers are combined with pulse modulators in a number of ways as showcased in Fig. 5 [43].

The pulse transformer can be incorporated in a direct switch-based pulser as shown in Fig. 5(a). It can be coupled with a Marx generator circuit as well as illustrated in Fig. 5(b). The pulse transformer works in tandem with the direct-switch-based pulser and the Marx generator to reduce the number of solid-state switches connected in series and number of stages respectively. The addition of a pulse transformer also facilitates the use of a low-voltage input DC supply. To meet the requirement of higher output pulsed power, multiple switches can be connected in parallel at the input side of the pulse transformer as illustrated in Fig. 5(c). However, a current balancing scheme for the parallel connected switches is required in this scheme. An alternative approach to mitigate this issue can be splitting the single transformer into multiple transformers with a reduced turns ratio with the secondary windings connected in series as shown in Fig. 5(d).

Pulse transformers are associated with some level of leakage inductance depending on the quality of the design and geometric configuration. Leakage inductance adversely impacts the rise time ( $t_{rise}$ ) of the output pulse as stated in the following equation.

$$t_{rise} \sim \sqrt{L_{\sigma} C_d} \tag{2}$$

Where  $C_d$  is the stray capacitance of the pulse transformer. The total leakage inductance associated with the configuration shown in Fig. 5(d) reduces as the number of split

Fig. 5: Hybrid pulse transformer topologies: (a) Direct series HV switch + pulse transformer, (b) Marx generator + pulse transformer. (c) Direct parallel HV-switch + pulse transformer (d) Series connection of four single pulse transformers with the same output behavior as in (c). (e) Matrix transformer solution with the same output behavior as in (c) and (d), which results in lower transformer parasitic than in (c) and (d) [43]

transformers increases, and the total stray capacitance increases as this number increases. Fig. 5(e) showcases a matrix transformer that consists of four cores, enclosed by the secondary winding. The flux coupled to the secondary winding is the sum of the fluxes in the primary windings, thereby turns ratio is the same as the configuration shown in Fig. 5(d). The biggest advantage offered by this configuration is the reduction of leakage inductance and a smaller footprint.

Pulse transformer-based modulators typically occupy a significant amount of space, limiting their practical use in applications requiring portable and compact solutions. On top of that, the introduction of a pulse transformer in a Marx generator topology or a HV switchbased topology negates the advantage offered by the modularity of these topologies.

#### CHAPTER 3

## FUNDAMENTALS OF NONLINEAR TRANSMISSION LINES (NLTLS) AND SOLITON GENERATION USING NLTL

Nonlinear transmission lines (NLTLs) are a class of pulse forming networks (PFN) for modulation of pulsed power to generate radiofrequency (RF) signals. Primarily, NLTL designs assume a two-port configuration, which requires one-to-tens of nanosecond input pulse rise time for each modulated pulse out. NLTL designs exploit the nonlinearity of the permittivity, and/or permeability to transform an input pulse into a shockwave or a series of oscillations with decaying amplitudes, known as solitons. The origin of these oscillations can be traced back to the precession of magnetic moments for nonlinear magnetic materials or the translations of the dipole in the crystalline structure for nonlinear dielectric materials. NLTLs are capable of operating at a repetition frequency greater than tens of kHz and capable of delivering high peak power in the range of MW, thereby rendering them an attractive candidate for high-power RF applications [47], [48]. On top of that, the use of NLTLs in high-power radio-frequency (RF) generation is gaining further momentum as their mode conversion efficiency and enabling components have improved [49]-[52]. NLTL utilization can be extended to applications in pulse compression, satellite communication, radar, electron beam drivers, defensive countermeasures, and battlefield communication disruption [53]-[56]. Robust and compact solid-state switching as the NLTL feed mechanism is, therefore, an enabling sub-technology, which when coupled in a closed-loop or positive feedback system as first described in [57], yields a potential leapfrog.

NLTLs used in high-power RF generator circuits can be classified into two major categories: (1) lumped element transmission lines assembled from a ladder network of identical

L-C sections, where a balance between the dispersion and nonlinearity gives rise to RF pulses; and, (2) gyromagnetic lines built from ferrimagnetic materials (ferrites), where damped precession of magnetic dipoles polarized by an external magnetic field yields RF pulses [58]. In an NLTL-based RF pulse generator, an input pulse can be decomposed into a stream of pulses with a narrower width, and heightened peak power (i.e., sharpening) compared to the input pulse, which propagates along the line while maintaining the shape and velocity throughout the line. This particular form of RF pulse(s) can be represented as a soliton(s). The balancing act between the dispersion and nonlinearity of the NLTL gives rise to the formation of solitons. The dispersion can be attributed to the periodic nature of the line, whereas the nonlinearity originates from the complex permittivity of the solids (e.g., the nonlinearity of ceramic capacitors, varactors, current dependent inductors, etc.).

Researchers have utilized NLTLs to deliver RF power into output loads in the form of solitons. Gyromagnetic lines typically generate RF signals with center frequency ranging from 500-MHz to a few GHz while achieving reported peak power as high as 100-MW [59]–[62]. As opposed to the gyromagnetic lines, lumped lines tend to be more compact with a caveat of generating RF signals with lower peak power and lower center frequency ranging from a few MHz to 1.2 GHz [63]. That being said, the compactness of the lumped NLTLs paves the way for the researchers to devise a portable high-power RF signal generator. Traditionally, NLTL designs assume a two-port configuration that is capable of generating a finite number of soliton bursts from an input pulse. The characteristics (e.g., frequency, peak amplitude, voltage modulation depth (VMD), oscillation count, etc.) of the soliton bursts are governed by at least the width, shape, and rise time of the input pulse, section count of the NLTL, level of

nonlinearity and dispersion of the NLTL. The nonlinearity of the commercial-of-the-shelf components (e.g., Schottky diodes, ceramic capacitors, varactor diodes, saturable inductors, etc.) are largely non-customizable, thereby imposing an upper threshold of frequency, and amplitude related to the solitons generated from the lumped NLTLs. However, by making changes to the configuration of the nonlinear components in the building block of the NLTL, the frequency of the solitons can be increased.

### 3.1 Lumped Element Nonlinear Transmission Lines

Lumped element transmission lines are typically constructed using identical L-C ladder blocks in series. The capacitor, and/or the inductor of a single block can be nonlinear, thereby contributing to the generation of solitons or a shockwave with higher amplitude. The nonlinear components can be either bought off-the-shelf or they can be custom-made. A typical lumped element NLTL can be illustrated as shown in Fig. 6 [64].

Fig. 6: Schematic of a lumped element nonlinear transmission line comprising of nonlinear inductor and nonlinear capacitor [64]

The general form of the wave equation for the NLTL shown in Fig. 6 can be expressed as:

$$\frac{\partial^2 V(x)}{\partial x^2} = (j\omega L(I) + R)(j\omega C(V) + G)V(x)$$

(3)

Where V represents the input voltage, x denotes the position along the line, L(I) represents the nonlinear inductance as a function of current I, C(V) represents the nonlinear capacitance as a function of voltage V and G is the conductance in parallel with C(V).

Numerical techniques, such as the Bulirsch-Stoer or Runge-Kutta methods are some of the well-defined methods to solve the wave equation related to the generated solitons from the NLTL [65]–[67]. It is found out that the Runge-Kutta method is more efficient in solving wave equations for very steep rise time thanks to its simpler step calculation compared to the Bulirsch-Stoer method [66].

A lumped element transmission line can be represented by modeling transmission line capacitance and inductance as functions of voltage and current respectively. The resulting Korteweg-de Vries equations can be numerically solved for a number of NLTL configurations, namely, nonlinear inductors with linear capacitors [68], nonlinear capacitors with linear inductors [69], and hybrid lines composed of nonlinear inductors and nonlinear capacitors [70].

## **3.2 Gyromagnetic Nonlinear Transmission Lines**

Gyromagnetic line alludes to a continuous ferrite-loaded nondispersive line biased by an axial magnetic field. Unlike lumped element NLTLs, the nonlinearity of a gyromagnetic line stems from the variation of the magnetic permeability with respect to current. The frequency of the output RF signal can be tuned by adjusting the external magnetic field bias and the peak voltage of the input pulse [71], [72]. The coaxial line used for a gyromagnetic line can be either azimuthally or axially biased for pulse compression and efficient RF signal generation from magnetic precession respectively. During azimuthal bias, the gyromagnetic

Fig. 7: Precession of magnetic moment *M* in gyromagnetic line [72]

line is biased by a DC current that flows through the inner conductor, and the ferrites encircling the line are saturated in the opposite direction at the application of this bias current. Conversely, as a result of the application of the axial bias, the entire effective field gets twisted as the azimuthal field generated by the current pulse injected onto the line is superimposed on the axial field.

As illustrated in Fig. 7, if the gyromagnetic line is subjected to an axial magnetic field  $H_z$ , upon injection of a current pulse with a magnitude of *I*, the magnetic moment *M* of the ferrites around the line changes their initial alignment along the longitudinal axis after their interaction with the azimuthal bias, leading to the pulse compression phenomenon [72]. The magnetic moment of the ferrite or ferroelectric material (e.g., barium titanate (BT), barium strontium titanate (BST)) stems from the positioning of the atoms in the polycrystalline structure. A high-frequency precession motion of the magnetic moment also initiates as soon as the current starts to propagate through the line leading to high-frequency oscillations with a shape similar to the input pulse, but with a reduced rise time.

#### **3.3** Theory of Soliton Generation in Lumped Element Transmission Line

A lumped element nonlinear transmission line is a ladder network comprising identical sections of shunt capacitors and series inductors [63]. The shunt capacitor, the series inductor, or a combination of both can introduce nonlinearity in a lumped element NLTL. The potential capacitive elements exhibiting nonlinearity include Schottky diodes with nonlinear junction capacitance [73], nonlinear ceramic capacitors [74], and/or nonlinear ceramic dielectric slabs [75]. On the other hand, the potential inductive elements showing nonlinearity include nonlinear ferrite material [68], MEMS resonator [76]. The availability of multiple commercial-off-the-shelf (COTS) components exhibiting nonlinear capacitance has encouraged the design and fabrication of capacitive NLTL, which is one of the fundamental blocks of the proposed self-sustaining RF pulse generator. The voltage dependence of the capacitance C(V) of the nonlinear capacitor is responsible for the nonlinear behavior exhibited by a capacitive transmission line. The propagation velocity ( $\nu_p$ ) of an input pulse traveling across an NLTL is governed by the voltage dependence of the capacitance C(V) of the nonlinear capacitor and can be stated by the following relationship [77].

$$v_{\rm p} = 1/\sqrt{LC(\rm V)} \tag{4}$$

where *L* is the linear inductance, and C(V) is the nonlinear capacitance. The capacitance of a nonlinear capacitor decreases as the voltage applied across it increases, thereby resulting in a faster propagation velocity of the traveling pulse. This phenomenon leads to points closer to the crest of the waveform, attaining faster propagation velocity compared to the rising edge of the waveform, thereby producing a steep shockwave front [57]. However, the ensuing reduction of the rise time of the output pulse is limited by the relaxation characteristics of the dielectric material or dispersive properties of the lumped element transmission line [78]. Consequently, the output pulse propagates with a constant rise time irrespective of the number of sections once the minimum rise time is achieved. The reduction in pulse rise time ( $\Delta$ T) caused by the *L*-*C* ladder sections can be stated by the following relationship [62].

$$\Delta T = t_{\rm ri} - t_{\rm ro} = \delta_1 - \delta_2 = n \left( \sqrt{LC}_{\rm j0} - \sqrt{LC(V_{\rm max})} \right)$$

(5)

where  $t_{ri}$  and  $t_{ro}$  represent the rise times of the input and output pulses respectively, n is the number of identical *L*-*C* sections in the NLTL, *L* is the linear inductance,  $\delta_1$  and  $\delta_2$  are the propagation delay times of the rising edge and peak of the input pulse respectively and  $C_{j0}$  and  $C_{(Vmax)}$  represent the zero-bias capacitance, and the reduced saturated capacitance of the nonlinear capacitor respectively.

The rise time of the output pulse,  $t_{ro}$  can be expressed as  $t_{ro} = (t_{ri} - \Delta T)$ , where  $t_{ri} > \Delta T$ . However, rise time reduction ( $\Delta T$ ) cannot be equal or greater than the rise time of the input pulse ( $t_{ri}$ ) leading to an infinite steepness of the slope of the output pulse. Therefore, the rise time reduction of the output pulse is restricted by the rise time of the input pulse. The minimum rise time of an input pulse is defined by the cutoff frequency of the NLTL, which is an *L*-*C* ladder network that can be viewed as a cascaded low-pass filter arranged in  $\pi$  configuration. As with any other low pass filter, an NLTL has a cutoff frequency which is known as Bragg frequency. The Bragg frequency of an NLTL can be defined as follows [79]:

$$f_{\rm c} = 1/\pi \sqrt{LC(V_{\rm max})} \tag{6}$$

As the propagating pulse cannot be further sharpened by the remaining sections of the nonlinear transmission line, it breaks down into a stream of high-frequency oscillations with a narrow width, known as solitons. The frequency of the oscillation is close to Bragg frequency [25] and the shape of the oscillation remains unaltered throughout the entire propagation path. To that end, equation (X) can be rearranged as follows [78].

$$\Delta T = n (1 - \sqrt{k}) (\sqrt{LC_{j0}}) \approx \pi (\sqrt{LC} (V_{max})) = \pi \sqrt{k} (\sqrt{LC_{j0}})$$

(7)

where  $k = C(v_{max})/C_{jo} < 1$  and known as the nonlinearity factor. Manipulating equation (4), *K* can be isolated and expressed as follows [78].

$$K = \left(\frac{n}{n+\pi}\right)^2 \tag{8}$$

Equation (5) implies that for a large number of sections in the *L*-*C* ladder network  $(n \rightarrow \infty)$ , the nonlinearity factor approaches unity, thereby capacitors with relatively weak nonlinearity can be used to generate solitons. In addition, for a fixed length of a nonlinear transmission line, dispersion tends to decrease with increasing section count [78], thereby the required delicate balance between dispersion and nonlinearity can be established using weak nonlinearity. Renowned mathematicians Diederik Korteweg and Gustav de Vries proposed the mathematical modeling of a discrete soliton wave in 1895 in the form of a third-order nonlinear partial differential equation, known as KDV equation, as follows [80].

$$\frac{\partial u}{\partial t} + 6u\frac{\partial u}{\partial x} + \frac{\partial^3 u}{\partial x^3} = 0$$

(9)

For a waveform with a fixed shape like soliton and traveling at a speed v to the right side of the x-axis (u=f(x-vt)), this equation reduces to an ordinary differential equation (ODE) with a solution as given below [80]:

$$u(x,t) = \frac{v}{2} \operatorname{sech}^{2} \left[ \frac{\sqrt{v}}{2} (x - vt - x_{0}) \right] = a \operatorname{sech}^{2} [b(x - vt - x_{0})]$$

(10)

where v and  $x_0$  denote wave propagation velocity and initial wave position respectively. The constants a and b represent the amplitude and the inverse of the width of the soliton wave as a function of the propagation velocity (v) [80]. Understandably, waves with faster propagation velocity are associated with higher amplitude and shorter width. Therefore, a stream of solitons tends to feature pulses with gradually decreasing amplitudes and greater widths. The pulse sharpening and soliton formation phenomenon are illustrated in Fig. 8.

The voltage modulation depth (VMD) indicates the level of the DC component present in the soliton waveform. It can be defined as the average peak-to-trough voltage of consecutive three pulses starting from the first pulse in a soliton stream [69].

Fig. 8: (a) Pulse compression (b) Soliton formation

$$VMD = \frac{\sum_{j=1}^{3} (V_{\rm pt})_{j}}{3}$$

(11)

where *j* is the cycle number and  $V_{pt}$  is the voltage differential between the peak and trough of a pulse. VMD is taken into consideration to calculate the average RF power that can

be extracted from the generated soliton stream, and the expression of the average power is given by [69].

$$P_{\rm avg} = \frac{\left(\frac{VMD}{2}\right)^2}{R_{\rm L}} \tag{12}$$

where  $R_L$  is the output load and  $P_{avg}$  is the average RF power. The average RF power can be significantly lower than the peak instantaneous power related to solitons due to the underlying DC component and mismatched output load. Therefore, the characteristic impedance of an NLTL governs the selection of the output load or a matching network in between the NLTL and the load is needed to be designed for impedance matching. The characteristic impedance of an NLTL can be expressed as [62]:

$$Z_0 = \sqrt{\frac{L}{C(V)}} \tag{13}$$

#### CHAPTER 4

# DESIGN OF A MEDIUM-POWER, SELF-SUSTAINING CONFIGURABLE SOLITON GENERATION CIRCUIT USING NLTL IN OPEN AND CLOSED LOOP CONFIGURATIONS

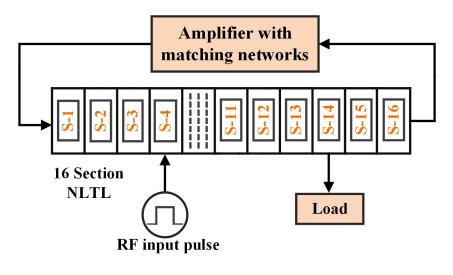

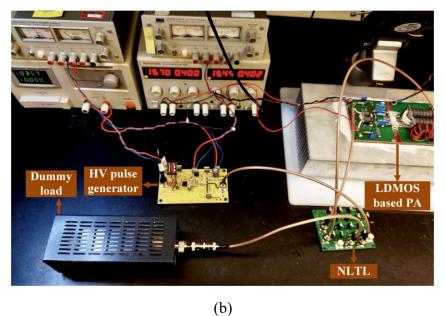

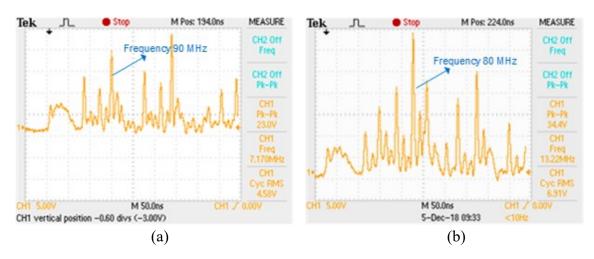

As opposed to the traditional method of generating continuous solitons, using an input pulse stream, a unique switching approach to generate continuous high-power solitons from a single input pulse is proposed and devised in this work. To this end, a Schottky diode-based sixteen-stage NLTL, an LDMOS based power amplifier with matching networks, and a custom GaNFET based high-voltage pulse generator has been combined to produce self-sustaining solitons from a single input pulse. The capability advantage of the closed-loop system is its stability and center frequency tunability; pragmatically, the solid-state-based design of this system enhances its probability of fielded use due to volume and mass savings compared to the prior-art. In [57], the authors have proposed a low-power soliton oscillator, which can amplify ambient noise and produce sustaining low-power solitons. However, the peak amplitude of the generated solitons was limited to 10 V, thereby limiting its practical use in most RF applications. In contrast, the solution demonstrated in this work can be a viable approach to generate self-sustaining solitons for medium-power RF applications in a compact package.

#### 4.1 Design Procedure of the Self-Sustaining Soliton Generator

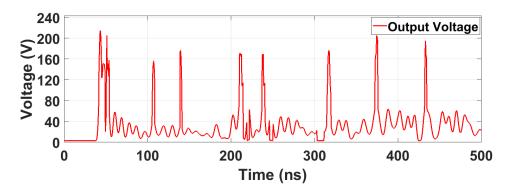

The validity of the design proposed in this work has been empirically shown by a 16section NLTL coupled with a solid-state laterally-diffused metal-oxide-semiconductor (LDMOS) based power amplifier (PA), and a custom HV pulse generator. The closed-loop configuration constructed from these components demonstrated a peak power of 2.1 kW into 50  $\Omega$  at 90 MHz. This is the first report of a solid-state switch-based closed-loop NLTL configuration capable of producing a continuous pulse stream. The key design components of the implemented self-sustaining soliton generator are discussed at length below.

#### 4.1.1 Capacitive NLTL

Nonlinearity in a capacitive NLTL can be introduced by nonlinear components that are predominantly made of ferroelectric dielectric [58]. Several commercially available ceramic capacitors are constructed from ferroelectric materials, thereby exhibiting capacitance nonlinearity when subjected to voltage variation. However, the performance of NLTLs assembled from this type of ceramic capacitors can considerably suffer from dielectric losses of ferroelectric materials. On top of that, the nonlinearity of the ceramic capacitors relies significantly on the Curie temperature of the ferroelectric material. Maximum nonlinearity can be achieved if the operating temperature is in the vicinity of the Curie temperature of the material. To compound the effects of the temperature dependence and dielectric loss of the ceramic capacitor on the performance of an NLTL, aging also has an adverse impact on the capacitance ratio which directly affects the performance of the NLTL [58]. Commercial semiconductor devices (e.g., Schottky diode, varactor, heterostructure barrier varactor, etc.) that exhibit nonlinear junction capacitance under the influence of reverse bias are reported in several studies as the nonlinear component in an NLTL [81]–[84]. The nonlinear junction capacitance is formed at the p-n junction at the depletion region of a diode when subjected to reverse bias voltage. The nonlinearity of the depletion layer junction capacitance can be expressed as follows [83].

$$C(V) = \frac{C_{j0}}{\left(1 + \frac{V}{V_{\rm J}}\right)^n} \tag{14}$$